PIN二极管检测器、制造方法和包括PIN二极管检测器的系统与流程

本公开涉及pin二极管检测器、制造方法和包括pin二极管检测器的系统。

背景技术:

1、pin二极管由n型掺杂区域和p型掺杂区域之间的未掺杂或轻掺杂半导体区域形成。pin二极管可用于检测不同能级的光子。包括pin二极管的光电检测器包括由外围区域包围的检测区域或像素区域。检测区域是光子转换成电信号的地方。外围区域是逻辑器件、密封圈、隔离结构或其它类型的结构所在的地方。光电检测器包括在未掺杂或轻掺杂的衬底中具有不同掺杂剂类型的掺杂阱。掺杂阱外的衬底中的掺杂浓度在整个衬底中基本恒定。

2、在制造过程中,在晶圆上形成各种阱和其它结构。晶圆包含大量分布在晶圆上的器件,例如光电检测器。将晶圆切片,从而将器件彼此分隔开,以便将器件并入集成电路或系统中。在一些实例中,切片过程使用切开衬底以便将器件彼此分隔开的锯子。这种切片过程会在衬底的晶体结构中引入缺陷。一旦器件被集成到集成电路或系统中,这些缺陷就会提供电流泄漏的途径。

技术实现思路

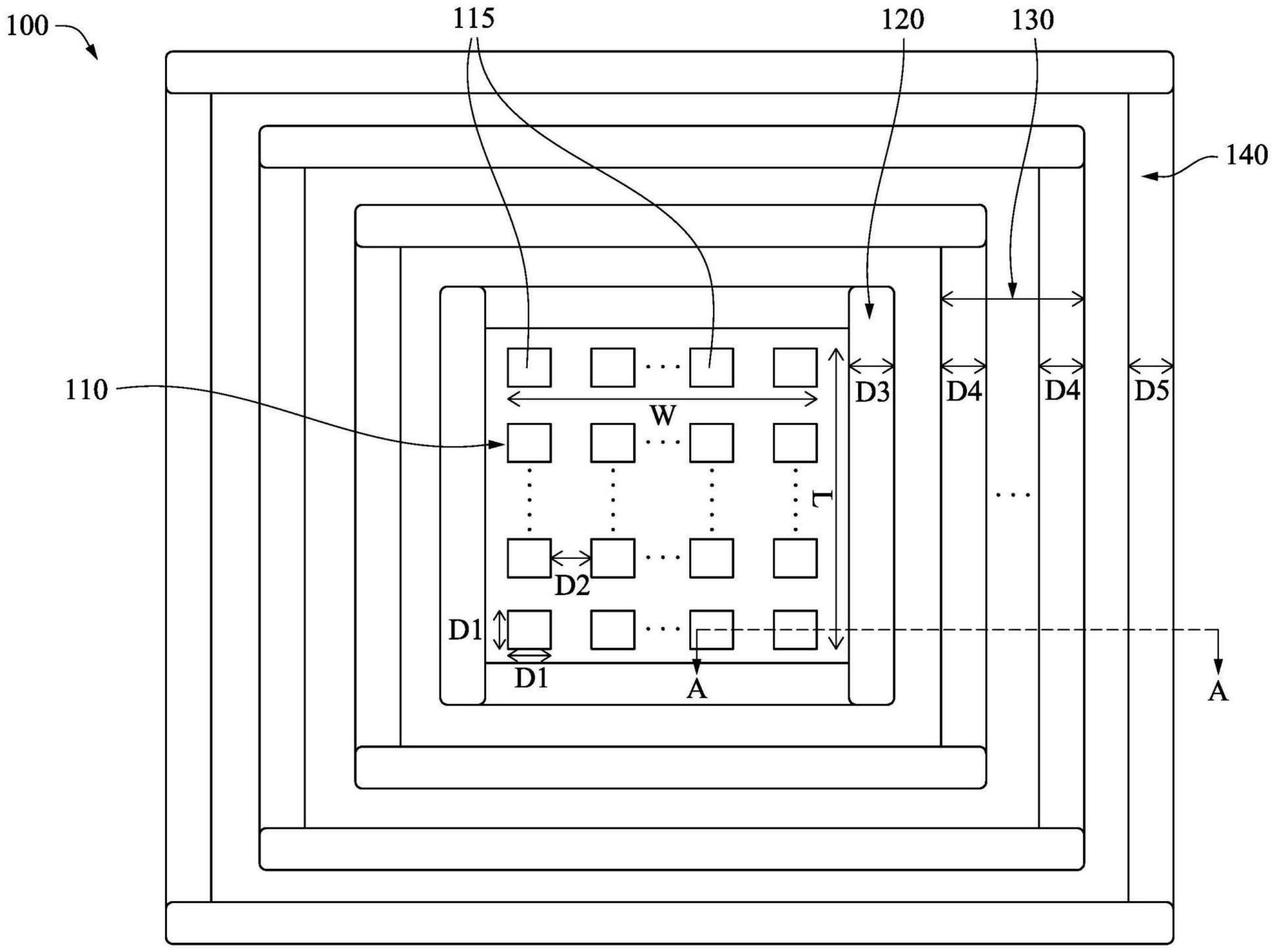

1、根据本公开的一个实施例,提供了一种pin二极管检测器,包括:衬底,其中所述衬底包括像素区域和外围区域,并且所述外围区域包围所述像素区域;多个pin二极管阱,位于所述像素区域中,其中所述多个pin二极管阱中的每一个具有第一掺杂剂类型;连接环阱,位于所述外围区域中,其中所述连接环阱具有所述第一掺杂剂类型;多个浮置环阱,包围所述连接环阱,其中所述多个浮置环阱中的每一个具有所述第一掺杂剂类型;场阻环阱,包围所述多个浮置环阱,其中所述场阻环阱具有与所述第一掺杂剂类型相反的第二掺杂剂类型;以及毯式掺杂区域,其中所述毯式掺杂区域连续地延伸穿过整个所述像素区域和整个所述外围区域,并且所述毯式掺杂区域具有所述第二掺杂剂类型。

2、根据本公开的另一实施例,提供了一种制作pin二极管检测器的方法,所述方法包括:将多个pin二极管阱注入衬底的像素区域中,其中所述多个pin二极管阱中的每一个具有第一掺杂剂类型;将连接环阱注入所述衬底的外围区域中,其中所述外围区域包围所述像素区域,并且所述连接环阱具有所述第一掺杂剂类型;将多个浮置环阱注入所述衬底的外围区域中,其中所述多个浮置环阱中的每一个具有所述第一掺杂剂类型;围绕所述多个浮置环阱注入场阻环阱,其中所述场阻环阱具有与所述第一掺杂剂类型相反的第二掺杂剂类型;以及毯式掺杂所述衬底的像素区域和外围区域,以限定在所述像素区域和所述外围区域上连续的毯式掺杂区域,其中所述毯式掺杂区域具有所述第二掺杂剂类型。

3、根据本公开的又一实施例,提供了一种pin二极管检测器系统,所述系统包括:源,被配置为发射电磁辐射;pin二极管检测器,被配置为检测所述电磁辐射,其中所述pin二极管检测器包括:衬底,其中所述衬底包括像素区域和外围区域,并且所述外围区域包围所述像素区域;多个pin二极管阱,位于所述像素区域中,其中所述多个pin二极管阱中的每一个具有第一掺杂剂类型;连接环阱,位于所述外围区域中,其中所述连接环阱具有所述第一掺杂剂类型;多个浮置环阱,包围所述连接环阱,其中所述多个浮置环阱中的每一个具有所述第一掺杂剂类型;场阻环阱,包围所述多个浮置环阱,其中所述场阻环阱具有与所述第一掺杂剂类型相反的第二掺杂剂类型;以及毯式掺杂区域,其中所述毯式掺杂区域连续地延伸穿过整个所述像素区域和整个所述外围区域,并且所述毯式掺杂区域具有所述第二掺杂剂类型;以及显示器,被配置为显示与检测到的电磁辐射相对应的图像。

技术特征:

1.一种pin二极管检测器,包括:

2.根据权利要求1所述的pin二极管检测器,其中,所述毯式掺杂区域的深度的范围为从0.5微米μm至1.5μm。

3.根据权利要求1所述的pin二极管检测器,其中,所述毯式掺杂区域中的掺杂剂浓度的范围为从1×1014掺杂剂/cm3至1×1015掺杂剂/cm3。

4.根据权利要求1所述的pin二极管检测器,其中,所述衬底包括切片边缘,并且所述衬底包括受损区域,与所述衬底的像素区域的晶体结构相比,在所述受损区域中所述衬底的与所述切片边缘相邻的晶体结构受损。

5.根据权利要求4所述的pin二极管检测器,还包括耗尽区域,位于所述像素区域中的衬底中,其中,所述耗尽区域延伸至所述外围区域中,并且整个所述耗尽区域与所述受损区域分隔开。

6.根据权利要求4所述的pin二极管检测器,其中,所述耗尽区域在所述像素区域的中心区域中的底表面是基本平面的。

7.根据权利要求1所述的pin二极管检测器,其中,所述多个浮置环阱的数量的范围为2到10。

8.根据权利要求1所述的pin二极管检测器,其中,所述多个pin二极管阱位于所述像素区域中的二维阵列中。

9.一种制作pin二极管检测器的方法,所述方法包括:

10.一种pin二极管检测器系统,所述系统包括:

技术总结

本公开涉及PIN二极管检测器、制造方法和包括PIN二极管检测器的系统。一种PIN二极管检测器包括衬底。PIN二极管检测器还包括位于像素区域中的多个PIN二极管阱,其中多个PIN二极管阱中的每一个具有第一掺杂剂类型。PIN二极管检测器还包括位于外围区域中的具有第一掺杂剂类型的连接环阱和多个浮置环阱。PIN二极管检测器还包括包围多个浮置环阱的场阻环阱,其中场阻环阱具有与第一掺杂剂类型相反的第二掺杂剂类型。PIN二极管检测器还包括毯式掺杂区域。毯式掺杂区域连续地延伸穿过整个像素区域和整个外围区域,并且毯式掺杂区域具有第二掺杂剂类型。

技术研发人员:李连杰,韩峰,张璐,陆胜天,桂林春,张成林

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!