封装基板及其制法的制作方法

本发明涉及一种半导体封装工艺,特别涉及一种具核心结构的封装基板及其制法。

背景技术:

1、现今高速运算应用的终端产品(如自动驾驶、超级电脑或移动装置等)正蓬勃发展,其内部皆设有经封装完成的半导体封装元件(芯片结合于封装基板上),借此使相关终端产品发挥作用,并应用于前述相关领域。

2、目前应用于芯片封装领域的技术,包含有例如芯片尺寸构装 (chip scalepackage,简称csp)、芯片直接贴附封装(direct chip attached,简称dca)或多芯片模块封装(multi-chip module,简称 mcm)等覆晶形态的封装模块。

3、现有覆晶形态的封装模块所采用的封装基板1,如图1所示,其包括一核心层10、设于该核心层10上、下两表面上的增层(build up) 结构11、及设于该增层结构11上的防焊层12,其中,该核心层10 具有导电柱100以电性连接该增层结构11的线路层110,且该增层结构11还包含至少一包覆该些线路层110的介电层111,并令该防焊层 12外露出该增层结构11最外侧的线路层110,以供作为电性连接垫 112,以通过焊锡材料13结合如电路板及该半导体芯片等的外部装置。

4、现有核心层10的制作过程中,先采用机械或激光方式进行钻孔,以于孔壁上电镀导电层,再填入如绝缘材100b的塞孔材料,以形成导电柱100。

5、然而,现有封装基板1的核心层10于制作导电柱100时,需配置绝缘材100b,致使该核心层10的各组成材料间的热膨胀系数 (coefficient of thermal expansion,简称cte)差异过大,因而于封装时,该封装基板1容易产生过度翘曲的现象,导致其与外部装置之间连接不良,更严重的是可能因为应力关系,会造成该半导体芯片本身的破裂、或该半导体芯片的电性失效。

6、因此,如何克服上述现有技术的种种问题,实已成为目前业界亟待克服的难题。

技术实现思路

1、鉴于上述现有技术的种种缺失,本发明提供一种封装基板,包括:具有玻纤的核心结构;嵌埋于该核心结构中的实心结构的导电柱,包含第一柱体及堆叠于该第一柱体上的第二柱体;以及形成于该核心结构上以电性连接该导电柱的线路结构。

2、本发明亦提供一种封装基板的制法,包括:提供一具有玻纤的核心结构,且于该核心结构中嵌埋有实心结构的导电柱,其中,该导电柱包含第一柱体及堆叠于该第一柱体上的第二柱体;以及形成线路结构于该核心结构上,以令该线路结构电性连接该导电柱。

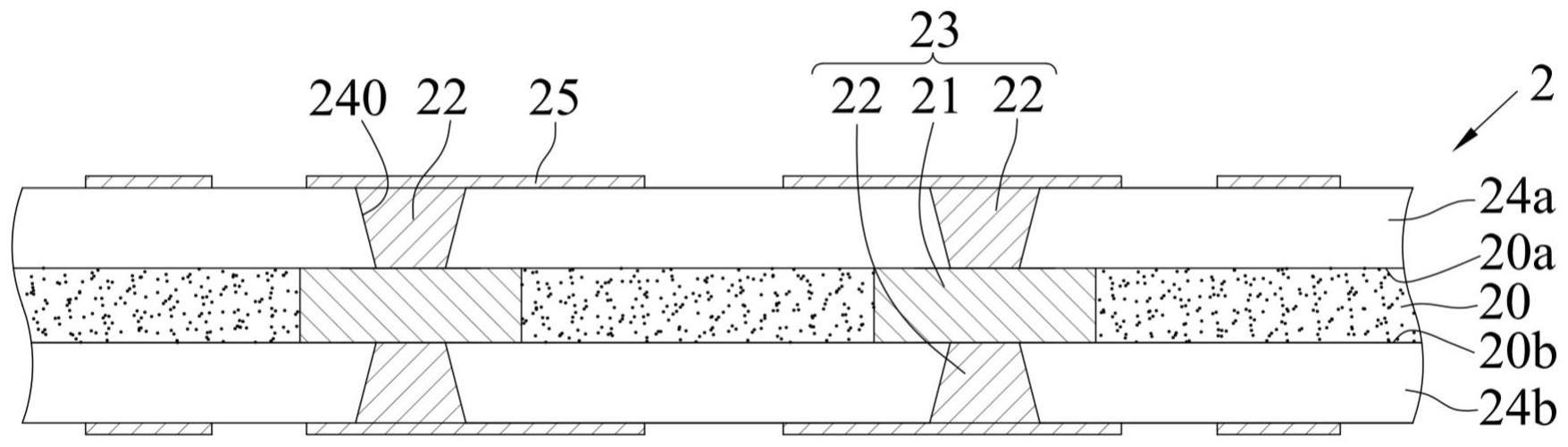

3、前述的封装基板及其制法中,该核心结构包含一具有该玻纤的核心层、及形成于该核心层相对两表面上的第一绝缘层与第二绝缘层。

4、前述的封装基板及其制法中,该第一柱体为宽度一致的直立柱。

5、前述的封装基板及其制法中,该第一柱体为双锥状柱。

6、前述的封装基板及其制法中,该第二柱体为锥状。

7、由上可知,本发明的封装基板及其制法中,主要通过该导电柱为实心结构,因而无需于其内配置绝缘材,以利于控制该核心结构的各组成材料间的热膨胀系数差异符合需求,故相较于现有技术,于封装时,本发明的封装基板不会过度翘曲,因而有利于提升其与外部装置之间的连接良率,以避免因应力关系而造成半导体芯片本身的破裂、或该半导体芯片的电性失效等衍生问题。

技术特征:

1.一种封装基板,包括:

2.如权利要求1所述的封装基板,其中,该核心结构包含一具有该玻纤的核心层、及形成于该核心层相对两表面上的第一绝缘层与第二绝缘层。

3.如权利要求1所述的封装基板,其中,该第一柱体为宽度一致的直立柱。

4.如权利要求1所述的封装基板,其中,该第一柱体为双锥状柱。

5.如权利要求1所述的封装基板,其中,该第二柱体为锥状。

6.一种封装基板的制法,包括:

7.如权利要求6所述的封装基板的制法,其中,该核心结构包含一具有该玻纤的核心层、及形成于该核心层相对两表面上的第一绝缘层与第二绝缘层。

8.如权利要求6所述的封装基板的制法,其中,该第一柱体为宽度一致的直立柱。

9.如权利要求6所述的封装基板的制法,其中,该第一柱体为双锥状柱。

10.如权利要求6所述的封装基板的制法,其中,该第二柱体为锥状。

技术总结

一种封装基板及其制法,包括:于具有玻纤的核心结构中嵌埋实心结构的导电柱,且于该核心结构上形成电性连接该导电柱的线路结构,以通过该导电柱为实心结构,因而有利于控制该核心结构的各组成材料间的热膨胀系数差异符合需求。

技术研发人员:陈敏尧,林松焜,张垂弘

受保护的技术使用者:芯爱科技(南京)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!