半导体晶圆结构及其形成方法与流程

本申请的实施例涉及半导体晶圆结构及其形成方法。

背景技术:

1、许多现代电子器件使用在半导体器件制造工艺期间形成在半导体晶圆上的集成电路。越来越多的半导体晶圆可以堆叠并且接合在一起以形成三维集成电路(3dic)。3dic具有优于传统二维集成电路(2dic)的许多优势,诸如更高的器件密度、更大的速度和更低的功耗。

技术实现思路

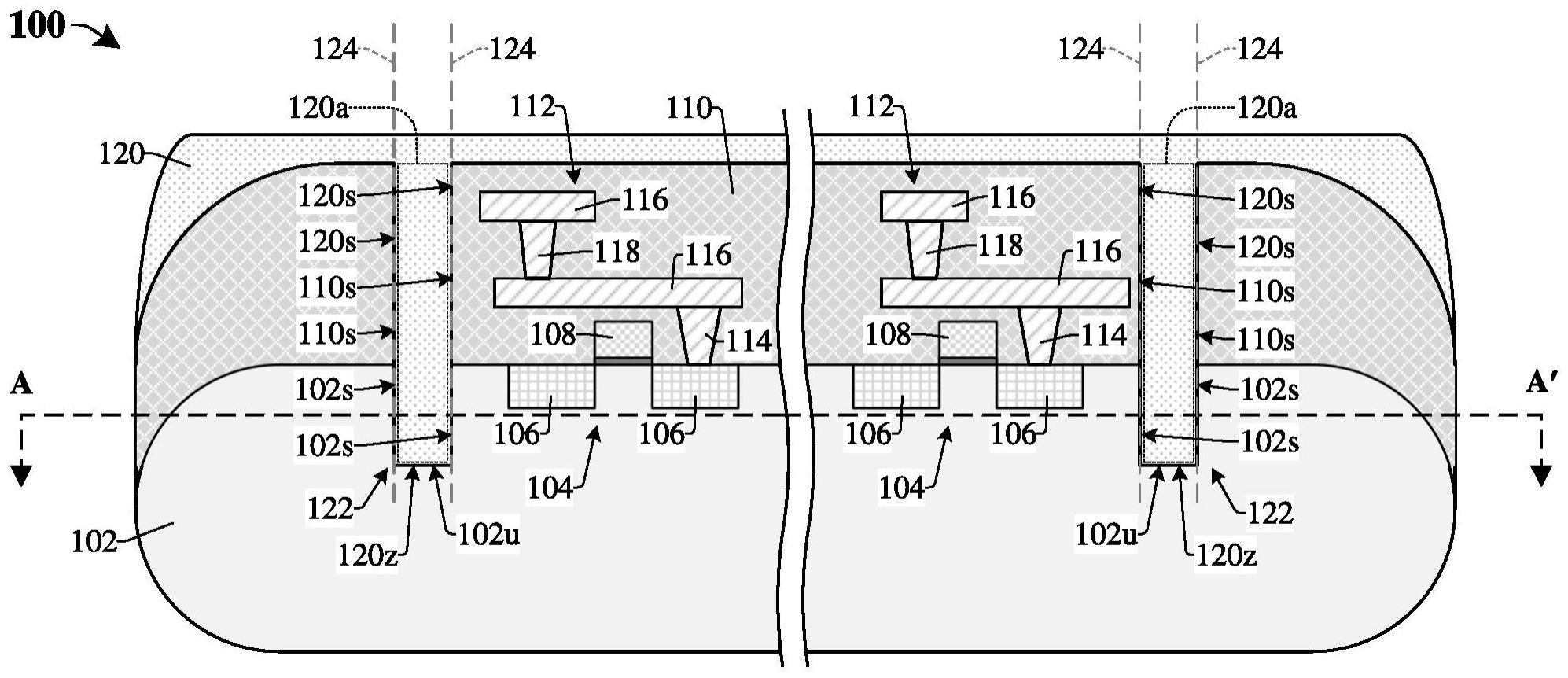

1、本申请的一些实施例提供了一种半导体晶圆结构,包括:半导体衬底;多个半导体器件,沿所述半导体衬底设置;介电堆叠件,包括布置在所述半导体衬底上方的多个介电层;导电互连结构,位于所述介电堆叠件内;以及密封环层,位于所述介电堆叠件上方并且沿所述介电堆叠件的第一侧壁横向围绕所述介电堆叠件,所述密封环层包括延伸至所述半导体衬底中的第一沟槽中的第一突起。

2、本申请的另一些实施例提供了一种用于形成半导体晶圆结构的方法,所述方法包括:沿半导体衬底形成多个半导体器件;在所述半导体衬底上方沉积介电层;在所述介电层内形成导电互连线;在所述半导体衬底中形成第一沟槽,所述第一沟槽沿所述半导体衬底的外围围绕所述半导体衬底的中心;利用第一沉积工艺在所述第一沟槽中以及沿所述介电层的界定所述介电层的外围的侧壁直接在所述介电层上方沉积包括电介质的密封环层的第一部分;以及平坦化所述密封环层的顶面。

3、本申请的又一些实施例提供了一种用于形成半导体晶圆结构的方法,所述方法包括:沿半导体衬底形成多个半导体器件;在所述半导体衬底上方沉积多个介电层以形成介电堆叠件;在所述介电堆叠件内形成多个导电互连线;去除所述半导体衬底的部分以在所述半导体衬底中形成第一沟槽,其中,所述第一沟槽由所述半导体衬底的侧壁界定并且以第一闭合路径围绕所述半导体衬底的中心;以及在所述介电堆叠件上方和所述第一沟槽中沉积电介质以形成具有填充所述第一沟槽的第一突起的密封环层,其中,突起以所述第一闭合路径围绕所述半导体衬底的所述中心,并且其中,所述密封环层以第二闭合路径围绕所述介电堆叠件的外围。

技术特征:

1.一种半导体晶圆结构,包括:

2.根据权利要求1所述的半导体晶圆结构,其中,所述密封环层沿所述介电堆叠件的顶面、沿所述介电堆叠件的所述第一侧壁以及沿所述半导体衬底的侧壁连续延伸,所述半导体衬底的侧壁围绕所述半导体衬底的中心并且设置在所述介电堆叠件的底面下方。

3.根据权利要求1所述的半导体晶圆结构,其中,所述半导体衬底的第一对侧壁界定所述半导体衬底中的所述第一沟槽,并且其中,所述第一突起在所述介电堆叠件的底面下方延伸并且以第一闭合路径围绕所述半导体衬底的中心。

4.根据权利要求3所述的半导体晶圆结构,其中,所述第一突起直接位于界定所述第一沟槽的所述第一对侧壁之间,并且在所述第一闭合路径中沿所述第一沟槽延伸。

5.根据权利要求4所述的半导体晶圆结构,其中,所述第一沟槽的底部由所述半导体衬底的上表面界定,并且其中,所述第一突起的底面位于所述半导体衬底的所述上表面上。

6.根据权利要求4所述的半导体晶圆结构,其中,所述半导体衬底的所述第一对侧壁是锥形的,并且其中,所述密封环层直接位于所述第一对侧壁上方。

7.根据权利要求6所述的半导体晶圆结构,其中,所述第一沟槽的底部由所述第一对侧壁相交的边缘界定,其中,所述密封环层直接位于所述边缘上方,并且其中,所述第一突起的侧壁沿所述边缘相交。

8.根据权利要求4所述的半导体晶圆结构,其中,所述半导体衬底的第二对侧壁界定所述半导体衬底中的第二沟槽,所述第二沟槽以第二闭合路径围绕所述第一沟槽,其中,所述密封环层包括直接在所述第二对侧壁之间延伸至所述第二沟槽中的第二突起,并且其中,所述第二突起在所述第二闭合路径中沿所述第二沟槽延伸。

9.一种用于形成半导体晶圆结构的方法,所述方法包括:

10.一种用于形成半导体晶圆结构的方法,所述方法包括:

技术总结

本发明涉及包括半导体衬底以及沿半导体衬底设置的多个半导体器件的半导体晶圆结构。包括多个介电层的介电堆叠件布置在半导体衬底上方。导电互连结构位于介电堆叠件内。密封环层位于介电堆叠件上方并且沿介电堆叠件的第一侧壁横向围绕介电堆叠件。密封环层包括延伸至半导体衬底中的第一沟槽中的第一突起。本申请的实施例还涉及半导体晶圆结构及其形成方法。

技术研发人员:李名哲,吴国铭,陈昇照,萧豪毅,骆冠宇,陈品孜,蔡正原

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!