半导体互连结构的制作方法

本发明是关于半导体互连结构。

背景技术:

1、集成电路装置(半导体芯片)可以包含数百万个晶体管和其他电路元件,这些晶体管和其他电路元件制造在单个硅晶体基板(晶圆)上。为了使集成电路装置发挥作用,通常会路由复杂的信号路径网络以连接分布在器件表面上的电路元件。随着电路元件的复杂性和数量的增加,这些信号在设备上的有效路由会变得更加困难。因此,多级或多层互连方案的形成,例如双镶嵌布线(互连)结构,由于它们在复杂集成电路上的大量晶体管和其他电路元件之间提供高速信号路由模式的功效,因此变得更受欢迎。

技术实现思路

1、本发明提出一种创新的半导体互连结构,解决先前技术的问题。

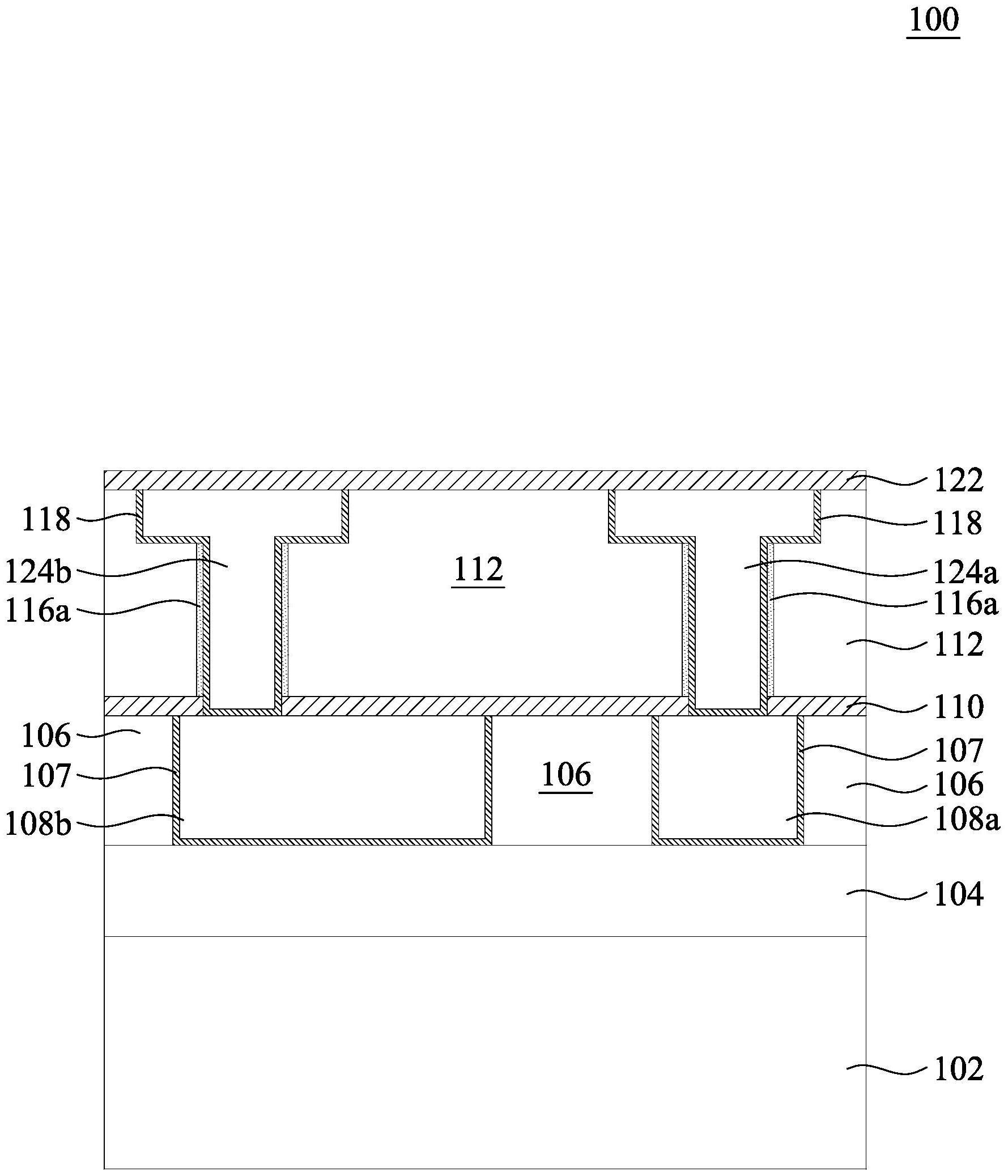

2、于本发明的一些实施例中,一种半导体互连结构包括设置在衬底上方的下层间介电层;下金属连通柱,设置在下层间介电层中;第一水平介电层,设置在下层间介电层和下金属连通柱上方;上层间介电层,设置于第一水平介电层上且介电常数小于第一水平介电层的介电常数;上金属连通柱,设置于上层间介电层与第一水平介电层中,并电性连接下金属连通柱;扩散阻挡层,设置在上金属连通柱周围,并设置在上层间介电层和上金属连通柱之间;及介电侧壁,设置于扩散阻挡层与上层间介电层之间。

3、于本发明的一些实施例中,介电侧壁具有比上层间介电层更高的刚性。

4、于本发明的一些实施例中,第一水平介电层具有比上层间介电层更高的刚性。

5、于本发明的一些实施例中,介电侧壁的介电常数大于上层间介电层的介电常数。

6、于本发明的一些实施例中,介电侧壁的热膨胀系数小于上层间介电层的热膨胀系数。

7、于本发明的一些实施例中,第一水平介电层的热膨胀系数小于上层间介电层的热膨胀系数。

8、于本发明的一些实施例中,上金属连通柱具有t形横截面。

9、于本发明的一些实施例中,介电侧壁的热膨胀系数小于上金属连通柱的热膨胀系数。

10、于本发明的一些实施例中,第一水平介电层的热膨胀系数小于上金属连通柱的热膨胀系数。

11、于本发明的一些实施例中,介电侧壁是原子层沉积氧化物层。

12、于本发明的一些实施例中,介电侧壁是原子层沉积氮化物层。

13、于本发明的一些实施例中,一种半导体互连结构包括设置在衬底上方的下层间介电层;下金属连通柱,设置在下层间介电层中;第一水平介电层,设置在下层间介电层和下金属连通柱上方;上层间介电层,设置于第一水平介电层上且介电常数小于第一水平介电层的介电常数;上金属连通柱,设置于上层间介电层与第一水平介电层中,并电性连接下金属连通柱;扩散阻挡层,设置在上金属连通柱周围,并设置在上层间介电层和上金属连通柱之间;介电侧壁,设置在扩散阻挡层与上层间介电层之间;第二水平介电层设置在上层间介电层之上。

14、于本发明的一些实施例中,介电侧壁实质上垂直于第一水平介电层的顶面。

15、于本发明的一些实施例中,介电侧壁连接第一水平介电层。

16、于本发明的一些实施例中,介电侧壁与第二水平介电层间隔开。

17、于本发明的一些实施例中,上金属连通柱具有t形横截面。

18、于本发明的一些实施例中,下金属连通柱具有矩形横截面。

19、于本发明的一些实施例中,介电侧壁连接于第一水平介电层与第二水平介电层之间。

20、于本发明的一些实施例中,介电侧壁为原子层沉积氧化物层或原子层沉积氮化物层。

21、于本发明的一些实施例中,扩散阻挡层包括以下的至少一种:钽(ta)、氮化钽(tan)、氮化钛(tin)、钛钨(tiw)、钨(w)、氮化钨(wn)、钛-氮化钛(ti-tin)、氮化钛硅(tisin)、氮化硅钨(wsin)及氮化钽硅(tasin)。

22、综合以上,本案所揭露的半导体互连结构具有额外的刚性介电侧壁,其夹在其金属连通柱和低k(低介电常数)松散的层间介电层之间,以避免金属连通柱热膨胀引起的应力迁移。刚性介电侧壁可以使其顶端或底端连接到(上或下)水平介电层,以共同包覆和保护低k松散的层间介电层抵抗金属热膨胀引起的应力迁移。

23、以下将以实施方式对上述的说明作详细的描述,并对本发明的技术方案提供更进一步的解释。

技术特征:

1.一种半导体互连结构,其特征在于,包括:

2.根据权利要求1所述的半导体互连结构,其中该介电侧壁具有比该上层间介电层更高的刚性。

3.根据权利要求1所述的半导体互连结构,其中该第一水平介电层具有比该上层间介电层更高的刚性。

4.根据权利要求1所述的半导体互连结构,其中该介电侧壁的介电常数大于该上层间介电层的介电常数。

5.根据权利要求1所述的半导体互连结构,其中该介电侧壁的热膨胀系数小于该上层间介电层的热膨胀系数。

6.根据权利要求1所述的半导体互连结构,其中该第一水平介电层的热膨胀系数小于该上层间介电层的热膨胀系数。

7.根据权利要求1所述的半导体互连结构,其中该上金属连通柱具有t形横截面。

8.根据权利要求1所述的半导体互连结构,其中该介电侧壁的热膨胀系数小于该上金属连通柱的热膨胀系数。

9.根据权利要求1所述的半导体互连结构,其中该第一水平介电层的热膨胀系数小于该上金属连通柱的热膨胀系数。

10.根据权利要求1所述的半导体互连结构,其中该介电侧壁是原子层沉积氧化物层。

11.根据权利要求1所述的半导体互连结构,其中该介电侧壁是原子层沉积氮化物层。

12.一种半导体互连结构,其特征在于,包括:

13.根据权利要求12所述的半导体互连结构,其中该介电侧壁实质上垂直于该第一水平介电层的顶面。

14.根据权利要求12所述的半导体互连结构,其中该介电侧壁连接该第一水平介电层。

15.根据权利要求12所述的半导体互连结构,其中该介电侧壁与该第二水平介电层间隔开。

16.根据权利要求12所述的半导体互连结构,其中该上金属连通柱具有t形横截面。

17.根据权利要求12所述的半导体互连结构,其中该下金属连通柱具有矩形横截面。

18.根据权利要求12所述的半导体互连结构,其中该介电侧壁连接于该第一水平介电层与该第二水平介电层之间。

19.根据权利要求12所述的半导体互连结构,其中该介电侧壁为原子层沉积氧化物层或原子层沉积氮化物层。

20.根据权利要求12所述的半导体互连结构,其中该扩散阻挡层包括以下的至少一种:钽(ta)、氮化钽(tan)、氮化钛(tin)、钛钨(tiw)、钨(w)、氮化钨(wn)、钛-氮化钛(ti-tin)、氮化钛硅(tisin)、氮化硅钨(wsin)及氮化钽硅(tasin)。

技术总结

一种半导体互连结构包括位于基板上方的下层间介电层;位于下层间介电层中的下金属连通柱;位于下层间介电层和下金属连通柱上方的第一水平介电层;上层间介电层,位于第一水平介电层上方且介电常数小于第一水平介电层的介电常数;上金属连通柱位于上层间介电层和第一水平介电层中与下金属连通柱电连接;位于上金属连通柱周围且位于上层间介电层与上金属连通柱之间的扩散阻挡层;以及介电侧壁位于扩散阻挡层与上层间介电层之间。半导体互连结构具有刚性介电侧壁,其夹在其金属连通柱和低k松散的层间介电层之间,以避免应力迁移的问题。

技术研发人员:黄圣富

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!