具有重分布结构的半导体元件及其制备方法与流程

本申请案主张美国第17/550,317号专利申请案的优先权(即优先权日为“2021年12月14日”),其内容以全文引用的方式并入本文中。本公开是关于一种半导体元件及其制备方法。特别是关于一种具有重分布结构的半导体元件及其制备方法。

背景技术:

1、半导体元件已运用在各种电子应用上,像是个人电脑、手机、数码相机、以及其他的电子设备。半导体元件的尺寸不断微缩化,以满足对不断增长的计算能力的需求。但是,在微缩化的制程期间会出现各种问题,而且这些问题还在不断增加。因此,在达到提高品质、产率、性能、和可靠性以及降低复杂度方面仍然存在挑战。

2、上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不形成本公开的先前技术,且上文的“先前技术”的任何说明均不应做为本案的任一部分。

技术实现思路

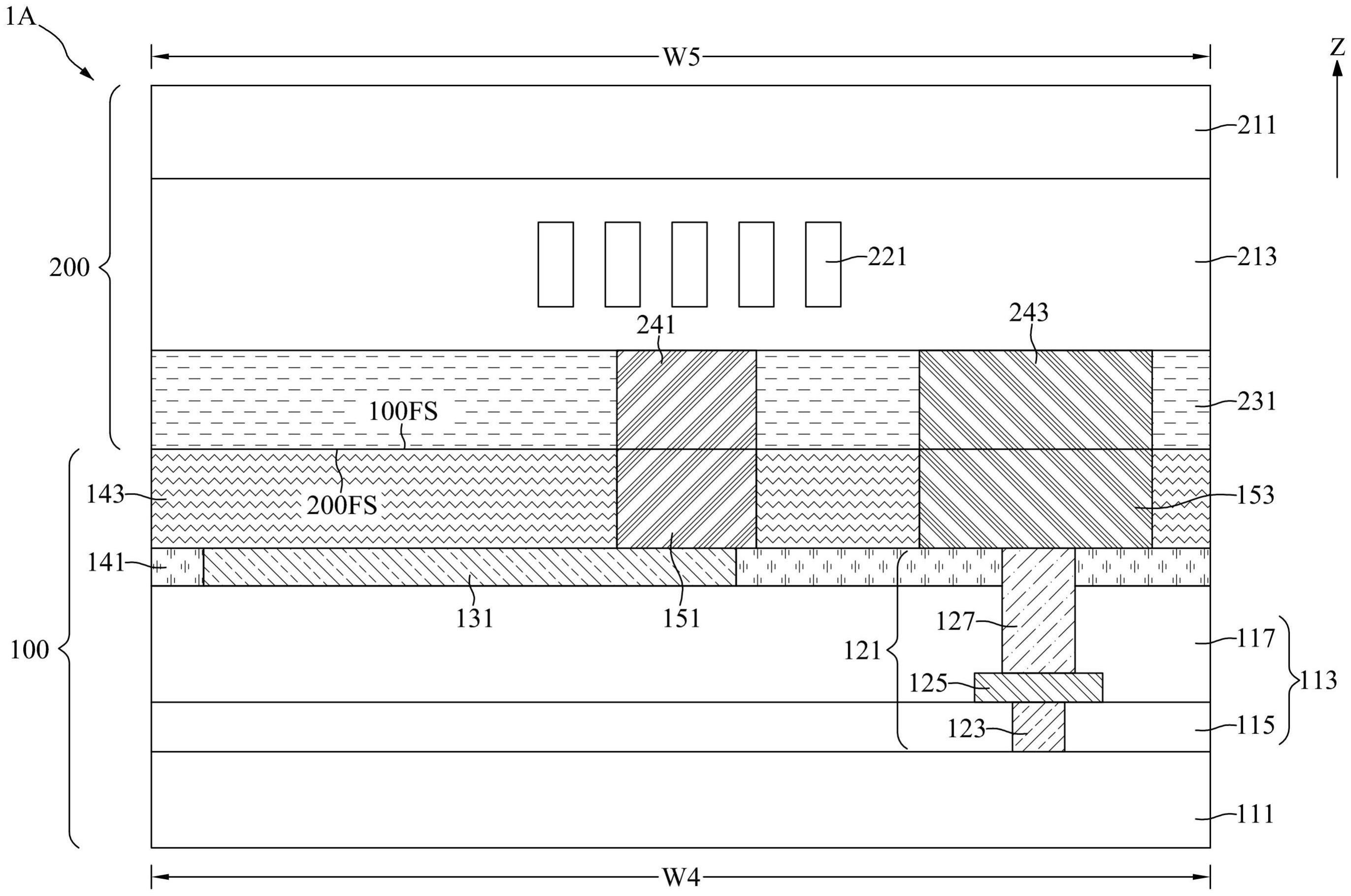

1、本公开的一方面提供一种半导体元件,包括:一第一芯片,其包括:一第一中间介电层,位于一第一基板上;一插塞结构,位于该第一中间介电层中且电性耦合至该第一芯片的一功能单元;一第一重分布层,位于该第一中间介电层上且远离该插塞结构;一第一较低接合垫,位于该第一重分布层上;以及一第二较低接合垫,位于该插塞结构上。该半导体元件还包括位于该第一芯片上的一第二芯片,其包括:一第一较高接合垫,位于该第一较低接合垫上;一第二较高接合垫,位于该第二较低接合垫上;以及多个存储单元,电性耦合至该第一较高接合垫和该第二较高接合垫。

2、在一些实施例中,该第一芯片被配置为一逻辑芯片且该第二芯片被配置为一存储器芯片。

3、在一些实施例中,该插塞结构包括位于该第一基板上的一底部插塞、位于该底部插塞上的一着陆垫、以及位于该着陆垫和该第二较低接合垫之间的一顶部插塞。

4、在一些实施例中,该半导体元件包括一第一障壁层,位于该顶部插塞和该第二较低接合垫之间。

5、在一些实施例中,该半导体元件包括一第二障壁层,位于该着陆垫和该顶部插塞之间。

6、在一些实施例中,该半导体元件包括位于该顶部插塞和该第二较低接合垫之间的一第三障壁层,以及位于该第一较低接合垫和该第一重分布层之间的一第四障壁层。

7、在一些实施例中,该第三障壁层的一底表面位于低于该第一重分布层的一顶表面的一垂直水平(vertical level)。

8、在一些实施例中,该第一芯片的一宽度和该第二芯片的一宽度实质上(substantially)相同。

9、在一些实施例中,该底部插塞包括铝、铜、或前述的组合,且该顶部插塞包括钨。

10、在一些实施例中,该第三障壁层包括钛和氮化钛。

11、在一些实施例中,所述存储单元被配置为一电容阵列或一浮动阵列(floatingarray)。

12、本公开的另一方面提供一种半导体元件,包括:一第一芯片,其包括:一第一基板,包括一中心区域和围绕该中心区域的一周围区域;一第一中心接合垫,位于该第一基板的该中心区域上方;以及一第一周围接合垫,位于该第一基板的该周围区域上方。该半导体元件还包括位于该第一芯片上的一第二芯片,其包括:多个周围较高接合垫,位于该第二芯片的一周围区域且分别位于该第一中心接合垫和该第一周围接合垫上;多个重分布结构,分别位于所述周围较高接合垫上且朝向该第二芯片的一中心区域延伸;多个中心较低接合垫,位于该第二芯片的该中心区域且分别位于所述重分布结构上;以及多个存储单元,电性耦合至所述中心较低接合垫。

13、在一些实施例中,所述重分布结构包括:多个重分布层,分别位于所述周围较高接合垫上,且分别从该第二芯片的该周围区域朝向该第二芯片的该中心区域延伸;以及多个重分布插塞,位于该第二芯片的该中心区域,且分别且对应地位于所述中心较低接合垫和所述重分布层之间。

14、在一些实施例中,该半导体元件包括多个第一支撑插塞,分别位于所述重分布层上,其中所述第一支撑插塞远离所述重分布插塞且所述第一支撑插塞为浮动的(floating)。

15、在一些实施例中,该半导体元件包括多个第二支撑插塞,分别位于所述重分布层上,其中所述第二支撑插塞远离所述第一支撑插塞且所述第二支撑插塞为浮动的。

16、在一些实施例中,相邻对的所述重分布插塞和所述第一支撑插塞之间的距离与相邻对的所述第一支撑插塞和所述第二支撑插塞之间的距离实质上相同。

17、在一些实施例中,该半导体元件包括一模制(molding)层,位于该第一芯片上且覆盖该第二芯片。

18、本公开的另一方面提供一种半导体元件的制备方法,包括:提供一第一基板,包括一功能单元;形成一插塞结构于该第一基板上且电性耦合至该功能单元;形成一第一重分布层于该第一基板上方;形成一第一较低接合垫于该第一重分布层上;形成一第二较低接合垫于该插塞结构上,其中该第一基板、该插塞结构、该第一重分布层、该第一较低接合垫、和该第二较低接合垫一起构成一第一芯片;以及接合一第二芯片至该第一芯片上。该第二芯片包括接合至该第一较低接合垫上的一第一较高接合垫、接合至该第二较低接合垫上的一第二较高接合垫、以及电性耦合至该第一较高接合垫和该第二较高接合垫的多个存储单元。

19、在一些实施例中,该第一芯片被配置为一逻辑芯片且该第二芯片被配置为一存储器芯片,并且所述存储单元被配置为一电容阵列或一浮动阵列。

20、在一些实施例中,该插塞结构包括形成于该第一基板上的一底部插塞、形成于该底部插塞上的一着陆垫、以及形成于该着陆垫上的一顶部插塞。

21、由于本公开的半导体元件的设计,数据信号可以通过第一较高接合垫、第一较低接合垫、和第一重分布层传输而不通过第一芯片的导电部件、插塞结构、和功能单元。其结果,可以缩小传输距离,从而可以提高半导体元件的性能。此外,由于传输距离较短,所以可以降低半导体元件的功耗。

22、上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。形成本公开的权利要求书标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可做为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求书所界定的本公开的精神和范围。

技术特征:

1.一种半导体元件,包括:

2.如权利要求1所述的半导体元件,其中所述重分布结构包括:

3.如权利要求2所述的半导体元件,更包括多个第一支撑插塞,分别位于所述重分布层上,其中所述第一支撑插塞远离所述重分布插塞且所述第一支撑插塞为浮动的。

4.如权利要求3所述的半导体元件,更包括多个第二支撑插塞,分别位于所述重分布层上,其中所述第二支撑插塞远离所述第一支撑插塞且所述第二支撑插塞为浮动的。

5.如权利要求4所述的半导体元件,其中一相邻对的所述重分布插塞和所述第一支撑插塞之间的一距离与一相邻对的所述第一支撑插塞和所述第二支撑插塞之间的一距离实质上相同。

6.如权利要求2所述的半导体元件,更包括一模制层,位于该第一芯片上且覆盖该第二芯片。

7.一种半导体元件的制备方法,包括:

8.如权利要求7所述的半导体元件的制备方法,其中该第一芯片被配置为一逻辑芯片且该第二芯片被配置为一存储器芯片,并且所述存储单元被配置为一电容阵列或一浮动阵列。

9.如权利要求7所述的半导体元件的制备方法,其中所述重分布插塞和所述第二重分布层一起构成多个重分布结构。

10.如权利要求7所述的半导体元件的制备方法,其中所述重分布结构包括:

11.如权利要求7所述的半导体元件的制备方法,其中所述第一支撑插塞远离所述重分布插塞且所述第一支撑插塞为浮动的。

12.如权利要求7所述的半导体元件的制备方法,其中所述第二支撑插塞远离所述第一支撑插塞且所述第二支撑插塞为浮动的。

13.如权利要求7所述的半导体元件的制备方法,其中一相邻对的所述重分布插塞和所述第一支撑插塞之间的一距离与一相邻对的所述第一支撑插塞和所述第二支撑插塞之间的一距离实质上相同。

技术总结

一种半导体元件包括一第一芯片以及位于该第一芯片上的一第二芯片。该第一芯片包括:一第一基板,包括一中心区域和围绕该中心区域的一周围区域;一第一中心接合垫,位于该第一基板的该中心区域上方;以及一第一周围接合垫,位于该第一基板的该周围区域上方。该第二芯片包括:多个周围较高接合垫,位于该第二芯片的一周围区域,且分别位于该第一中心接合垫和该第一周围接合垫上;多个重分布结构,分别位于所述周围较高接合垫上并朝向该第二芯片的一中心区域延伸;多个中心较低接合垫,位于该第二芯片的该中心区域,且分别位于所述重分布结构上;以及多个存储单元,电性耦合至所述中心较低接合垫。

技术研发人员:徐嘉祥

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!