半导体功率器件及其制造方法与流程

本发明涉及一种半导体功率器件,且特别是有关于一种半导体功率器件及其制造方法。

背景技术:

1、高压场效应晶体管,也被认知为功率晶体管或半导体功率器件,在半导体领域是众所周知的;其中包括延伸漏极或漂移区的垂直功率晶体管可以承受所施加的高工作电压,并且这种类型的功率晶体管通常用于功率转换应用,例如用于电源、电机控制等的ac/dc转换器中;这些功率晶体管器件可以在高电压下切换,并在“关闭”状态下具有高反向阻断电压,同时最大限度地减少漏极和源极之间的电流电阻,此在“开启”状态的电阻通常称为比导通电阻(specific on resistance,ron)。

2、在相同器件面积下,碳化硅(sic)mosfet由于其优于硅基器件的物理特性而受到高度关注。例如,与硅mosfet相比,sic mosfet表现出更高的反向阻断电压、更低的ron和更高的热导率。

3、垂直功率mosfet中的比导通电阻(ron)是信道(channel)电阻、jfet电阻、漂移区电阻和衬底电阻的组合。信道电阻是半导体材料、信道宽度、信道长度、操作条件(例如,漏极电流和电压)、载流子迁移率和单元间距的函数。为了在开启状态下获得最佳性能,希望最小化ron。在sic功率晶体管器件中,信道电阻相对较高,而载流子迁移率相对较低。然而,漂移区电阻是阻断电压的直接函数;因此,信道电阻在低于约3300v的电压下占主导地位。

4、为了降低sic功率mosfet的ron,需要复杂的处理步骤,包括调整沟槽、利用新技术或权衡其他器件性能参数,例如击穿电压。此外,通过减少信道长度来降低ron的尝试在很大程度上是不成功的,因为它增加了电流的泄漏,从而降低了器件的反向阻断电压。

技术实现思路

1、本发明提供一种半导体功率器件,用以降低比导通电阻(ron),且不需要复杂的器件设计,也不会对反向阻断电压等性能产生影响。

2、本发明还提供一种半导体功率器件的制造方法,用以降低比导通电阻,且不需要复杂的制程步骤。

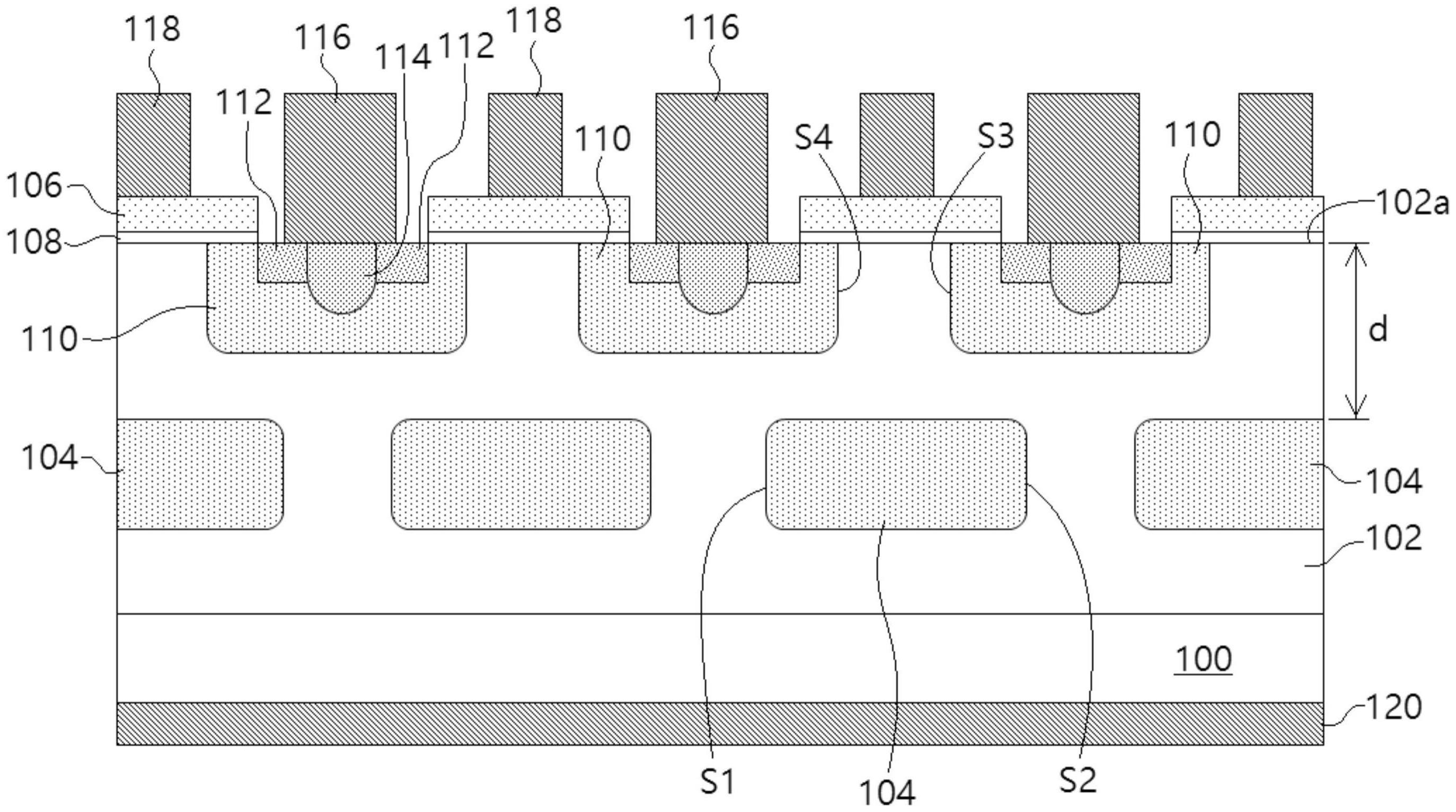

3、本发明的一种半导体功率器件,包括至少衬底、漂移层、数个埋入式掺杂区、数个栅极、栅极绝缘层、数个阱区、数个源极区与数个阱接触区。漂移层设置在衬底上,且埋入式掺杂区设置在漂移层中且相互平行,每个埋入式掺杂区与漂移层的上表面相距预定距离;栅极设置在漂移层的上表面上,且每个栅极位于每个埋入式掺杂区的正上方;栅极绝缘层设置在漂移层和每个栅极之间;阱区设置在漂移层的上表面中,且每个阱区位于栅极之间,并与埋入式掺杂区分开,阱区和埋入式掺杂区电性连接;源极区设置在栅极之间的阱区内,且阱接触区设置在漂移层的上表面中,每个阱接触区穿过源极区并与阱区接触。

4、在本发明的实施例中,上述的半导体功率器件尚包括设置在漂移层中的掺杂区带,以连接数个阱区以及数个埋入式掺杂区。

5、在本发明的实施例中,上述的掺杂区带的延伸方向垂直于数个栅极的延伸方向。

6、在本发明的实施例中,上述的栅极对称地设置在掺杂区带的两侧。

7、在本发明的实施例中,上述的阱区的导电类型与埋入式掺杂区的导电类型相同,并且与源极区的导电类型不同。

8、在本发明的实施例中,上述的数个阱区的掺杂浓度范围为5e16/cm3至1e18/cm3。

9、在本发明的实施例中,上述的数个埋入式掺杂区的掺杂浓度大于2e18/cm3。

10、在本发明的实施例中,上述的数个阱区与数个埋入式掺杂区在垂直投影方向上部分重叠。

11、在本发明的实施例中,上述的每个埋入式掺杂区的两侧与每个阱区的两侧在垂直投影方向上部分重叠。

12、在本发明的实施例中,上述的上述的半导体功率器件尚包括数个源极电极、数个栅极电极与漏极电极。源极电极设置在漂移层的上表面上,以与阱接触区和源极区直接接触;栅极电极分别设置在栅极上;以及漏极电极设置在衬底的底表面上。

13、本发明的一种半导体功率器件的制造方法,包括在衬底的上表面上形成形成第一漂移层,且形成数个埋入式掺杂区在第一漂移层中,其中埋入式掺杂区相互平行;然后在第一漂移层上形成第二漂移层,以覆盖数个埋入式掺杂区,且掺杂区带形成在第二漂移层中,以连接数个埋入式掺杂区;在第二漂移层的上表面形成数个阱区,其中阱区和埋入式掺杂区通过掺杂区带电性连接;在第二漂移层的上表面形成栅极绝缘层,然后在阱区之间的栅极绝缘层上形成数个栅极;在栅极之间的数个阱区中形成数个源极区,以及在第二漂移层的上表面中形成数个阱接触区,以穿过源极区,并与阱区接触。

14、在本发明的另一实施例中,在形成阱接触区之后,上述的半导体功率器件的制造方法尚包括形成数个源极电极和数个栅极电极。源极电极设置在第二漂移层的上表面上,以与数个阱接触区和数个源极区直接接触;以及栅极电极设置在数个栅极上。

15、在本发明的另一实施例中,在形成所述数个源极电极和所述数个栅极电极之后,上述的半导体功率器件的制造方法尚包括在衬底的底表面上形成漏极电极。

16、基于上述,本发明提供的半导体功率器件,由于埋入式掺杂区的存在,可以减轻栅极绝缘层中的电压降(voltage drop),从而可以使栅极绝缘层的厚度相对于传统的高压功率器件显着降低,因而降低了比导通电阻(ron),使电流阻力最大限度地减少。

17、为让本发明的上述特征和优点能更明显易懂,下文特举数个实施例,并配合附图作详细说明如下。

技术特征:

1.一种半导体功率器件,其特征在于,包括:

2.根据权利要求1所述的半导体功率器件,其特征在于,还包括设置在所述漂移层中的掺杂区带,以连接所述数个阱区以及所述数个埋入式掺杂区。

3.根据权利要求2所述的半导体功率器件,其特征在于,所述掺杂区带的延伸方向垂直于所述数个栅极的延伸方向。

4.根据权利要求3所述的半导体功率器件,其特征在于,所述栅极对称地设置在所述掺杂区带的两侧。

5.根据权利要求1所述的半导体功率器件,其特征在于,所述数个阱区的导电类型与所述数个埋入式掺杂区的导电类型相同,并与所述数个源极区的导电类型不同。

6.根据权利要求1所述的半导体功率器件,其特征在于,所述数个阱区的掺杂浓度范围为5e16/cm3至1e18/cm3。

7.根据权利要求1所述的半导体功率器件,其特征在于,所述数个埋入式掺杂区的掺杂浓度大于2e18/cm3。

8.根据权利要求1所述的半导体功率器件,其特征在于,所述数个阱区与所述数个埋入式掺杂区在垂直投影方向上部分重叠。

9.根据权利要求1所述的半导体功率器件,其特征在于,每个所述埋入式掺杂区的两侧与每个所述阱区的两侧在垂直投影方向上部分重叠。

10.根据权利要求1所述的半导体功率器件,其特征在于,还包括:

11.一种半导体功率器件的制造方法,其特征在于,包括:

12.根据权利要求11所述的半导体功率器件的制造方法,其特征在于,在形成所述数个阱接触区之后,还包括:形成数个源极电极和数个栅极电极,所述源极电极设置在所述第二漂移层的所述上表面上,以与所述数个阱接触区和所述数个源极区直接接触;以及所述栅极电极设置在所述数个栅极上。

13.根据权利要求12所述的半导体功率器件的制造方法,其特征在于,在形成所述数个源极电极和所述数个栅极电极之后,还包括:在所述衬底的底表面上形成漏极电极。

技术总结

本发明提供一种半导体功率器件及其制造方法。半导体功率器件包括衬底、设置在衬底上的漂移层、埋入式掺杂区、栅极、栅极绝缘层、阱区、源极区和阱接触区。埋入式掺杂区位于漂移层中且相互平行,且每个埋入式掺杂区与漂移层的上表面相距预定距离;栅极位于漂移层上,且位于埋入式掺杂区的正上方;栅极绝缘层位于漂移层和数个栅极之间;阱区位于栅极之间的漂移层中,并与埋入式掺杂区分开,其中阱区和埋入式掺杂区电性连接;源极区位于栅极之间的阱区内,且每个阱接触区穿过源极区并与阱区接触。

技术研发人员:陈伟梵,蔡国基

受保护的技术使用者:力拓半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!