半导体结构及其制备方法与流程

本公开实施例涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、动态随机存储器(dynamic random access memory,简称dram)是一种高速地、随机地写入和读取数据的半导体存储器,被广泛地应用到数据存储设备或装置中。

2、动态随机存储器通常包括多个重复的储存单元,每个存储单元包括一个晶体管和一个电容器。随着动态随机存储器的尺寸不断缩小、集成度不断提高,动态随机存储器的特征尺寸和单元面积都会减小,使得位线的电阻变大,导致流经位线的电流过小,从而降低了动态随机存储器的性能。

技术实现思路

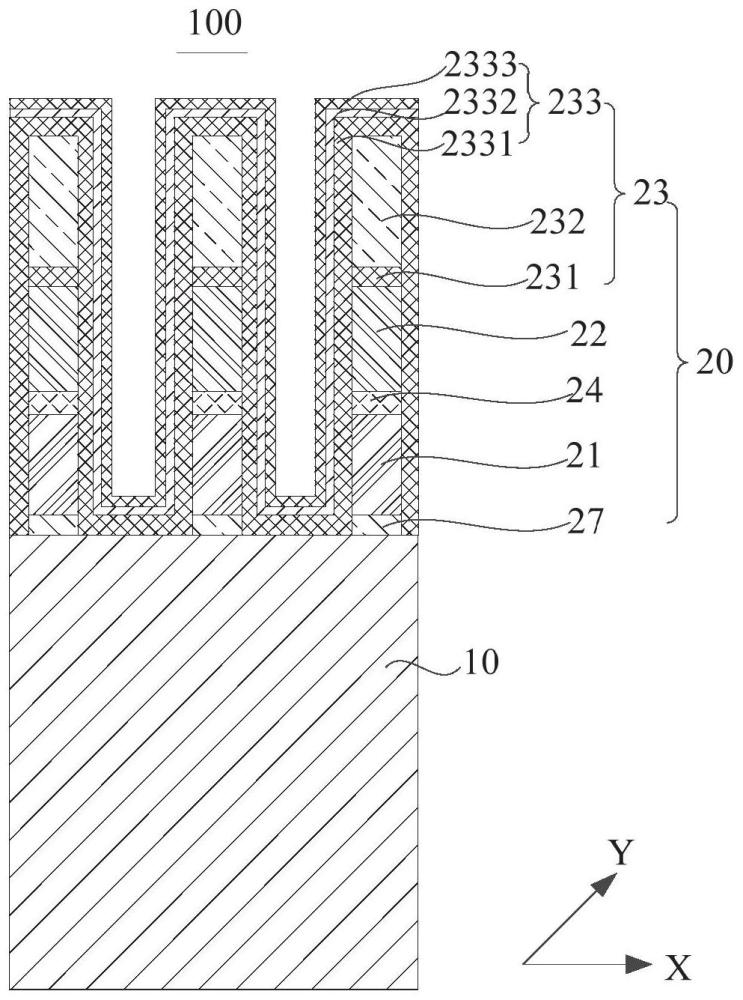

1、本公开实施例的第一方面提供一种半导体结构,其包括:基底以及设置在所述基底上的位线结构;所述位线结构包括掺杂层、导电层和隔离结构,所述导电层设置在所述掺杂层上,所述掺杂层的电阻小于所述导电层的电阻;

2、所述隔离结构覆盖在所述掺杂层和所述导电层上。

3、在一些实施例中,所述掺杂层包括硅锗碳、硅碳、砷化镓、砷化铟或磷化铟中的一种或任意组合。

4、在一些实施例中,所述半导体结构还包括阻挡层,所述阻挡层设置在所述掺杂层和所述导电层之间。

5、在一些实施例中,所述隔离结构包括绝缘层、缓冲层和隔离侧墙;所述缓冲层和所述绝缘层依次层叠设置在所述导电层上;

6、所述隔离侧墙覆盖所述掺杂层、所述导电层、所述缓冲层和所述绝缘层侧壁。

7、在一些实施例中,所述隔离侧墙包括第一隔离层、第二隔离层和第三隔离层,所述第二隔离层位于所述第一隔离层和所述第三隔离层之间,且所述第一隔离层的介电常数小于所述绝缘层的介电常数。

8、在一些实施例中,所述第三隔离层与所述第一隔离层均掺杂碳。

9、在一些实施例中,所述缓冲层和/或所述第一隔离层包括氮碳化硅。

10、在一些实施例中,所述第二隔离层的介电常数介于所述绝缘层与所述第一隔离层之间。

11、在一些实施例中,所述隔离侧墙包括第一氮化硅层、氧化硅层和第二氮化硅层,所述氧化硅层位于所述第一氮化硅层和所述第二氮化硅层之间,且所述第一氮化硅层与所述掺杂层和所述导电层的侧壁接触。

12、本公开实施例第二方面提供一种半导体结构的制备方法,用于形成第一方面所述的半导体结构,包括如下步骤:

13、提供基底;

14、在所述基底上形成位线结构,所述位线结构包括掺杂层、导电层和隔离结构,所述导电层设置在所述掺杂层上,所述掺杂层的电阻小于所述导电层的电阻;所述隔离结构覆盖在所述掺杂层和所述导电层上。

15、在一些实施例中,在所述基底上形成位线结构的步骤包括:

16、在所述基底上形成初始层叠结构,所述层叠结构包括初始掺杂层、初始导电层、初始缓冲层以及初始绝缘层;

17、去除部分所述初始层叠结构,以形成沿第一方向间隔设置的多个层叠结构;每个所述层叠结构包括依次层叠设置的掺杂层、导电层、缓冲层以及绝缘层;

18、形成覆盖所述层叠结构的隔离侧墙,所述层叠结构中的所述缓冲层和所述绝缘层,以及所述隔离侧墙构成隔离结构,所述隔离结构、所述掺杂层和所述导电层构成位线结构。

19、在一些实施例中,在所述基底上形成初始层叠结构的步骤包括:

20、在所述基底上形成第一材料层;

21、向所述第一材料层通入第一掺杂元素,并对所述第一材料层进行处理,以形成初始掺杂层;

22、在所述初始掺杂层上形成依次层叠设置的初始导电层、初始缓冲层和初始绝缘层。

23、在一些实施例中,在所述初始掺杂层上形成依次层叠设置的初始缓冲层和初始绝缘层的步骤包括:

24、在所述初始导电层上形成第二材料层;

25、向所述第二材料层通入第二掺杂元素,并对所述第二材料层进行处理,形成初始缓冲层;

26、在所述初始缓冲层上形成初始绝缘层。

27、在一些实施例中,在形成覆盖所述层叠结构的隔离侧墙的步骤,包括:在所述层叠结构的侧壁上形成第一初始隔离层,所述第一初始隔离层覆盖在层叠结构的顶面上;

28、对所述第一初始隔离层进行掺杂,以形成第一隔离层;所述第一隔离层的介电常数小于所述绝缘层的介电常数;

29、在所述第一隔离层上形成依次层叠设置的第二隔离层和第三初始隔离层;

30、对所述第三初始隔离层进行掺杂,以形成第三隔离层。

31、在一些实施例中,对所述第一初始隔离层进行掺杂,以形成第一隔离层的步骤包括:

32、通过等离子体掺杂工艺向所述第一初始隔离层内注入第三掺杂元素;所述等离子体掺杂工艺的注入方向与垂直于所述基底的方向之间的夹角为8°-11°。

33、在一些实施例中,所述第三掺杂元素为碳,所述第三掺杂元素的含量占所述第一隔离层中所有元素的8%-15%。

34、本公开实施例所提供的半导体结构及其制备方法中,通过在位线结构中增加具有低电阻的掺杂层,以此降低位线结构的电阻。在不影响半导体结构向小尺寸方向发展的前提下,也能够提高半导体结构的电性能的均匀性和稳定性。

35、除了上面所描述的本公开实施例解决的技术问题、构成技术方案的技术特征以及由这些技术方案的技术特征所带来的有益效果外,本公开实施例提供的半导体结构及其制备方法所能解决的其他技术问题、技术方案中包含的其他技术特征以及这些技术特征带来的有益效果,将在具体实施方式中作出进一步详细的说明。

技术特征:

1.一种半导体结构,其特征在于,包括:基底以及设置在所述基底上的位线结构;所述位线结构包括掺杂层、导电层和隔离结构,所述导电层设置在所述掺杂层上,所述掺杂层的电阻小于所述导电层的电阻;

2.根据权利要求1所述的半导体结构,其特征在于,所述掺杂层包括硅锗碳、硅碳、砷化镓、砷化铟或磷化铟中的一种或任意组合。

3.根据权利要求1或2所述的半导体结构,其特征在于,所述半导体结构还包括阻挡层,所述阻挡层设置在所述掺杂层和所述导电层之间。

4.根据权利要求1或2所述的半导体结构,其特征在于,所述隔离结构包括绝缘层、缓冲层和隔离侧墙;所述缓冲层和所述绝缘层依次层叠设置在所述导电层上;

5.根据权利要求4所述的半导体结构,其特征在于,所述隔离侧墙包括第一隔离层、第二隔离层和第三隔离层,所述第二隔离层位于所述第一隔离层和所述第三隔离层之间,且所述第一隔离层的介电常数小于所述绝缘层的介电常数。

6.根据权利要求5所述的半导体结构,其特征在于,所述第三隔离层与所述第一隔离层均掺杂碳。

7.根据权利要求6所述的半导体结构,其特征在于,所述缓冲层和/或所述第一隔离层包括氮碳化硅。

8.根据权利要求5所述的半导体结构,其特征在于,所述第二隔离层的介电常数介于所述绝缘层与所述第一隔离层之间。

9.根据权利要求4所述的半导体结构,其特征在于,所述隔离侧墙包括第一氮化硅层、氧化硅层和第二氮化硅层,所述氧化硅层位于所述第一氮化硅层和所述第二氮化硅层之间,且所述第一氮化硅层与所述掺杂层和所述导电层的侧壁接触。

10.一种半导体结构的制备方法,其特征在于,用于形成权利要求1-9任一所述的半导体结构,包括如下步骤:

11.根据权利要求10所述的半导体结构的制备方法,其特征在于,在所述基底上形成位线结构的步骤包括:

12.根据权利要求11所述的半导体结构的制备方法,其特征在于,在所述基底上形成初始层叠结构的步骤包括:

13.根据权利要求12所述的半导体结构的制备方法,其特征在于,在所述初始掺杂层上形成依次层叠设置的初始缓冲层和初始绝缘层的步骤包括:

14.根据权利要求11-13任一项所述的半导体结构的制备方法,其特征在于,在形成覆盖所述层叠结构的隔离侧墙的步骤,包括:在所述层叠结构的侧壁上形成第一初始隔离层,所述第一初始隔离层覆盖在层叠结构的顶面上;

15.根据权利要求14所述的半导体结构的制备方法,其特征在于,对所述第一初始隔离层进行掺杂,以形成第一隔离层的步骤包括:

16.根据权利要求15所述的半导体结构的制备方法,其特征在于,所述第三掺杂元素为碳,所述第三掺杂元素的含量占所述第一隔离层中所有元素的8%-15%。

技术总结

本公开实施例提供一种半导体结构及其制备方法,涉及半导体技术领域,用于解决半导体结构性能差的技术问题,该半导体结构包括基底以及设置在基底上的位线结构;位线结构包括掺杂层、导电层和隔离结构,掺杂层设置在基底上,且掺杂层的电阻小于导电层的电阻;隔离结构覆盖在掺杂层和导电层上。本公开通过使位线结构具有低电阻的掺杂层,以此降低位线结构的电阻。在不影响半导体结构向小尺寸方向发展的前提下,也能够提高半导体结构的电性能的均匀性和稳定性。

技术研发人员:廖昱程,刘文杰,陈慕宇,李延龙,张磊

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!