用于在导电层中形成开口和使用开口的方法与流程

本公开的实施例大体上涉及半导体装置,且更确切地说,涉及用于在导电层中形成开口且使用开口的方法。

背景技术:

1、高数据可靠性、高存数据存取速度、较低功耗和减小的芯片大小是半导体装置所需要的特征。为了减小芯片大小,电路元件之间的距离已变得越来越短。

2、半导体装置包含导体,例如,将电路耦合到布线的接触插塞。导体可由导电层的导电材料形成。在一些常规方法中,导电材料可形成于通过蚀刻形成于介电层中的开口中。在一些其它常规方法中,导体可在可通过蚀刻形成导电层中的开口之后由导电层的剩余导电材料形成。在常规方法中,常规硬掩模可用于在导电层中形成开口。举例来说,此类常规硬掩模可以是二氧化硅硬掩模(例如,teos硬掩模)。硬掩模可形成于导电层上和二氧化硅(sio2)掩模下方。

3、常规硬掩模可在处理(例如,蚀刻)期间被高能量动能(例如,离子、电子或光子)束损坏。因此,导电层的位于掩模的损坏部分下且开口周围的顶部部分往往会被过度蚀刻。因此,在蚀刻工艺之后,导电层的顶部部分可能变得过度狭窄,这是不合需要的。

技术实现思路

1、根据本公开的一方面,提供一种方法。方法包括:形成导电层;在导电层上形成第一硬掩模;在第一硬掩模上形成第二硬掩模;提供穿过第一硬掩模和第二硬掩模的开口;以及去除导电层在开口下的表面,其中第一硬掩模的硬度大于第二硬掩模的硬度。

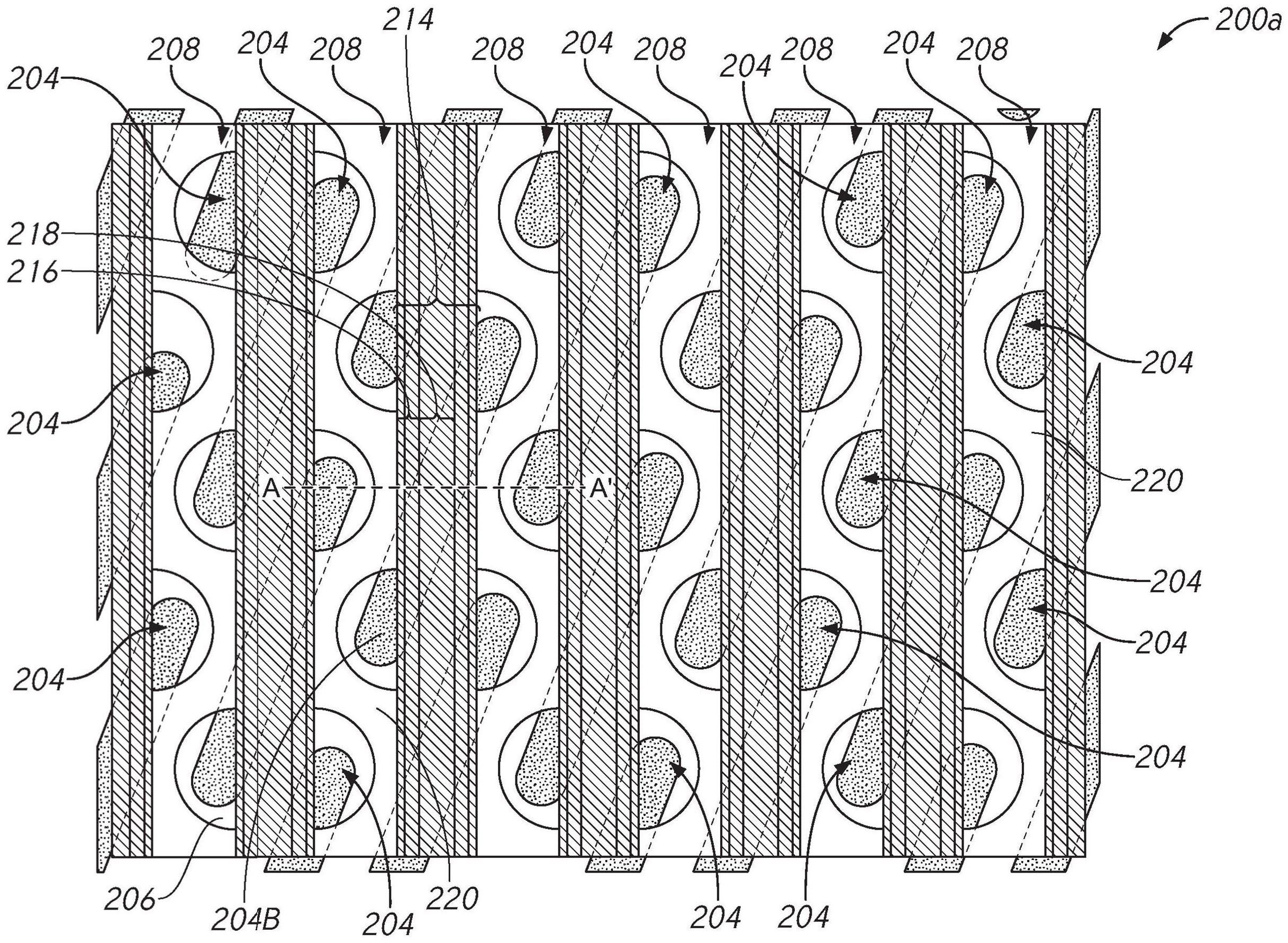

2、根据本公开的另一方面,提供一种方法。方法包括:通过以下形成位线触点、位于位线触点上的位线和位于位线触点上的介电膜:在位线触点、位线和介电膜的侧上形成在第一方向上延伸的第一开口;在第一开口中的位线触点和位线以及介电膜的侧上形成一或多个介电膜;将导电材料沉积于第一开口中;通过在第二方向上延伸的第二开口在导电材料上提供多个第一硬掩模且在多个对应第一硬掩模上提供多个第二硬掩模;去除第二开口下方的导电材料以形成第三开口;以及将介电材料沉积于第三开口中。

3、根据本公开的又一方面,提供了一种设备。设备包括:在第一方向上彼此邻近的第一电容器触点和第二电容器触点;位线触点,其在第二方向上延伸于第一电容器触点与第二电容器触点之间;以及位线,其位于在第二方向上延伸于第一电容器触点与第二电容器触点之间的位线触点上,其中第一电容器触点和第二电容器触点包含多晶硅。

技术特征:

1.一种方法,其包括:

2.根据权利要求1所述的方法,其中所述第一硬掩模的所述硬度大于所述导电层的硬度。

3.根据权利要求1所述的方法,其中所述导电层包括多晶硅。

4.根据权利要求1所述的方法,其中所述第一硬掩模包括金属。

5.根据权利要求1所述的方法,其中所述第二硬掩模包括氧化硅。

6.根据权利要求1所述的方法,其中通过光刻提供穿过所述第一硬掩模和所述第二硬掩模的所述开口。

7.根据权利要求1所述的方法,其中去除包括通过所述开口施加一或多个带电粒子束。

8.根据权利要求7所述的方法,其中所述一或多个带电粒子束包括离子束。

9.根据权利要求8所述的方法,其中所述离子束包括卤素离子束。

10.一种方法,其包括:

11.根据权利要求10所述的方法,其中所述第一硬掩模的硬度大于所述第二硬掩模的硬度。

12.根据权利要求11所述的方法,其中所述第一硬掩模包括金属。

13.根据权利要求10所述的方法,其中所述第二硬掩模包括氧化硅。

14.根据权利要求10所述的方法,其中所述第一硬掩模的硬度大于所述导电材料的硬度。

15.根据权利要求14所述的方法,其中所述导电材料包括多晶硅。

16.根据权利要求10所述的方法,其进一步包括:

17.根据权利要求10所述的方法,其中所述导电材料是所述第一材料,且

18.根据权利要求17所述的方法,其中所述有源区是第一有源区,且

19.一种设备,其包括:

20.根据权利要求19所述的设备,其进一步包括:

21.根据权利要求19所述的设备,其进一步包括位于所述第一电容器触点上的重布层。

技术总结

描述用于在导电层中形成开口和使用所述开口的方法。实例方法包含:形成导电层;在所述导电层上形成第一硬掩模;在所述第一硬掩模上形成第二硬掩模;提供穿过所述第一硬掩模和所述第二硬掩模的开口;以及去除所述导电层在所述开口下方的表面。所述第一硬掩模的硬度可大于所述第二硬掩模的硬度。

技术研发人员:巴山剛,小冢计介

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!