半导体结构及其制备方法与流程

本公开涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、动态随机存取存储器(dynamic random access memory,简称dram)是一种高速地、随机地写入和读取数据的半导体存储器,被广泛地应用到数据存储设备或装置中。

2、dram器件的衬底中包括多个间隔设置的源/漏区,相邻的源/漏区之间设置有隔离区,隔离区内设置有隔离结构,以阻隔相邻的源/漏区,避免相邻的源/漏区之间电性干扰。上述的源/漏区的隔离结构常采用浅沟槽隔离工艺(shallow trench isolation,简称sti)制备。

3、然而,上述的隔离结构中存在热载流子穿透效应(hot electron induced punchthrough,简称heip),产生漏电,从而导致dram器件的不良。

技术实现思路

1、本公开提供一种半导体结构及其制备方法,能够有效缓解半导体结构的heip效应,避免产生漏电,从而提高半导体结构的良率。

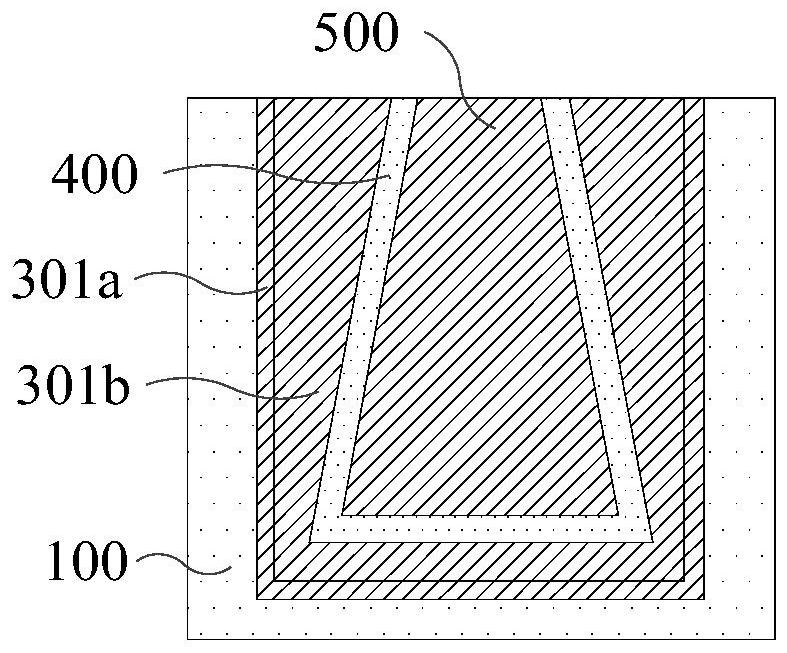

2、第一方面,本公开提供一种半导体结构,包括:

3、衬底,衬底包括有源区和第一沟槽,第一沟槽位于有源区的一侧;

4、第一隔离层,第一隔离层位于第一沟槽中,第一隔离层中设置有第二沟槽;

5、绝缘层,绝缘层位于第二沟槽中,绝缘层中设置有第三沟槽;

6、第二隔离层,第二隔离层填充第三沟槽;

7、位于第二沟槽的顶部侧壁的绝缘层与有源区之间的距离,大于位于第二沟槽的底部侧壁的绝缘层与有源区之间的距离。

8、在上述的半导体结构中,可选的是,位于第一沟槽的顶部侧壁的第一隔离层的厚度,大于位于第一沟槽的底部侧壁的第一隔离层的厚度。

9、在上述的半导体结构中,可选的是,沿第一沟槽的槽口至第一沟槽的槽底的方向,位于第一沟槽的侧壁的第一隔离层的厚度逐渐减小。

10、在上述的半导体结构中,可选的是,位于第二沟槽的顶部侧壁的绝缘层的厚度,小于位于第二沟槽的底部侧壁的绝缘层的厚度。

11、在上述的半导体结构中,可选的是,沿第二沟槽的槽口至槽底的方向,位于第二沟槽侧壁的绝缘层的厚度逐渐增大。

12、在上述的半导体结构中,可选的是,第一隔离层和第二隔离层的材质相同,第一隔离层的材料和绝缘层的材料不同。

13、在上述的半导体结构中,可选的是,位于第一沟槽的顶部侧壁的第一隔离层的厚度不小于10nm;位于第一沟槽的底部侧壁的第一隔离层的厚度范围为2-5nm。

14、在上述的半导体结构中,可选的是,绝缘层连续覆盖第二沟槽的底面和部分侧壁,绝缘层侧壁的顶面低于第一隔离层的顶面。

15、在上述的半导体结构中,可选的是,第一隔离层的顶部与第二隔离层的顶部相接触,绝缘层的侧壁顶面与第一隔离层的顶面的距离为10nm-15nm。

16、第二方面,本公开提供一种半导体结构的制备方法,包括:

17、提供衬底,在衬底中形成有源区和第一沟槽,第一沟槽位于有源区的一侧;

18、形成第一隔离层,第一隔离层位于第一沟槽中,第一隔离层中围成有第二沟槽;

19、形成绝缘层,绝缘层位于第二沟槽中,绝缘层中围成有第三沟槽;

20、形成第二隔离层,第二隔离层填充第三沟槽;

21、位于第二沟槽的顶部侧壁的绝缘层与有源区之间的距离,大于位于第二沟槽的底部侧壁的绝缘层与有源区之间的距离。

22、在上述的半导体结构的制备方法中,可选的是,形成第一隔离层,包括:

23、形成第一子隔离层,第一子隔离层位于第一沟槽中;

24、形成第二子隔离层,第二子隔离层覆盖于第一子隔离层的表面,第二子隔离层的侧壁顶部的厚度大于第二子隔离层的侧壁底部的厚度;

25、第一子隔离层和第二子隔离层共同形成第一隔离层。

26、在上述的半导体结构的制备方法中,可选的是,通过原子层沉积工艺和原位水汽生成工艺制备第一子隔离层;

27、和/或,通过原子层沉积工艺和低台阶覆盖工艺制备第二子隔离层。

28、在上述的半导体结构的制备方法中,可选的是,形成绝缘层,包括:

29、在第二沟槽中形成绝缘材料层,绝缘材料层完全覆盖第一隔离层的表面,在第二沟槽中形成的绝缘层的侧壁顶部的厚度小于绝缘层的侧壁底部的厚度。

30、在上述的半导体结构的制备方法中,可选的是,形成绝缘层,还包括:回刻绝缘材料层,去除位于第二沟槽顶部侧壁的绝缘材料层。

31、在上述的半导体结构的制备方法中,可选的是,回刻绝缘材料层的深度为10nm-15nm。

32、本公开提供一种半导体结构及其制备方法,通过在半导体结构中设置具有第一沟槽的衬底,第一沟槽位于衬底的有源区的一侧。在第一沟槽中设置第一隔离层、绝缘层和第二隔离层,三者可以形成隔离结构,用于隔离不同的有源区,避免有源区之间发生电性干扰。第一沟槽中的绝缘层与有源区之间设置有第一隔离层,并且位于第二沟槽的顶部侧壁的绝缘层与有源区之间的距离,大于位于第二沟槽的底部侧壁的绝缘层与有源区之间的距离。这样,可以避免衬底中的热载流子被绝缘层捕获而形成电子聚集区,从而防止在有源区中形成与电子聚集区对应的空穴聚集区,降低两者之间发生击穿的可能性,防止第一沟槽中的隔离结构发生漏电,从而提高半导体结构的良率。

33、本公开的构造以及它的其他发明目的及有益效果将会通过结合附图而对优选实施例的描述而更加明显易懂。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,位于所述第一沟槽的顶部侧壁的所述第一隔离层的厚度,大于位于所述第一沟槽的底部侧壁的所述第一隔离层的厚度。

3.根据权利要求2所述的半导体结构,其特征在于,沿所述第一沟槽的槽口至槽底的方向,位于所述第一沟槽侧壁的所述第一隔离层的厚度逐渐减小。

4.根据权利要求1-3中任一项所述的半导体结构,其特征在于,位于所述第二沟槽的顶部侧壁的所述绝缘层的厚度,小于位于所述第二沟槽的底部侧壁的所述绝缘层的厚度。

5.根据权利要求4所述的半导体结构,其特征在于,沿所述第二沟槽的槽口至槽底的方向,位于所述第二沟槽侧壁的所述绝缘层的厚度逐渐增大。

6.根据权利要求1-3中任一项所述的半导体结构,其特征在于,所述第一隔离层和所述第二隔离层的材质相同,所述第一隔离层的材料和所述绝缘层的材料不同。

7.根据权利要求2或3所述的半导体结构,其特征在于,位于所述第一沟槽的顶部侧壁的所述第一隔离层的厚度不小于10nm,位于所述第一沟槽的底部侧壁的所述第一隔离层的厚度为2nm-5nm。

8.根据权利要求2或3所述的半导体结构,其特征在于,所述绝缘层连续覆盖所述第二沟槽的底面和部分侧壁,所述绝缘层侧壁的顶面低于所述第一隔离层的顶面。

9.根据权利要求8所述的半导体结构,其特征在于,所述第一隔离层的顶部与所述第二隔离层的顶部相接触,所述绝缘层的侧壁顶面与所述第一隔离层的顶面的距离为10nm-15nm。

10.一种半导体结构的制备方法,其特征在于,包括:

11.根据权利要求10所述的半导体结构的制备方法,其特征在于,形成所述第一隔离层,包括:

12.根据权利要求11所述的半导体结构的制备方法,其特征在于,通过原子层沉积工艺和原位水汽生成工艺制备所述第一子隔离层;

13.根据权利要求10-12中任一项所述的半导体结构的制备方法,其特征在于,形成所述绝缘层,包括:在所述第二沟槽中形成绝缘材料层,所述绝缘材料层完全覆盖所述第一隔离层的表面,在所述第二沟槽中形成的所述绝缘层的侧壁顶部的厚度小于所述绝缘层的侧壁底部的厚度。

14.根据权利要求13所述的半导体结构的制备方法,其特征在于,形成所述绝缘层,还包括:回刻所述绝缘材料层,去除位于所述第二沟槽顶部侧壁的所述绝缘材料层。

15.根据权利要求14所述的半导体结构的制备方法,其特征在于,回刻所述绝缘材料层的深度为10nm-15nm。

技术总结

本公开提供一种半导体结构及其制备方法,该半导体结构包括衬底、第一隔离层、绝缘层和第二隔离层。衬底包括有源区和第一沟槽,第一沟槽位于有源区的一侧,第一隔离层位于第一沟槽中,第一隔离层中设置有第二沟槽,绝缘层位于第二沟槽中,绝缘层中设置有第三沟槽,第二隔离层填充第三沟槽;位于第二沟槽的顶部侧壁的绝缘层与有源区之间的距离,大于位于第二沟槽的底部侧壁的绝缘层与有源区之间的距离。本公开能够有效缓解半导体结构的HEIP效应,避免产生漏电,从而提高半导体结构的良率。

技术研发人员:乔梦竹

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!