半导体结构的形成方法与流程

本发明涉及半导体,具体涉及一种半导体结构的形成方法。

背景技术:

1、随着半导体技术的发展,半导体器件的尺寸持续减小。其中,在集成电路后段制成工艺中,对金属线的尺寸要求也相应提高,因此,通过改进工艺以保证高质量、小尺寸的金属线是目前广泛研究的课题。

2、在现有的7nm以下制程的半导体制备工艺中,自对准四重图形工艺(self-alignedquadruple patterning,saqp)是制备小尺寸金属线的重要手段。自对准四重图形工艺的过程包括:第一步,形成第一芯轴图形;第二步,在第一芯轴图形侧壁通过淀积形成第一侧墙图形,并去除第一芯轴图形;第三步,传递第一侧墙图形,并以此形成第二芯轴图形;第四步,在第二芯轴图形侧壁通过淀积形成第二侧墙图形,并去除第二芯轴图形,以此使最终图形节距(pitch)仅为初始图形节距的四分之一,极大地缩小了图形尺寸。

3、然而,在现有工艺中,以自对准四重图形工艺形成的金属线的图形由第一芯轴图形以及第二芯轴图形的结构确定,通常为连续且长度相等的线形结构,其图案的选择非常有限,难以形成传统光刻工艺能够达成的各种尺寸的头碰头(head to head)间断金属线结构,因此,使集成电路设计的灵活性较差。

技术实现思路

1、本发明解决的技术问题是,提供一种半导体结构的形成方法,提升了半导体结构的图案灵活性,改善了工艺窗口和兼容性。

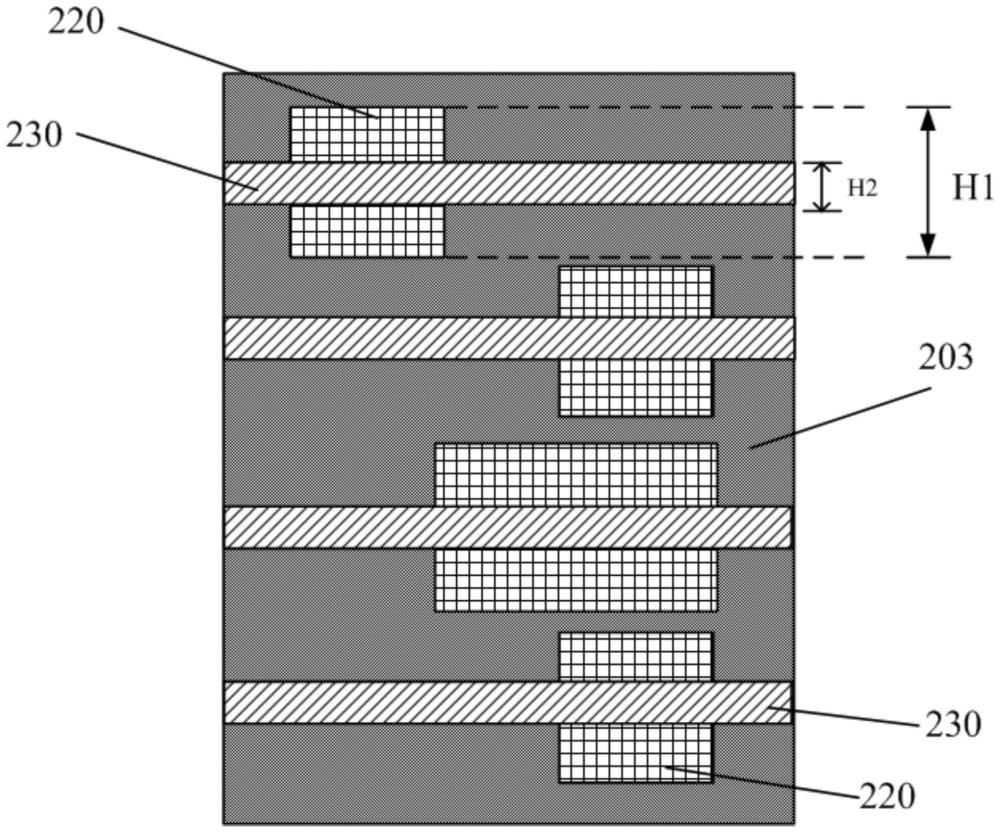

2、为解决上述技术问题,本发明的技术方案提供一种半导体结构的形成方法,包括:提供衬底;在衬底上形成第一材料层;对第一材料层进行离子注入,以形成位于第一材料层内的若干离子掺杂区,离子掺杂区平行于第一方向上的尺寸为第一尺寸,离子掺杂区在垂直于第一方向的第二方向上的尺寸为第二尺寸,第一尺寸大于或等于第二尺寸,所述第一方向和所述第二方向均平行于衬底表面;在第一材料层上形成若干第一掩膜结构,各第一掩膜结构至少位于各离子掺杂区的部分表面;以第一掩膜结构为掩膜,刻蚀第一材料层,以形成若干第二芯轴结构,各第二芯轴结构包括离子掺杂区以及与离子掺杂区相邻的牺牲结构;在各第二芯轴结构侧壁形成第二侧墙结构;去除牺牲结构。

3、可选的,各第一掩膜结构在第一材料层表面的投影图形为第一图形,各离子掺杂区仅与一个第一图形有交集。

4、可选的,各离子掺杂区的第一尺寸相同或不同。

5、可选的,各第一掩膜结构在垂直于第一方向的第二方向上的尺寸为第三尺寸,第二尺寸大于或等于第三尺寸。

6、可选的,第一尺寸大于200纳米。

7、可选的,离子掺杂区内的掺杂离子包括硼离子、碳离子或锗离子中的一种。

8、可选的,对第一材料层进行离子注入之前,还包括:在第一材料层上形成初始掩膜层,初始掩膜层内具有掩膜开口,掩膜开口暴露出部分第一材料层表面。

9、可选的,去除牺牲结构的工艺包括湿法刻蚀工艺。

10、可选的,湿法刻蚀工艺中采用的刻蚀液包括碱性溶液。

11、可选的,以第一掩膜结构为掩膜刻蚀第一材料层的工艺为干法刻蚀工艺。

12、可选的,形成第一掩膜结构的方法包括:在形成离子掺杂区后,形成位于第一材料层上的第一芯轴结构;在第一芯轴结构侧壁和顶部表面沉积第一掩膜材料层;回刻蚀第一芯轴结构顶部表面的第一掩膜材料层,以形成位于第一芯轴结构侧壁表面的第一掩膜结构;去除第一芯轴结构。

13、可选的,形成第一掩膜结构的方法包括:在形成离子掺杂区后,形成位于第一材料层上的初始材料层;对初始材料层进行图形化,以形成第一掩膜结构。

14、可选的,衬底包括:基底以及位于基底上的层间介质层。

15、可选的,在去除牺牲结构之后,还包括:以第二侧墙结构和离子掺杂区为掩膜,刻蚀层间介质层,以形成位于基底上的若干隔离结构和位于各隔离结构之间的隔离间隙。

16、可选的,半导体结构的形成方法还包括:在各隔离间隙内形成电互连结构。

17、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

18、本发明的技术方案提供的半导体结构的形成方法中,在形成第一掩膜结构之前,先在第一材料层内形成了若干离子掺杂区,且后续形成的各第一掩膜结构至少位于各离子掺杂区的部分表面,因此,后续以第一掩膜结构为掩膜,刻蚀第一材料层,形成若干第二芯轴结构之后,第二芯轴结构包括的离子掺杂区和周围的牺牲结构的材料不同,可以通过选择性地去除牺牲结构,保留离子掺杂区。一方面,离子掺杂区和第二侧墙结构共同构成的图形决定了后续形成的金属线的图案,使其突破了传统四重自对准工艺形成的连续型结构,增加了图案的灵活性;另一方面,对于较宽尺寸的图案形成,相比传统的光刻工艺进行的图形化过程,通过离子掺杂的方式进行图形化,能够减少宽尺寸图案的图形化对相邻结构的影响,使工艺窗口更大,且工艺难度更小。

19、进一步,离子掺杂区在垂直于第一方向上的尺寸为第二尺寸,第一掩膜结构在垂直于第一方向上的尺寸为第三尺寸,第二尺寸大于或等于第三尺寸。在后续形成第二芯轴结构的过程中,可以通过刻蚀第一材料层,将离子掺杂区的第二尺寸减薄,直至达到第三尺寸,因此,对第一材料层进行离子注入而形成的离子掺杂区的第二尺寸可以大于或等于第三尺寸,相比于传统的光刻工艺进行的图形化过程,离子掺杂区的形成过程的工艺窗口更大,对初始掩膜层的形成过程中的光刻工艺要求更低,降低了工艺难度和成本。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,各所述第一掩膜结构在所述第一材料层表面的投影图形为第一图形,各离子掺杂区仅与一个第一图形有交集。

3.如权利要求1所述的半导体结构的形成方法,其特征在于,各离子掺杂区的第一尺寸相同或不同。

4.如权利要求1所述的半导体结构的形成方法,其特征在于,各所述第一掩膜结构在垂直于所述第一方向的第二方向上的尺寸为第三尺寸,所述第二尺寸大于或等于第三尺寸。

5.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一尺寸大于200纳米。

6.如权利要求1所述的半导体结构的形成方法,其特征在于,所述离子掺杂区内的掺杂离子包括硼离子、碳离子或锗离子中的一种。

7.如权利要求1所述的半导体结构的形成方法,其特征在于,对第一材料层进行离子注入之前,还包括:在所述第一材料层上形成初始掩膜层,所述初始掩膜层内具有掩膜开口,所述掩膜开口暴露出部分所述第一材料层表面。

8.如权利要求1所述的半导体结构的形成方法,其特征在于,去除所述牺牲结构的工艺包括湿法刻蚀工艺。

9.如权利要求8所述的半导体结构的形成方法,其特征在于,所述湿法刻蚀工艺中采用的刻蚀液包括碱性溶液。

10.如权利要求1所述的半导体结构的形成方法,其特征在于,以所述第一掩膜结构为掩膜刻蚀所述第一材料层的工艺为干法刻蚀工艺。

11.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述第一掩膜结构的方法包括:在形成离子掺杂区后,形成位于所述第一材料层上的第一芯轴结构;在所述第一芯轴结构侧壁和顶部表面沉积第一掩膜材料层;回刻蚀所述第一芯轴结构顶部表面的第一掩膜材料层,以形成位于第一芯轴结构侧壁表面的第一掩膜结构;去除所述第一芯轴结构。

12.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述第一掩膜结构的方法包括:在形成离子掺杂区后,形成位于所述第一材料层上的初始材料层;对所述初始材料层进行图形化,以形成第一掩膜结构。

13.如权利要求1所述的半导体结构的形成方法,其特征在于,所述衬底包括:基底以及位于基底上的层间介质层。

14.如权利要求13所述的半导体结构的形成方法,其特征在于,在去除所述牺牲结构之后,还包括:以所述第二侧墙结构和离子掺杂区为掩膜,刻蚀所述层间介质层,以形成位于基底上的若干隔离结构和位于各隔离结构之间的隔离间隙。

15.如权利要求14所述的半导体结构的形成方法,其特征在于,还包括:在各隔离间隙内形成电互连结构。

技术总结

一种半导体结构的形成方法,包括:提供衬底;在衬底上形成第一材料层;对第一材料层进行离子注入,形成位于第一材料层内的离子掺杂区,离子掺杂区平行于第一方向上的尺寸为第一尺寸,第一方向平行于衬底表面,离子掺杂区在垂直于第一方向上的尺寸为第二尺寸,第一尺寸大于或等于第二尺寸;在第一材料层上形成若干第一掩膜结构,各第一掩膜结构至少位于各离子掺杂区的部分表面;以第一掩膜结构为掩膜,刻蚀第一材料层,以形成若干第二芯轴结构,各第二芯轴结构包括离子掺杂区以及与离子掺杂区相邻的牺牲结构;在各第二芯轴结构侧壁形成第二侧墙结构;去除牺牲结构。所述半导体结构的形成方法提升了结构图案的灵活性,改善了工艺窗口和兼容性。

技术研发人员:吴轶超

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!