一种提高氮化镓器件击穿电压的器件结构及制作方法与流程

本发明属于半导体器件,尤其涉及一种提高氮化镓器件击穿电压的器件结构及制作方法。

背景技术:

1、近年来,氮化镓器件的研发和产业化越来越受到重视,氮化镓器件由于其高功率、高频、高压、高温及抗辐射等性能,在电力电子、微电子等高新技术信息产业和能源产业等领域具有巨大的发展潜力和市场前景。器件结构设计是芯片生产的一个重要环节,优良的器件性能可以通过器件结构设计和工艺制造优化来实现。氮化镓材料有电子迁移率高,击穿电场强度大等特点,氮化镓功率器件市场发展非常迅速。

2、但是氮化镓本身起步比较晚,目前氮化镓器件主要是在硅,蓝宝石,和碳化硅等衬底材料上外延生长氮化镓制造的。考虑到材料成本,氮化镓/硅衬底是氮化镓功率器件的主流产品。虽然氮化镓的击穿电场强度很高,但是硅衬底的击穿电场强度不高,所以硅衬底限制了氮化镓的高压性能。当然有一种提高击穿电压的办法,就是增加氮化镓外延层厚度,氮化镓缓冲层/沟道层的击穿电场强度大概在2-3mv/cm,即200-300v/μm。但是外延层厚度增加,材料应力也相应增加,晶圆的翘曲度就会增加,裂纹和缺陷增多,从而影响成品率和生产成本。相关技术通过外延9μm厚的氮化镓外延结构,使得硅衬底氮化镓功率器件获得1813v击穿电压,虽然增加氮化镓外延层厚度可以提高击穿电压,但是,发明人认为,这同时也大大增加了外延时间和成本。相关技术采用背面硅衬底剥离方法,在源漏有源区背面开孔,选择性地剥离硅衬底,获得3000v的氮化镓/硅衬底功率器件击穿电压,发明人认为,这个方法虽然提高了击穿电压,但是工艺过程非常复杂,成本很高,成品率低。鉴于以上原因,需要设计出一种提高氮化镓器件击穿电压的器件结构及制作方法。

3、需要说明的是,在上述背景技术部分公开的信息仅用于加强理解本公开的背景,并且因此可以包括不构成现有技术的信息。

技术实现思路

1、发明人通过研究发现,因为硅衬底的击穿电场强度不高,限制了氮化镓的高压性能,使得氮化镓器件存在无法以较低的成本,提高氮化镓器件击穿电压的技术问题。

2、鉴于以上技术问题中的至少一项,本公开提供了的一种提高氮化镓器件击穿电压的器件结构及制作方法,具体技术方案如下:

3、一种提高氮化镓器件击穿电压的器件结构,包括衬底,所述衬底上方外延有缓冲层,缓冲层上方外延有p型gan外延层,p型gan外延层上方外延有高质量氮化镓沟道材料层,高质量氮化镓沟道材料层上方外延有aln隔离层,aln隔离层上方外延有algan势垒层,通过具有衬底p-gan反向pin结构的氮化镓hemt器件,在衬底上生长氮化镓缓冲层后,在缓冲层上增加一层p-gan,然后继续生长无掺杂高纯度氮化镓沟道材料层,再生长aln隔离层、algan势垒层,这一层p-gan与后续生长的i-gan以及algan,相当于构建了一个耐压非常高的反向pin结构,本发明工艺简单,只是增加一层p-gan外延生长,却可以大大提高器件击穿电压,有很大的市场应用价值。

4、在本公开的一些实施例中,衬底为蓝宝石、硅、碳化硅或氮化镓,衬底为可以用来外延氮化镓薄膜的材料。

5、在本公开的一些实施例中,缓冲层为氮化镓层或氮化铝层,其质量直接影响随后生长的异质结的质量。

6、在本公开的一些实施例中,p型gan外延层的厚度在20nm~1000nm。

7、在本公开的一些实施例中,algan势垒层上表面沉积有源漏欧姆接触金属和栅金属。

8、在本公开的一些实施例中,algan势垒层外延生长有帽层,algan势垒层上沉积有源漏欧姆接触金属,帽层上沉积有栅金属。

9、在本公开的一些实施例中,algan势垒层外延生长有帽层,algan势垒层上沉积有源漏欧姆接触金属,帽层上沉积二氧化硅或氮化硅栅绝缘层,然后在上方沉积有栅金属。

10、在本公开的一些实施例中,帽层为氮化硅、n型氮化镓或p型氮化镓,具体可根据器件需要选择。

11、一种提高氮化镓器件击穿电压的器件结构的制作方法,用于制作上述的提高氮化镓器件击穿电压的器件结构,具体步骤为,在衬底上低温生长缓冲层,在缓冲层上通过mocvd技术,在tmg和nh3,以及n2,h2和cp2mg环境下依次外延生长p型gan外延层,高质量氮化镓沟道材料层,aln隔离层,algan势垒层,algan势垒层上方沉积有帽层和源漏欧姆接触金属。

12、在本公开的一些实施例中,p型gan外延层的生长温度为800~1000c。

13、相比较现有技术而言,本发明具有以下有益效果:

14、1.本发明提出一种新的氮化镓功率器件结构:具有衬底p-gan反向pin结构的氮化镓hemt器件,在衬底上生长缓冲层后,在缓冲层上增加一层p-gan,然后继续生长无掺杂高纯度氮化镓沟道材料层,再生长aln隔离层、algan势垒层,这一层p-gan与后续生长的i-gan以及algan,相当于构建了一个耐压非常高的反向pin结构。

15、2.本发明提出的衬底反向pin结构hemt,与常规hemt器件结构变化很小,只是增加一层p-gan外延层,工艺简单,重复性好,几乎不增加材料成本,可以在现有氮化镓hemt器件的击穿电压基础上提高将近1倍,提高器件的稳定性和可靠性,并且提高成品率,降低器件生产成本,能够充分发挥氮化镓功率器件高频、高击穿电压、高电流密度等特点,可以大大提高器件击穿电压,具有巨大的市场应用价值,可以广泛应用于氮化镓功率器件,射频器件的生产制造。

技术特征:

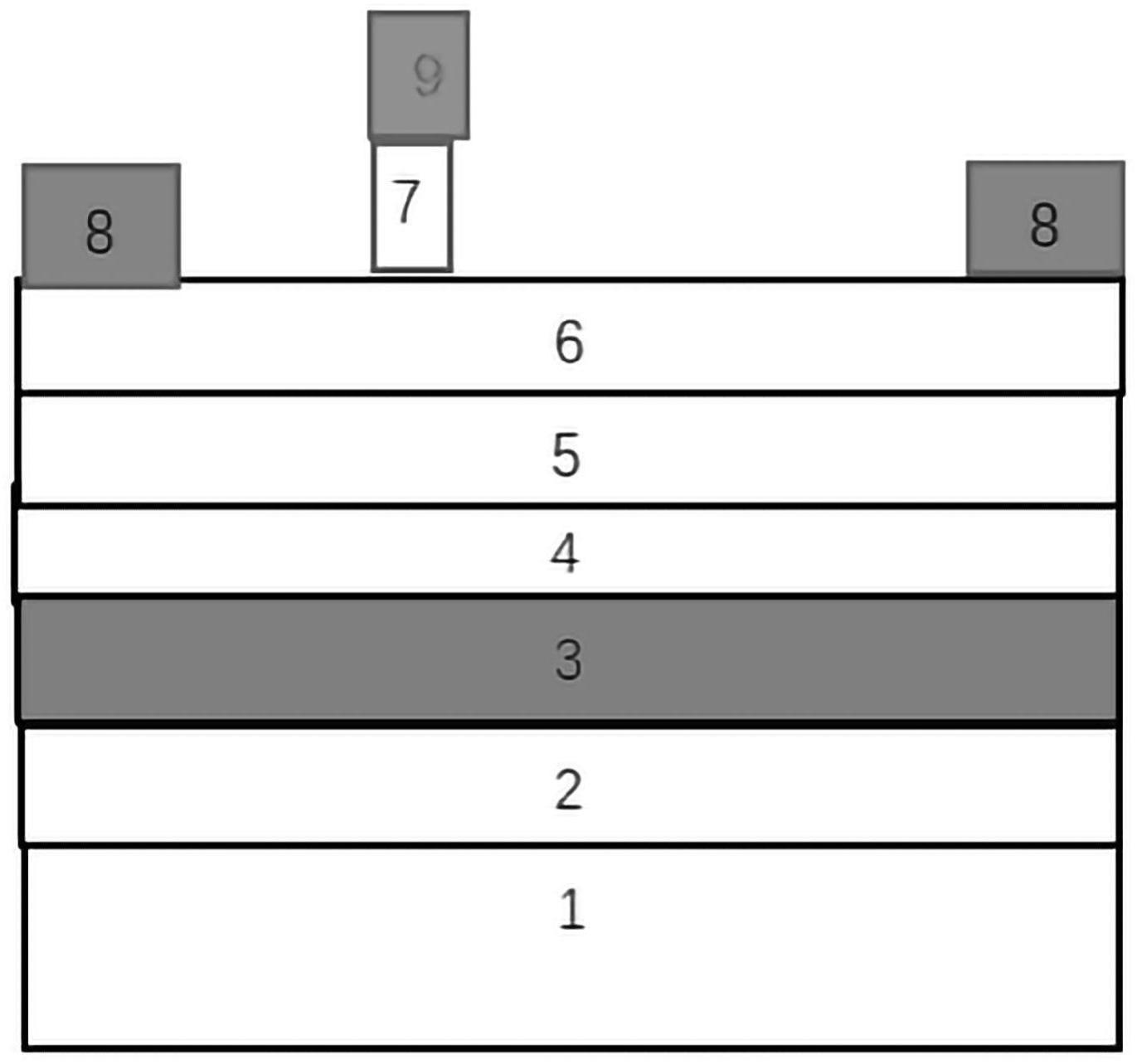

1.一种提高氮化镓器件击穿电压的器件结构,包括衬底(1),其特征在于:所述衬底(1)上方外延有缓冲层(2),缓冲层(2)上方外延有p型gan外延层(3),p型gan外延层(3)上方外延有高质量氮化镓沟道材料层(4),高质量氮化镓沟道材料层(4)上方外延有aln隔离层(5),aln隔离层(5)上方外延有algan势垒层(6)。

2.根据权利要求1所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述衬底(1)为蓝宝石、硅、碳化硅或氮化镓。

3.根据权利要求1所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述缓冲层(2)为氮化镓层或氮化铝层。

4.根据权利要求1所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述p型gan外延层(3)的厚度在20nm~1000nm。

5.根据权利要求1所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述algan势垒层(6)上表面沉积有源漏欧姆接触金属(8)和栅金属(9)。

6.根据权利要求1所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述algan势垒层(6)外延生长有帽层(7),algan势垒层(6)上沉积有源漏欧姆接触金属(8),帽层(7)上沉积有栅金属(9)。

7.根据权利要求1所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述algan势垒层(6)外延生长有帽层(7),algan势垒层(6)上沉积有源漏欧姆接触金属(8),帽层(7)上沉积二氧化硅或氮化硅栅绝缘层,然后在上方沉积有栅金属(9)。

8.根据权利要求6或8中任意一项所述的提高氮化镓器件击穿电压的器件结构,其特征在于,所述帽层(7)为氮化硅、n型氮化镓或p型氮化镓。

9.一种提高氮化镓器件击穿电压的器件结构的制作方法,其特征在于,用于制作权利要求1所述的提高氮化镓器件击穿电压的器件结构,具体步骤为,在衬底(1)上以600~800℃生长缓冲层(2),在缓冲层(2)上通过mocvd技术,在tmg和nh3,以及n2,h2和cp2mg环境下依次外延生长p型gan外延层(3),高质量氮化镓沟道材料层(4),aln隔离层(5),algan势垒层(6)。

10.根据权利要求9所述的提高氮化镓器件击穿电压的器件结构的制作方法,其特征在于,所述p型gan外延层(3)的生长温度为800~1000c。

技术总结

本发明公开了一种提高氮化镓器件击穿电压的器件结构及制作方法,包括衬底,所述衬底上方外延有缓冲层,缓冲层上方外延有P型GaN外延层,P型GaN外延层上方外延有高质量氮化镓沟道材料层,高质量氮化镓沟道材料层上方外延有AlN隔离层,AlN隔离层上方外延有AlGaN势垒层,本发明通过在缓冲层上增加一层P‑GaN,形成具有P‑GaN反向PIN结构的氮化镓HEMT器件,然后继续生长无掺杂高纯度氮化镓沟道材料层,再生长AlN隔离层、AlGaN势垒层,这一层P‑GaN与后续生长的i‑GaN以及AlGaN,相当于构建了一个耐压非常高的反向PIN结构,工艺简单,只是增加一层P‑GaN外延生长,却可以大大提高器件击穿电压,有很大的市场应用价值。

技术研发人员:胡旭宏

受保护的技术使用者:江苏镓宏半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!