半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、随着半导体工艺技术的逐步发展,半导体工艺节点遵循摩尔定律的发展趋势不断减小。为了适应工艺节点的减小,mosfet场效应管的沟道长度也相应不断缩短。然而随着器件沟道长度的缩短,器件源极与漏极间的距离也随之缩短,因此栅极对沟道的控制能力变差,栅极电压夹断(pinch off)沟道的难度也越来越大,使得亚阈值漏电(subthresholdleakage)现象,即所谓的短沟道效应(sce:short-channel effects)更容易发生。

2、因此,为了更好的适应器件尺寸按比例缩小的要求,半导体工艺逐渐开始从平面mosfet向具有更高功效的三维立体式的晶体管过渡,如鳍式场效应晶体管(fin field-effect transistor,finfet)。finfet中,栅极至少可以从两侧对超薄体(鳍部)进行控制,与平面mosfet相比,栅极对沟道的控制能力更强,能够很好的抑制短沟道效应;且finfet相对于其他器件,与现有集成电路制造具有更好的兼容性。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法,提高半导体结构的性能。

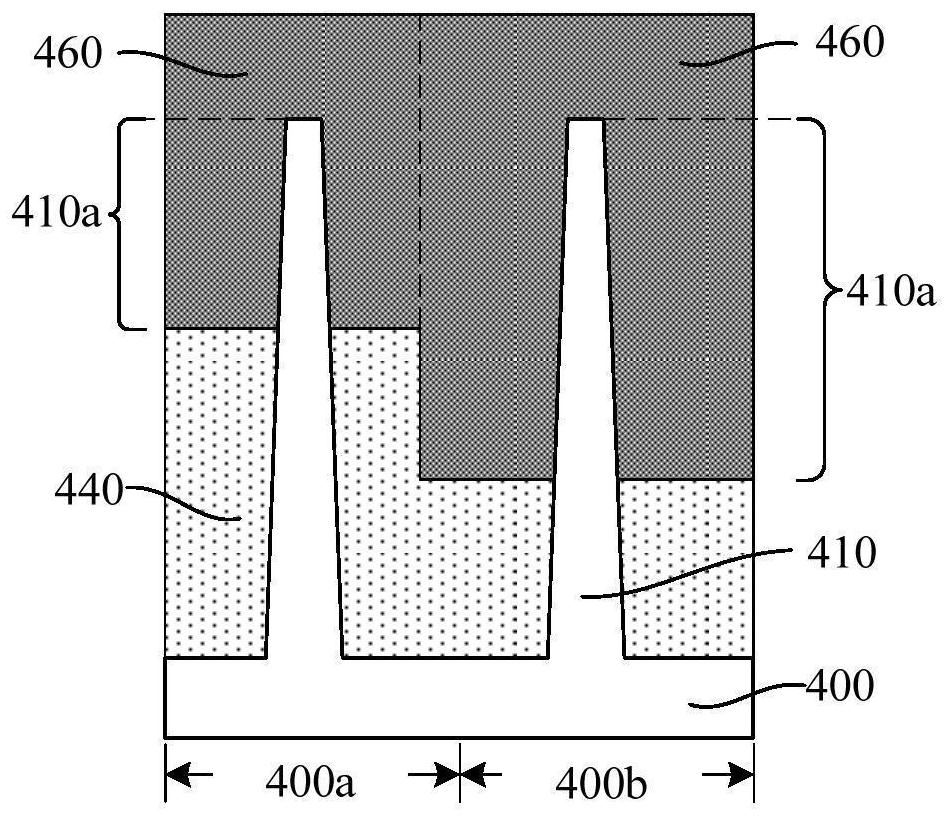

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:衬底,包括第一区域和第二区域,所述第一区域的器件驱动电流与所述第二区域的器件驱动电流存在差异;鳍部,位于所述第一区域和第二区域的衬底上;隔离层,位于所述鳍部露出的衬底上并覆盖所述鳍部的部分侧壁,所述隔离层的顶面低于所述鳍部的顶面;器件栅极结构,位于所述隔离层上、且分别横跨所述第一区域和第一区域的鳍部,所述器件栅极结构覆盖所述鳍部的部分顶部和部分侧壁;侧墙,位于所述器件栅极结构的两侧,并覆盖所述器件栅极结构的侧壁;源漏掺杂层,位于所述鳍部的两端内且邻近所述侧墙一侧;其中,所述第一区域的器件栅极结构覆盖的鳍部面积,与所述第二区域的器件栅极结构覆盖的鳍部的面积不同。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括第一区域和第二区域,所述第一区域的器件驱动电流与所述第二区域的器件驱动电流存在差异;形成位于所述衬底上的鳍部、以及位于所述鳍部露出的衬底上的隔离层,所述隔离层覆盖所述鳍部的部分侧壁,所述隔离层的顶面低于所述鳍部的顶面;在所述隔离层上形成分别横跨所述第一区域和第一区域的鳍部的器件栅极结构,所述器件栅极结构覆盖所述鳍部的部分顶部和部分侧壁,所述第一区域的器件栅极结构覆盖的鳍部面积,与所述第二区域的器件栅极结构覆盖的鳍部的面积不同。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供的半导体结构中,衬底包括第一区域和第二区域,第一区域的器件驱动电流与第二区域的器件驱动电流存在差异,所述第一区域的器件栅极结构覆盖的鳍部面积,与所述第二区域的器件栅极结构覆盖的鳍部的面积不同;其中,增加被器件栅极结构覆盖的鳍部面积能够增加器件的驱动电流(drive current),因此,通过使第一区域和第二区域中被器件栅极结构覆盖的鳍部面积不同,易于在满足各区域的器件的驱动电流的同时,不增大第一区域和第二区域的鳍部间的正对面积,从而抑制寄生电容的增加,进而提高半导体结构的性能。

6、可选方案中,所述鳍部中高于所述隔离层顶部的部分作为沟道鳍部,所述第一区域的沟道鳍部高度与所述第二区域的沟道鳍部高度不相同,或者,所述第一区域的鳍部高度与所述第二区域的鳍部高度相同,且所述第一区域的器件栅极结构覆盖所述沟道鳍部的深度,与所述第二区域的器件栅极结构覆盖所述沟道鳍部的深度不相同;其中,增加沟道鳍部的高度能够增加器件的驱动电流,从而有利于降低功耗、提高器件性能,因此本发明实施例使第一区域和第二区域的沟道鳍部高度不同,或者,被栅极结构覆盖的沟道鳍部深度不同,能够满足各区域的器件的驱动电流;同时,根据不同区域的器件的驱动电流大小,使第一区域和第二区域的沟道鳍部具有高度差,或者,使器件栅极结构覆盖的沟道鳍部的深度具有差异,有利于不增大第一区域和第二区域的鳍部之间的正对面积,从而有利于抑制寄生电容的增加,进而提高半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述鳍部中高于所述隔离层顶部的部分作为沟道鳍部,所述第一区域的沟道鳍部高度与所述第二区域的沟道鳍部高度不相同;

3.如权利要求2所述的半导体结构,其特征在于,所述第一区域的沟道鳍部为一体结构,所述第二区域的沟道鳍部为一体结构。

4.如权利要求2所述的半导体结构,其特征在于,所述第一区域的器件驱动电流大于所述第二区域的器件驱动电流;

5.如权利要求4所述的半导体结构,其特征在于,当所述第一区域的沟道鳍部顶面高于所述第二区域的沟道鳍部顶面,所述第一区域的器件栅极结构的顶面高于所述第二区域的器件栅极结构的顶面;

6.如权利要求5所述的半导体结构,其特征在于,所述第一区域的器件栅极结构的顶面高于所述第二区域的器件栅极结构的顶面;

7.如权利要求6所述的半导体结构,其特征在于,所述填充介质层的材料包括氧化硅、氮化硅、碳化硅、碳氮化硅、碳氮氧化硅、氮氧化硅、氮化硼和碳氮化硼中的一种或多种。

8.如权利要求1~7中任一项所述的半导体结构,其特征在于,所述器件栅极结构为金属栅极结构。

9.一种半导体结构的形成方法,其特征在于,包括:

10.如权利要求9所述的半导体结构的形成方法,其特征在于,所述鳍部中高于所述隔离层顶部的部分作为沟道鳍部,所述第一区域的沟道鳍部高度与所述第二区域的沟道鳍部高度不相同;

11.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一区域的沟道鳍部为一体结构,所述第二区域的沟道鳍部为一体结构。

12.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一区域的器件驱动电流大于所述第二区域的器件驱动电流;

13.如权利要求12所述的半导体结构的形成方法,其特征在于,形成位于所述鳍部露出的衬底上的隔离层的步骤包括:在所述鳍部露出的衬底上形成初始隔离层,所述初始隔离层覆盖所述鳍部的侧壁;

14.如权利要求13所述的半导体结构的形成方法,其特征在于,去除所述第一区域的第一预设厚度的初始隔离层、以及所述第二区域的第二预设厚度的初始隔离层的步骤包括:去除所述第一区域中的第三预设厚度的初始隔离层,所述第三预设厚度等于所述第一区域和第二区域的沟道鳍部的高度差;

15.如权利要求14所述的半导体结构的形成方法,其特征在于,去除所述第一区域中的第三预设厚度的初始隔离层的步骤包括:形成覆盖所述第二区域的第一掩膜层;

16.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一区域的器件驱动电流大于所述第二区域的器件驱动电流;

17.如权利要求16所述的半导体结构的形成方法,其特征在于,形成所述鳍部和隔离层之前,所述形成方法还包括:形成位于所述衬底上的初始鳍部;

18.如权利要求17所述的半导体结构的形成方法,其特征在于,形成所述隔离层的步骤包括:在所述初始鳍部露出的衬底上形成隔离层,所述隔离层覆盖所述初始鳍部的部分侧壁,所述隔离层的顶面低于所述初始鳍部的顶面;

19.如权利要求17所述的半导体结构的形成方法,其特征在于,去除所述第二区域中的部分高度的初始鳍部之前,还包括:在所述隔离层上形成覆盖所述初始鳍部的第二掩膜层;去除所述第二区域的部分厚度的第二掩膜层,以暴露部分高度的初始鳍部;

20.如权利要求18所述的半导体结构的形成方法,其特征在于,去除所述第二区域中的部分高度的初始鳍部的步骤包括:在所述第二区域中,对待去除的部分高度的初始鳍部进行氧化处理,将所述部分高度的初始鳍部转化为牺牲层;去除所述牺牲层。

21.如权利要求20所述的半导体结构的形成方法,其特征在于,所述氧化处理包括湿法氧化处理,所述湿法氧化处理的参数包括:处理温度小于200摄氏度,处理溶液包括双氧水或臭氧水溶液。

22.如权利要求20所述的半导体结构的形成方法,其特征在于,去除所述牺牲层的工艺包括湿法刻蚀工艺。

23.如权利要求16所述的半导体结构的形成方法,其特征在于,形成所述器件栅极结构的步骤中,所述第一区域的器件栅极结构的顶面高于所述第二区域的器件栅极结构的顶面。

24.如权利要求23所述的半导体结构的形成方法,其特征在于,形成所述第二区域的器件栅极结构的步骤包括:形成横跨所述第二区域的鳍部的初始器件栅极结构,所述初始器件栅极结构和第一区域的器件栅极结构的顶部相齐平;

25.如权利要求22所述的半导体结构的形成方法,其特征在于,所述形成方法还包括:形成覆盖所述第二区域的器件栅极结构顶部的填充介质层,所述填充介质层的顶面和所述第一区域的器件栅极结构的顶面相齐平。

26.如权利要求24所述的半导体结构的形成方法,其特征在于,形成覆盖所述第二区域的器件栅极结构顶部的填充介质层的步骤包括:形成覆盖所述第二区域的器件栅极结构顶部的填充介质材料层;

技术总结

一种半导体结构及其形成方法,半导体结构包括:衬底,包括第一区域和第二区域,第一区域的器件驱动电流与第二区域的器件驱动电流存在差异;鳍部,位于衬底上;隔离层,位于鳍部露出的衬底上并覆盖鳍部的部分侧壁;器件栅极结构,分别横跨第一区域和第一区域的鳍部;侧墙,位于器件栅极结构的两侧并覆盖器件栅极结构的侧壁;源漏掺杂层,位于鳍部的两端内且邻近侧墙一侧;其中,第一区域的器件栅极结构覆盖的鳍部面积,与第二区域的器件栅极结构覆盖的鳍部的面积不同。本发明使被器件栅极结构覆盖的鳍部面积不同,易于在满足各区域的器件的驱动电流的同时,不增大第一区域和第二区域的鳍部间的正对面积,从而抑制寄生电容的增加。

技术研发人员:韩静利,于海龙

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!