半导体结构及其制备方法、电子设备与流程

本申请涉及半导体,尤其涉及一种半导体结构及其制备方法、电子设备。

背景技术:

1、随着电子技术的发展,电子设备的功能不断的区域丰富化、全面化,也趋使电子设备内的集成电路向小型化和密集化发展。

2、为了提高集成电路的封装密度以及实现集成电路小型化,就需要将集成电路上的半导体设计的更小。

3、然而,半导体结构的尺寸减小会带来半导体结构的性能降低等问题,导致集成电路的性能降低。

技术实现思路

1、本申请实施例提供一种半导体结构及其制备方法、电子设备,用于降低半导体结构的寄生电容。

2、为达到上述目的,本申请采用如下技术方案:

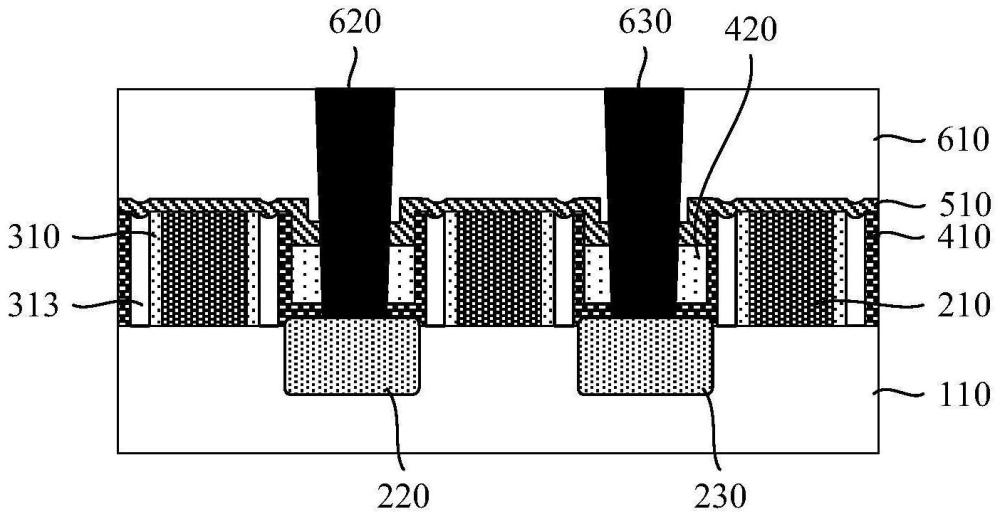

3、本申请实施例的第一方面,提供一种半导体结构,半导体结构包括设置在衬底上的栅极、源极、漏极、位于栅极侧面的第一介电层以及层间介电层。其中,第一介电层还延伸至源极和漏极的顶面,且第一介电层和栅极的至少一个侧面之间具有空隙。层间介电层设置在第一介电层远离源极和漏极一侧。半导体结构还包括贯穿层间介电层和第一介电层、且与源极接触的源极接触部,以及贯穿层间介电层和第一介电层、且与漏极接触的漏极接触部。

4、本申请实施例提供的半导体结构,第一介电层与栅极之间具有空隙,可以使源极接触部或者漏极接触部与栅极之间也具有空隙。相比于其他填充材料,空隙的介电常数较低,也就是说在源极接触部或者漏极接触部与栅极之间存在较低的介电常数材料,因此,降低了源极接触部和漏极接触部与栅极之间材料的介电常数,进而降低了源极接触部和漏极接触部与栅极之间产生的寄生电容,降低了由于寄生电容造成的阻容延迟,从而提高半导体结构的性能。

5、在一种可能实现的方式中,半导体结构还包括保护层;保护层覆盖在空隙的上方。这样一来,有利于在源极接触部或者漏极接触部与栅极之间形成空隙。

6、在一种可能实现的方式中,保护层还延伸至层间介电层上;保护层设置在层间介电层远离源极和漏极的表面,且位于源极接触部和漏极接触部的外围。这样一来,保护层可以避免层间介电层受到破坏。

7、在一种可能实现的方式中,保护层的厚度大于或者等于空隙的尺寸。这样一来,能够避免保护层的材料填充至空隙内。

8、在一种可能实现的方式中,栅极靠近源极接触部一侧设置有空隙。这样一来,能够降低栅极与源极接触部之间产生的寄生电容。

9、在一种可能实现的方式中,栅极靠近漏极接触部一侧设置有空隙。这样一来,能够降低栅极与漏极接触部之间产生的寄生电容。

10、在一种可能实现的方式中,空隙位于衬底的上方。结构简单,易于制作。

11、在一种可能实现的方式中,空隙的高度小于或者等于栅极的高度。这样一来,空隙存在于栅极的至少一个侧面。

12、在一种可能实现的方式中,半导体结构还包括栅极侧墙,栅极侧墙包裹在栅极的侧面;空隙位于栅极侧墙远离栅极一侧。这样一来,栅极侧墙用于保护栅极。

13、在一种可能实现的方式中,半导体结构还包括第二介电层,第二介电层覆盖栅极和层间介电层的表面,且位于源极接触部和漏极接触部的外围。这样一来,第二介电层用于隔离半导体结构内的第一层金属与衬底。

14、在一种可能实现的方式中,空隙内填充有空气或者惰性气体。这样一来,能够有效降低源极接触部或者漏极接触部与栅极之间材料的介电常数。

15、在一种可能实现的方式中,第一介电层的材料与层间介电层的材料具有不同的刻蚀选择比。这样一来,在减薄层间介电层材料时,能够避免破坏第一介电层材料。

16、在一种可能实现的方式中,第一介电层的材料包括氮化硅。这样一来,第一介电层作为接触孔刻蚀阻挡层,还用于保护衬底的有源区。

17、在一种可能实现的方式中,层间介电层的材料包括氧化硅。这样一来,层间介电层可以作为半导体结构中的第一层金属与衬底的隔离结构。

18、本申请实施例的第二方面,提供一种半导体结构的制备方法,包括:形成位于衬底上的栅极和栅极介电层;栅极介电层设置在栅极的侧面;形成位于衬底上的源极和漏极,源极和漏极位于栅极相对的两侧;形成第一介电层,第一介电层覆盖栅极的侧面以及源极和漏极的顶面;形成层间介电层,层间介电层设置在第一介电层远离源极和漏极一侧;去除至少部分栅极介电层,以使第一介电层与栅极的至少一个侧面之间具有空隙;形成源极接触部和漏极接触部;源极接触部贯穿层间介电层和第一介电层与源极接触;漏极接触部贯穿层间介电层和第一介电层与漏极接触。

19、本申请实施例提供的半导体结构的制备方法,使第一介电层与栅极之间形成有空隙,可以使源极接触部或者漏极接触部与栅极之间也形成有空隙。也就是说在源极接触部或者漏极接触部与栅极之间存在介电常数较低的空隙,因此,降低了源极接触部和漏极接触部与栅极之间材料的介电常数,进而降低了源极接触部和漏极接触部与栅极之间产生的寄生电容,降低了由于寄生电容造成的阻容延迟,从而提高半导体结构的性能。

20、在一种可能实现的方式中,形成栅极介电层,包括:利用原子层沉积工艺形成栅极介电层。这样一来,能够在栅极侧面形成均匀的栅极介电层。

21、在一种可能实现的方式中,去除至少部分栅极介电层之前,制备方法还包括:形成第一保护膜,第一保护膜覆盖栅极、栅极介电层以及层间介电层的表面;去除栅极和栅极介电层上的第一保护膜,形成第一保护层;第一保护层覆盖层间介电层远离源极和漏极的表面。这样一来,可以避免在去除至少部分栅极介电层时破坏层间介电层。

22、在一种可能实现的方式中,去除部分栅极介电层之后,制备方法还包括:形成第二保护层,第二保护层覆盖栅极远离衬底的表面,第二保护层还延伸至空隙的上方;第一保护层和第二保护层构成保护层。这样一来,有利于形成空隙,同时避免后续制备工艺过程中填充空隙。

23、在一种可能实现的方式中,形成源极接触部和漏极接触部之前,制备方法还包括:形成第二介电层,第二介电层覆盖栅极、剩余栅极介电层以及层间介电层的表面;形成源极接触部和漏极接触部,包括:源极接触部从第二介电层的表面贯穿至第一介电层,与源极接触;漏极接触部从第二介电层的表面贯穿至第一介电层,与漏极接触。这样一来,形成第二介电层以隔离半导体结构中的第一层金属和衬底。

24、本申请实施例的第三方面,提供一种电子设备,包括集成电路和印刷线路板,集成电路与印刷线路板电连接;集成电路包括第一方面任一项的半导体结构。

25、本申请实施例第三方面提供的电子设备,包括第一方面任一项的半导体结构,其有益效果与半导体结构的有益效果相同,此处不再赘述。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括保护层;所述保护层覆盖在所述空隙的上方。

3.根据权利要求2所述的半导体结构,其特征在于,所述保护层还延伸至所述层间介电层上;所述保护层设置在所述层间介电层远离所述源极和所述漏极的表面,且位于所述源极接触部和所述漏极接触部的外围。

4.根据权利要求2或3所述的半导体结构,其特征在于,所述保护层的厚度大于或者等于所述空隙的尺寸。

5.根据权利要求1-4任一项所述的半导体结构,其特征在于,

6.根据权利要求1-5任一项所述的半导体结构,其特征在于,所述空隙位于所述衬底的上方。

7.根据权利要求1-6任一项所述的半导体结构,其特征在于,所述空隙的高度小于或者等于所述栅极的高度。

8.根据权利要求1-7任一项所述的半导体结构,其特征在于,所述半导体结构还包括栅极侧墙,所述栅极侧墙包裹在所述栅极的侧面;所述空隙位于所述栅极侧墙远离所述栅极一侧。

9.根据权利要求1-8任一项所述的半导体结构,其特征在于,所述半导体结构还包括第二介电层,所述第二介电层覆盖所述栅极和所述层间介电层的表面,且位于所述源极接触部和所述漏极接触部的外围。

10.根据权利要求1-9任一项所述的半导体结构,其特征在于,所述空隙内填充有空气或者惰性气体。

11.根据权利要求1-10任一项所述的半导体结构,其特征在于,所述第一介电层的材料与所述层间介电层的材料具有不同的刻蚀选择比。

12.根据权利要求1-11任一项所述的半导体结构,其特征在于,所述第一介电层的材料包括氮化硅。

13.根据权利要求1-12任一项所述的半导体结构,其特征在于,所述层间介电层的材料包括氧化硅。

14.一种半导体结构的制备方法,其特征在于,包括:

15.根据权利要求14所述的半导体结构的制备方法,其特征在于,形成栅极介电层,包括:利用原子层沉积工艺形成所述栅极介电层。

16.根据权利要求14或15所述的半导体结构的制备方法,其特征在于,去除至少部分所述栅极介电层之前,所述制备方法还包括:

17.根据权利要求14-16任一项所述的半导体结构的制备方法,其特征在于,去除部分所述栅极介电层之后,所述制备方法还包括:

18.根据权利要求14-17任一项所述的半导体结构的制备方法,其特征在于,形成源极接触部和漏极接触部之前,所述制备方法还包括:

19.一种电子设备,其特征在于,包括集成电路和印刷线路板,所述集成电路与所述印刷线路板电连接;所述集成电路包括权利要求1-13任一项所述的半导体结构。

技术总结

本申请实施例提供一种半导体结构及其制备方法、电子设备,涉及半导体技术领域,用于降低半导体结构的寄生电容。半导体结构包括设置在衬底上的栅极、源极、漏极、位于栅极侧面的第一介电层以及层间介电层。其中,第一介电层还延伸至源极和漏极的顶面,且第一介电层和栅极的至少一个侧面之间具有空隙。层间介电层设置在第一介电层远离源极和漏极一侧。半导体结构还包括贯穿层间介电层和第一介电层、且与源极接触的源极接触部,以及贯穿层间介电层和第一介电层、且与漏极接触的漏极接触部。

技术研发人员:张峰溢

受保护的技术使用者:华为技术有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!