半导体装置及半导体装置的制造方法与流程

本发明涉及半导体装置及半导体装置的制造方法。

背景技术:

1、在专利文献1中公开了功率半导体装置的表面电极的构造。在该表面电极设置维氏硬度为200~350hv的以cu作为主要成分的通过化学镀而形成的第一cu层。在第一cu层之上层叠地设置比第一cu层柔软的维氏硬度为70~150hv的以cu作为主要成分的通过化学镀而形成的第二cu层。在第二cu层处导线键合cu制的导线。

2、专利文献1:日本特开2018-37684号公报

3、在专利文献1中,为了抑制导线键合时的对半导体芯片的损伤,作为表面电极而层叠有2层cu化学镀层。通常,在cu化学镀中,为了提高维氏硬度,需要提高杂质浓度。但是,如果提高杂质浓度,则有可能产生由杂质引起的空隙,有可能难以提高维氏硬度。因此,有可能无法充分地抑制对半导体芯片的损伤。

技术实现思路

1、本发明就是为了解决上述课题而提出的,其目的在于得到能够抑制对半导体基板的损伤的半导体装置及半导体装置的制造方法。

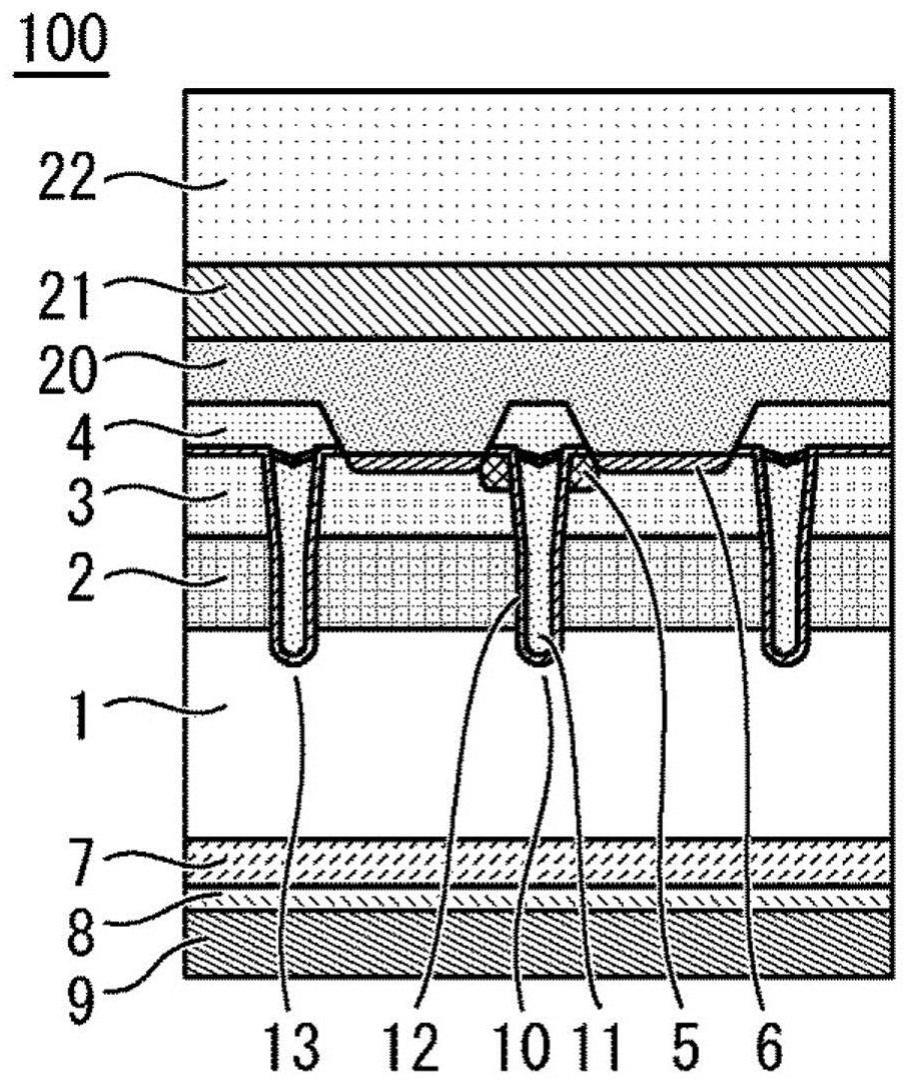

2、本发明涉及的半导体装置具有:半导体基板;第1金属层,其设置于所述半导体基板之上;第2金属层,其设置于所述第1金属层之上,材料包含ni;以及第3金属层,其设置于所述第2金属层之上,材料包含cu或ni,所述第2金属层的维氏硬度大于或等于400hv,比所述第3金属层硬,所述第3金属层比所述第1金属层硬。

3、本发明涉及的半导体装置的制造方法是,在半导体基板之上形成第1金属层,在所述第1金属层之上通过镀敷而形成材料包含ni的第2金属层,在所述第2金属层之上形成材料包含cu或ni的第3金属层,所述第2金属层的维氏硬度大于或等于400hv,比所述第3金属层硬,所述第3金属层比所述第1金属层硬。

4、发明的效果

5、就本发明涉及的半导体装置及半导体装置的制造方法而言,能够通过硬的第2金属层而抑制由导线键合等造成的对半导体基板的损伤。

技术特征:

1.一种半导体装置,其特征在于,具有:

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求1或2所述的半导体装置,其特征在于,

4.根据权利要求1至3中任一项所述的半导体装置,其特征在于,

5.根据权利要求4所述的半导体装置,其特征在于,

6.根据权利要求4或5所述的半导体装置,其特征在于,

7.根据权利要求6所述的半导体装置,其特征在于,

8.根据权利要求1至7中任一项所述的半导体装置,其特征在于,

9.根据权利要求1至7中任一项所述的半导体装置,其特征在于,

10.根据权利要求1至9中任一项所述的半导体装置,其特征在于,

11.根据权利要求10所述的半导体装置,其特征在于,

12.根据权利要求1至11中任一项所述的半导体装置,其特征在于,

13.根据权利要求12所述的半导体装置,其特征在于,

14.根据权利要求13所述的半导体装置,其特征在于,

15.根据权利要求1至12中任一项所述的半导体装置,其特征在于,

16.根据权利要求1至12中任一项所述的半导体装置,其特征在于,

17.根据权利要求1至16中任一项所述的半导体装置,其特征在于,具有:

18.根据权利要求1至17中任一项所述的半导体装置,其特征在于,

19.根据权利要求18所述的半导体装置,其特征在于,

20.一种半导体装置的制造方法,其特征在于,

技术总结

目的在于得到能够抑制对半导体基板的损伤的半导体装置及半导体装置的制造方法。本发明涉及的半导体装置具有:半导体基板;第1金属层,其设置于所述半导体基板之上;第2金属层,其设置于所述第1金属层之上,材料包含Ni;以及第3金属层,其设置于所述第2金属层之上,材料包含Cu或Ni,所述第2金属层的维氏硬度大于或等于400Hv,比所述第3金属层硬,所述第3金属层比所述第1金属层硬。

技术研发人员:田中香次,佐藤祐司,内田祥久,中村祥太郎

受保护的技术使用者:三菱电机株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!