晶体管元件及其制造方法与流程

本发明涉及一种半导体元件及其制造方法,且特别涉及一种晶体管元件及其制造方法。

背景技术:

1、目前,发展出一种屏蔽栅极沟槽式晶体管(shielded gate trench transistor),其可降低栅极与漏极之间的寄生电容且可改善晶体管元件的效能。一般而言,屏蔽栅极沟槽式晶体管包含栅极与位于栅极下方的屏蔽电极(shield electrode)。然而,由于位于栅极与基底之间的栅极介电层在栅极的底部的转角处会有偏薄的现象,因此位于栅极的底部的转角处的栅极介电层容易被击穿,而导致晶体管元件失效。

技术实现思路

1、本发明提供一种晶体管元件及其制造方法,其可有效地防止栅极介电层被击穿,进而防止晶体管元件失效。

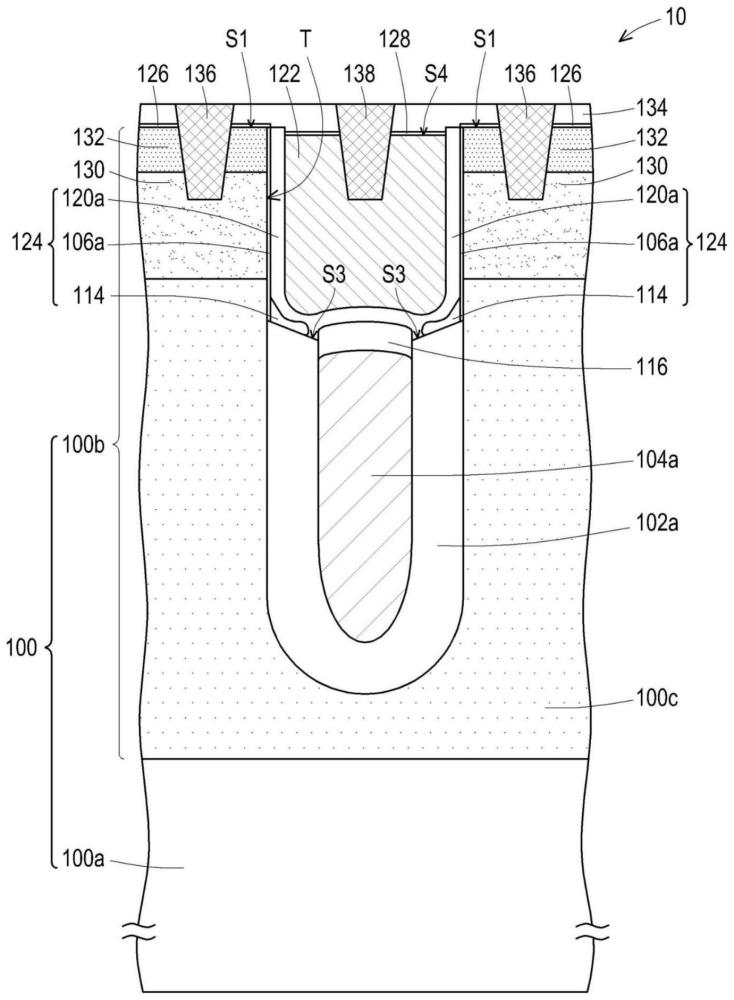

2、本发明提出一种晶体管元件,包括基底结构、屏蔽电极、第一介电层、栅极与栅极介电层。在基底结构中具有沟槽。屏蔽电极设置在沟槽中。第一介电层设置在屏蔽电极与基底结构之间。栅极设置在沟槽中与屏蔽电极上。栅极介电层设置在栅极与基底结构之间以及栅极与屏蔽电极之间。栅极介电层包括第二介电层与第三介电层。第二介电层设置在栅极的底部的转角与基底结构之间。第三介电层设置在栅极与基底结构之间、栅极与第二介电层之间以及栅极与屏蔽电极之间。

3、依照本发明的一实施例所述,在上述晶体管元件中,栅极介电层还可包括垫层。垫层设置在第二介电层与基底结构之间以及第三介电层与基底结构之间。

4、依照本发明的一实施例所述,在上述晶体管元件中,还可包括第四介电层。第四介电层设置在第三介电层与屏蔽电极之间。第二介电层与第四介电层可彼此分离。

5、依照本发明的一实施例所述,在上述晶体管元件中,还可包括第一掺杂区、第二掺杂区与基体区(body region)。第一掺杂区设置在栅极旁边的基底结构中。第二掺杂区设置在第一掺杂区下方的基底结构中。基体区设置在第一掺杂区与第二掺杂区之间的基底结构中。

6、依照本发明的一实施例所述,在上述晶体管元件中,基底结构可包括基底与半导体层。半导体层设置在基底上。沟槽可位于半导体层中。

7、本发明提出一种晶体管元件的制造方法,包括以下步骤。提供基底结构。在基底结构中形成沟槽。在沟槽中形成屏蔽电极。在屏蔽电极与基底结构之间形成第一介电层。在沟槽中与屏蔽电极上形成栅极。在栅极与基底结构之间以及栅极与屏蔽电极之间形成栅极介电层。栅极介电层包括第二介电层与第三介电层。第二介电层设置在栅极的底部的转角与基底结构之间。第三介电层设置在栅极与基底结构之间、栅极与第二介电层之间以及栅极与屏蔽电极之间。

8、依照本发明的一实施例所述,在上述晶体管元件的制造方法中,第二介电层的形成方法可包括以下步骤。在沟槽的侧壁上形成硅间隙壁。在硅间隙壁上形成间隙壁。间隙壁可暴露出硅间隙壁的底部。对由间隙壁所暴露出的硅间隙壁的底部进行热氧化制作工艺,而形成第二介电层。

9、依照本发明的一实施例所述,在上述晶体管元件的制造方法中,还可包括以下步骤。对屏蔽电极进行热氧化制作工艺,而在屏蔽电极上形成第四介电层。

10、依照本发明的一实施例所述,在上述晶体管元件的制造方法中,硅间隙壁可位于第一介电层上。硅间隙壁的顶面可低于基底结构的顶面。

11、依照本发明的一实施例所述,在上述晶体管元件的制造方法中,还包括以下步骤。在沟槽的侧壁上形成垫层。第二介电层可形成在第一介电层与垫层上。第三介电层可形成在第一介电层与垫层上上。

12、基于上述,在本发明所提出的晶体管元件及其制造方法中,由于第二介电层设置在栅极的底部的转角与基底结构之间,因此可增加位于栅极的底部的转角处的栅极介电层的厚度。如此一来,可有效地防止栅极介电层被击穿,进而防止晶体管元件失效。此外,由于第二介电层设置在栅极的底部的转角与基底结构之间,所以可弹性地调整第三介电层的厚度,由此可弹性地调整晶体管元件的临界电压(threshold voltage,vt)。

13、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

技术特征:

1.一种晶体管元件,包括:

2.如权利要求1所述的晶体管元件,其中所述栅极介电层还包括:

3.如权利要求1所述的晶体管元件,还包括:

4.如权利要求1所述的晶体管元件,还包括:

5.如权利要求1所述的晶体管元件,其中所述基底结构包括:

6.一种晶体管元件的制造方法,包括:

7.如权利要求6所述的晶体管元件的制造方法,其中所述第二介电层的形成方法包括:

8.如权利要求7所述的晶体管元件的制造方法,还包括:

9.如权利要求7所述的晶体管元件的制造方法,所述硅间隙壁位于所述第一介电层上,且所述硅间隙壁的顶面低于所述基底结构的顶面。

10.如权利要求6所述的晶体管元件的制造方法,还包括:

技术总结

本发明公开一种晶体管元件及其制造方法,其中该晶体管元件包括基底结构、屏蔽电极、第一介电层、栅极与栅极介电层。在基底结构中具有沟槽。屏蔽电极设置在沟槽中。第一介电层设置在屏蔽电极与基底结构之间。栅极设置在沟槽中与屏蔽电极上。栅极介电层设置在栅极与基底结构之间以及栅极与屏蔽电极之间。栅极介电层包括第二介电层与第三介电层。第二介电层设置在栅极的底部的转角与基底结构之间。第三介电层设置在栅极与基底结构之间、栅极与第二介电层之间以及栅极与屏蔽电极之间。

技术研发人员:杨梅玉,何昌瑾,蒋永康

受保护的技术使用者:力晶积成电子制造股份有限公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!