半导体装置的制作方法

本发明涉及一种半导体装置。

背景技术:

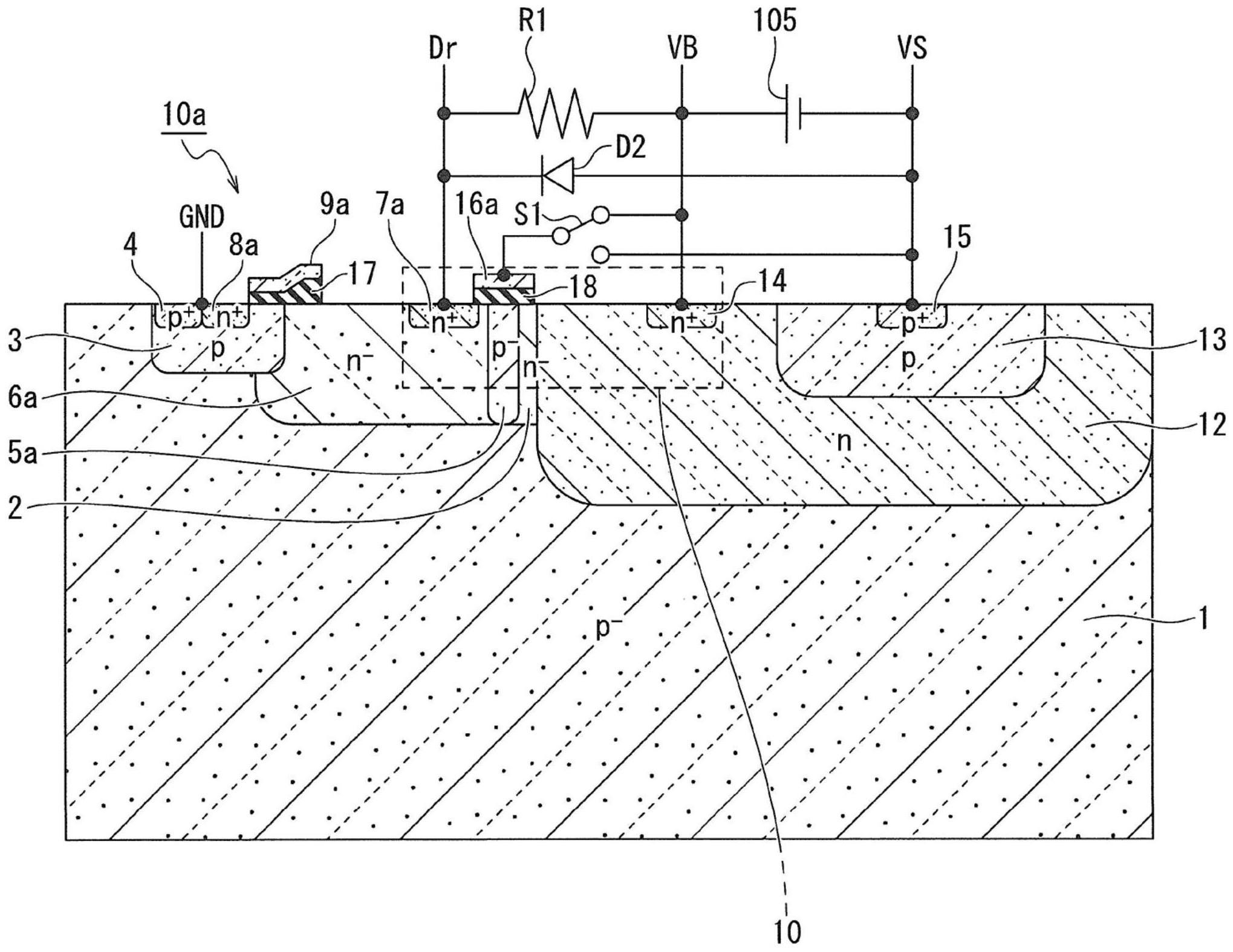

1、一般的高耐压集成电路(hvic)在p型半导体基板上设置有n型阱区。在n型阱区设置有形成高电位侧电路(高边(high side)电路)的高电位侧电路区(高边电路区),在包围n型阱区的p型区设置有形成低电位侧电路(低边(low side)电路)的低电位侧电路区(低边电路区)。在该n型阱区与p型区之间形成有被称为高耐压结终端(hvjt)的高耐压二极管,从而即使在高边电路区的电位比低边电路区的电位高数百v的情况下也正常地进行动作。

2、通常,在高边电路区的n型阱区上形成有p型阱区。p型阱区被施加作为高边电路的基准电位的vs电位,n型阱区被施加作为高边电路的电源电位的vb电位。

3、另外,需要用于从低边电路向高边电路进行信号传递的电平转换元件。电平转换元件一般由高耐压的n沟道mosfet构成,该n沟道mosfet具有设置于高边电路区侧的漏极区以及设置于低边电路区侧的栅极电极和源极区。电平转换元件的漏极电位(dr电位)通过电平转换电阻来与vb电位连接。在电平转换元件的栅极断开时,电平转换元件的dr电位比vs电位高,并且与vb电位大致等同(vb电位≈dr电位>vs电位)。另一方面,在电平转换元件的栅极接通时,电平转换元件的dr电位比vb电位低,并且与vs电位大致等同(vb电位>dr电位≈vs电位)。

4、在被称为自屏蔽方式(ss方式)的结构的情况下,电平转换元件是利用hvjt的一部分来形成的。在高边电路区,除了被固定为vb电位的n型阱区和被固定为vs电位的p型阱区以外,还混合存在被固定为电平转换元件的dr电位的n型漂移区。因此,需要将n型阱区与n型漂移区分离,该分离使用狭缝状的p型分离区。在该p型分离区由于表面电荷等而形成有反型层的情况下,vb电位与dr电位被短路,在电平转换元件的栅极接通时无法正确地传递信号。

5、因此,已知的是,在p型分离区的上方设置屏蔽层以避免在p型分离区形成反型层(参照专利文献1和2)。专利文献1公开了将屏蔽层固定为电平转换元件的dr电位的结构。专利文献2公开了将屏蔽层固定为vs电位的结构。

6、现有技术文献

7、专利文献

8、专利文献1:日本专利第3917211号说明书

9、专利文献2:日本专利第5733416号说明书

技术实现思路

1、发明要解决的问题

2、在以往的hvic中,例如当对高边电路区的n型阱区施加负电压浪涌时表现出如下行为:电平转换元件的dr电位暂时地增加,在超过vb电位之后转为下降而接近vs电位。此时,如果dr电位的下降量大,则存在以下情况:尽管未将电平转换元件的栅极接通,但是dr电位变得与vs电位大致等同(dr电位≈vs电位),电平转换元件的输出发生误反转。

3、鉴于上述问题,本发明的目的在于提供一种能够抑制hvic中由浪涌电压引起的电平转换元件的误动作的半导体装置。

4、用于解决问题的方案

5、本发明的一个方式为一种半导体装置,其主旨在于,具备:(a)第一导电型的基体;(b)第二导电型的阱区,其设置在基体上,形成有高电位侧电路;(c)第二导电型的耐压区,其以包围阱区的周围的方式设置,耐压区的杂质浓度比阱区的杂质浓度低;(d)电平转换元件,其具有设置在基体上的第二导电型的漂移区、设置在漂移区的上部且杂质浓度比漂移区的杂质浓度高的第二导电型的载体接收区、与漂移区相接地设置的第一导电型的基区、以与基区之间被绝缘的方式设置在基区上的第一栅极电极、以及设置在基区的上部的第二导电型的载体供给区;(e)第一导电型的分离区,其设置在基体上的耐压区与漂移区之间;以及(f)第二栅极电极,其以与分离区之间被绝缘的方式设置在分离区上,第二栅极电极被择一性地施加第一电位或比第一电位高的第二电位。

6、发明的效果

7、根据本发明,能够提供一种能够抑制hvic中由浪涌电压引起的电平转换元件的误动作的半导体装置。

技术特征:

1.一种半导体装置,其特征在于,具备:

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求1或2所述的半导体装置,其特征在于,

4.根据权利要求1或2所述的半导体装置,其特征在于,

5.根据权利要求1~4中的任一项所述的半导体装置,其特征在于,

6.根据权利要求1~5中的任一项所述的半导体装置,其特征在于,

7.根据权利要求1~6中的任一项所述的半导体装置,其特征在于,

技术总结

本发明提供一种半导体装置,能够抑制HVIC中由浪涌电压引起的电平转换元件的误动作。半导体装置具备:第一导电型的基体(1);第二导电型的阱区(12),其设置在基体上,形成有高电位侧电路;第二导电型的耐压区(2),其以包围阱区的周围的方式设置;电平转换元件(10a),其具有设置在基体上的第二导电型的漂移区(6a)、设置在漂移区的上部的第二导电型的载体接收区(7a)、与漂移区相接地设置的第一导电型的基区(3)、设置在基区上的第一栅极电极(9a)、以及设置在基区的上部的第二导电型的载体供给区(8a);第一导电型的分离区(5a),其设置在基体上的耐压区与漂移区之间;以及第二栅极电极,其设置在分离区上。

技术研发人员:田中贵英

受保护的技术使用者:富士电机株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!