测试结构及形成方法、测试方法与流程

本发明涉及半导体制造领域,尤其是涉及一种测试结构及形成方法、测试方法。

背景技术:

1、随着半导体技术的进步,集成电路器件的尺寸变得越来越小,当集成电路的集成度增加时,芯片表面无法提供足够面积来制作所需的互连线。因此,目前超大规模集成电路的结构大都采用多层堆叠的金属互连结构。在多层堆叠的金属互连结构中,每一层金属互连层都包括若干条金属互连线,位于同一层的金属互连线之间利用介质材料相隔离,位于不同层的金属互连线之间也利用介质材料相隔离,不同层的金属互连线之间通过导电插塞相连接。

2、目前,随着金属互连线的最小关键尺寸不断的缩小,为了降低工艺复杂程度,底层金属互连通常采用单镶嵌结构(single damascene),即位于上层的金属层和位于下层的导电插塞分别独立形成,因此导电插塞会与相邻的上下两层金属层之间形成两个接触截面,导电插塞的电阻严重影响芯片的性能和良率,因此导电插塞的电阻是测试中必须关注的一项指标。

3、然而,现有技术中在对导电插塞的电阻的测试仍存在诸多问题。

技术实现思路

1、本发明解决的技术问题是提供一种测试结构及形成方法、测试方法,以独立的获取导电插塞条的电阻,进而对相关的工艺制程做出针对性的改善。

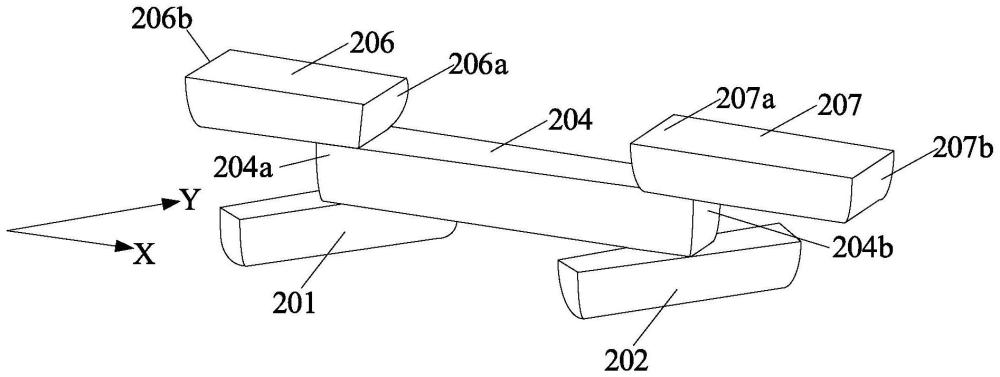

2、为解决上述技术问题,本发明的技术方案提供一种测试结构,包括:衬底;位于所述衬底上相互分立的第一导线和第二导线;位于所述第一导线和所述第二导线上的导电插塞条,所述导电插塞条具有相对的第一端部和第二端部,所述第一端部位于所述第一导线的表面,所述第二端部位于所述第二导线的表面;位于所述导电插塞条上相互分立的第三导线和第四导线,所述第三导线位于所述第一端部的表面,所述第四导线位于所述第二端部的表面。

3、可选的,所述导电插塞条沿第一方向延伸;所述第一导线和所述第二导线分别沿第二方向延伸,且所述第一导线、所述第二导线沿所述第一方向平行排布,所述第一方向与所述第二方向不同。

4、可选的,所述第一方向与所述第二方向垂直。

5、可选的,所述第三导线和所述第四导线分别沿所述第一方向延伸。

6、可选的,所述第三导线包括相对的第三端部和第四端部,所述第三端部位于所述第一端部的表面。

7、可选的,所述第一导线投影至所述衬底上形成第一投影图形,所述第三端部投影至所述衬底上形成第二投影图形,所述第一投影图形的一边界线在所述第二方向上与所述第二投影图形的边界线在所述第二方向上重叠。

8、可选的,所述第四导线包括相对的第五端部和第六端部,所述第五端部位于所述第二端部的表面。

9、可选的,所述第二导线投影至所述衬底上形成第三投影图形,所述第五端部投影至所述衬底上形成第四投影图形,所述第三投影图形的一边界线在所述第二方向上与所述第四投影图形的边界线在所述第二方向上重叠。

10、相应的,本发明还提供一种测试方法,包括:提供测试结构,所述测试结构包括:衬底;位于所述衬底上相互分立的第一导线和第二导线;位于所述第一导线和所述第二导线上的导电插塞条,所述导电插塞条具有相对的第一端部和第二端部,所述第一端部位于所述第一导线的表面,所述第二端部位于所述第二导线的表面;位于所述导电插塞条上相互分立的第三导线和第四导线,所述第三导线位于所述第一端部的表面,所述第四导线位于所述第二端部的表面;在所述第三导线和所述第四导线之间施加恒定电流;获取所述第一导线与第二导线之间的电压;根据所述电压和所述恒定电流,获取所述导电插塞条的电阻。

11、相应的,本发明还一种测试结构的形成方法,包括:提供衬底;在所述衬底上形成相互分立的第一导线和第二导线;在所述第一导线和所述第二导线上形成导电插塞条,所述导电插塞条具有相对的第一端部和第二端部,所述第一端部与所述第一导线的表面接触,所述第二端部与所述第二导线的表面接触;在所述导电插塞条上形成相互分立的第三导线和第四导线,所述第三导线与所述第一端部的表面接触,所述第四导线与所述第二端部的表面接触。

12、可选的,所述导电插塞条沿第一方向延伸;所述第一导线和所述第二导线分别沿第二方向延伸,且所述第一导线、所述第二导线沿所述第一方向平行排布,所述第一方向与所述第二方向不同。

13、可选的,所述第一方向与所述第二方向垂直。

14、可选的,所述第三导线和所述第四导线分别沿所述第一方向延伸。

15、可选的,所述第三导线包括相对的第三端部和第四端部,所述第三端部位于所述第一端部的表面。

16、可选的,所述第一导线投影至所述衬底上形成第一投影图形,所述第三端部投影至所述衬底上形成第二投影图形,所述第一投影图形的一边界线在所述第二方向上与所述第二投影图形的边界线在所述第二方向上重叠。

17、可选的,所述第四导线包括相对的第五端部和第六端部,所述第五端部位于所述第二端部的表面。

18、可选的,所述第二导线投影至所述衬底上形成第三投影图形,所述第五端部投影至所述衬底上形成第四投影图形,所述第三投影图形的一边界线在所述第二方向上与所述第四投影图形的边界线在所述第二方向上重叠。

19、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

20、本发明技术方案提供的测试结构中,所述导电插塞条上的第三导线和第四导线是相互分立排布的,其中第三导线位于所述导电插塞条的第一端部的表面,所述第四导线是位于所述第二端部的表面,在后续的测试过程中,通过在所述第三导线和所述第四导线施加恒定电流,并且获取所述第一导线与所述第二导线之间的电压,进而获取所述导电插塞条的电阻,由于所述第三导线、所述导电插塞条以及所述第四导线形成串联,且所述第一导线和所述第二导线之间的电压是所述导电插塞条两端的电压,此时获取的电阻值只是单纯的所述导电插塞条的电阻值,从而提升了所述导电插塞条的电阻测试准确性,进而可以对相关工艺制程做出针对性的改进。

21、本发明技术方案提供的测试方法中,通过在所述第三导线和所述第四导线施加恒定电流,并且获取所述第一导线与所述第二导线之间的电压,进而获取所述导电插塞条的电阻,由于所述第三导线、所述导电插塞条以及所述第四导线形成串联,且所述第一导线和所述第二导线之间的电压是所述导电插塞条两端的电压,此时获取的电阻值只是单纯的所述导电插塞条的电阻值,从而提升了所述导电插塞条的电阻测试准确性,进而可以对相关工艺制程做出针对性的改进。

技术特征:

1.一种测试结构,其特征在于,包括:

2.如权利要求1所述的测试结构,其特征在于,所述导电插塞条沿第一方向延伸;所述第一导线和所述第二导线分别沿第二方向延伸,且所述第一导线、所述第二导线沿所述第一方向平行排布,所述第一方向与所述第二方向不同。

3.如权利要求2所述的测试结构,其特征在于,所述第一方向与所述第二方向垂直。

4.如权利要求2所述的测试结构,其特征在于,所述第三导线和所述第四导线分别沿所述第一方向延伸。

5.如权利要求2所述的测试结构,其特征在于,所述第三导线包括相对的第三端部和第四端部,所述第三端部位于所述第一端部的表面。

6.如权利要求5所述的测试结构,其特征在于,所述第一导线投影至所述衬底上形成第一投影图形,所述第三端部投影至所述衬底上形成第二投影图形,所述第一投影图形的一边界线在所述第二方向上与所述第二投影图形的边界线在所述第二方向上重叠。

7.如权利要求2所述的测试结构,其特征在于,所述第四导线包括相对的第五端部和第六端部,所述第五端部位于所述第二端部的表面。

8.如权利要求7所述的测试结构,其特征在于,所述第二导线投影至所述衬底上形成第三投影图形,所述第五端部投影至所述衬底上形成第四投影图形,所述第三投影图形的一边界线在所述第二方向上与所述第四投影图形的边界线在所述第二方向上重叠。

9.一种测试方法,其特征在于,包括:

10.一种测试结构的形成方法,其特征在于,包括:

11.如权利要求10所述的测试结构的形成方法,其特征在于,所述导电插塞条沿第一方向延伸;所述第一导线和所述第二导线分别沿第二方向延伸,且所述第一导线、所述第二导线沿所述第一方向平行排布,所述第一方向与所述第二方向不同。

12.如权利要求11所述的测试结构的形成方法,其特征在于,所述第一方向与所述第二方向垂直。

13.如权利要求11所述的测试结构的形成方法,其特征在于,所述第三导线和所述第四导线分别沿所述第一方向延伸。

14.如权利要求11所述的测试结构的形成方法,其特征在于,所述第三导线包括相对的第三端部和第四端部,所述第三端部位于所述第一端部的表面。

15.如权利要求14所述的测试结构的形成方法,其特征在于,所述第一导线投影至所述衬底上形成第一投影图形,所述第三端部投影至所述衬底上形成第二投影图形,所述第一投影图形的一边界线在所述第二方向上与所述第二投影图形的边界线在所述第二方向上重叠。

16.如权利要求11所述的测试结构的形成方法,其特征在于,所述第四导线包括相对的第五端部和第六端部,所述第五端部位于所述第二端部的表面。

17.如权利要求16所述的测试结构的形成方法,其特征在于,所述第二导线投影至所述衬底上形成第三投影图形,所述第五端部投影至所述衬底上形成第四投影图形,所述第三投影图形的一边界线在所述第二方向上与所述第四投影图形的边界线在所述第二方向上重叠。

技术总结

本发明提供一种测试结构及形成方法、测试方法,其中测试结构包括:衬底;位于所述衬底上相互分立的第一导线和第二导线;位于所述第一导线和所述第二导线上的导电插塞条,所述导电插塞条具有相对的第一端部和第二端部,所述第一端部位于所述第一导线的表面,所述第二端部位于所述第二导线的表面;位于所述导电插塞条上相互分立的第三导线和第四导线,所述第三导线位于所述第一端部的表面,所述第四导线位于所述第二端部的表面;以独立的获取导电插塞条的电阻,进而对相关的工艺制程做出针对性的改善。

技术研发人员:吴轶超

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/5/20

- 还没有人留言评论。精彩留言会获得点赞!