改善外延工艺弛豫的方法与流程

本发明涉及半导体,特别是涉及一种改善外延工艺弛豫的方法。

背景技术:

1、55纳米技术节点的bi cmos(铋互补金属氧化物半导体)平台,hbt(异质结双极型晶体管)器件部分的基区目前主要采用方法为seg(选择性外延技术)和nseg(非选择性外延);

2、非选择性锗硅现有工艺在调试研究中发现,压力降低条件下,硅锗键长变短,分子间间距较小,晶格原子间分子间排斥作用力加强,应力抑制削弱,从而发生晶格失配引起的弛豫现象;

3、上述弛豫现象的发生导致非选择性锗硅工艺压力调试窗口(window)大大减小,很难满足工艺需求;

4、传统弛豫改善方法均会改变ge浓度,而ge浓度对于器件电性参数至关重要。

5、为解决上述问题,需要提出一种新型的改善外延工艺弛豫的方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种改善外延工艺弛豫的方法,用于解决现有技术中非选择性锗硅工艺中现,压力降低条件下,硅锗键长变短,分子间间距较小,晶格原子间分子间排斥作用力加强,应力抑制削弱,从而发生晶格失配引起的弛豫现象;弛豫现象的发生导致非选择性锗硅工艺压力调试窗口大大减小,很难满足工艺需求,会改变ge浓度,影响器件的电性参数的问题。

2、为实现上述目的及其他相关目的,本发明提供一种改善外延工艺弛豫的方法包括:

3、提供衬底,在所述衬底上形成外延层;其中,

4、所述外延层的形成工艺包括:

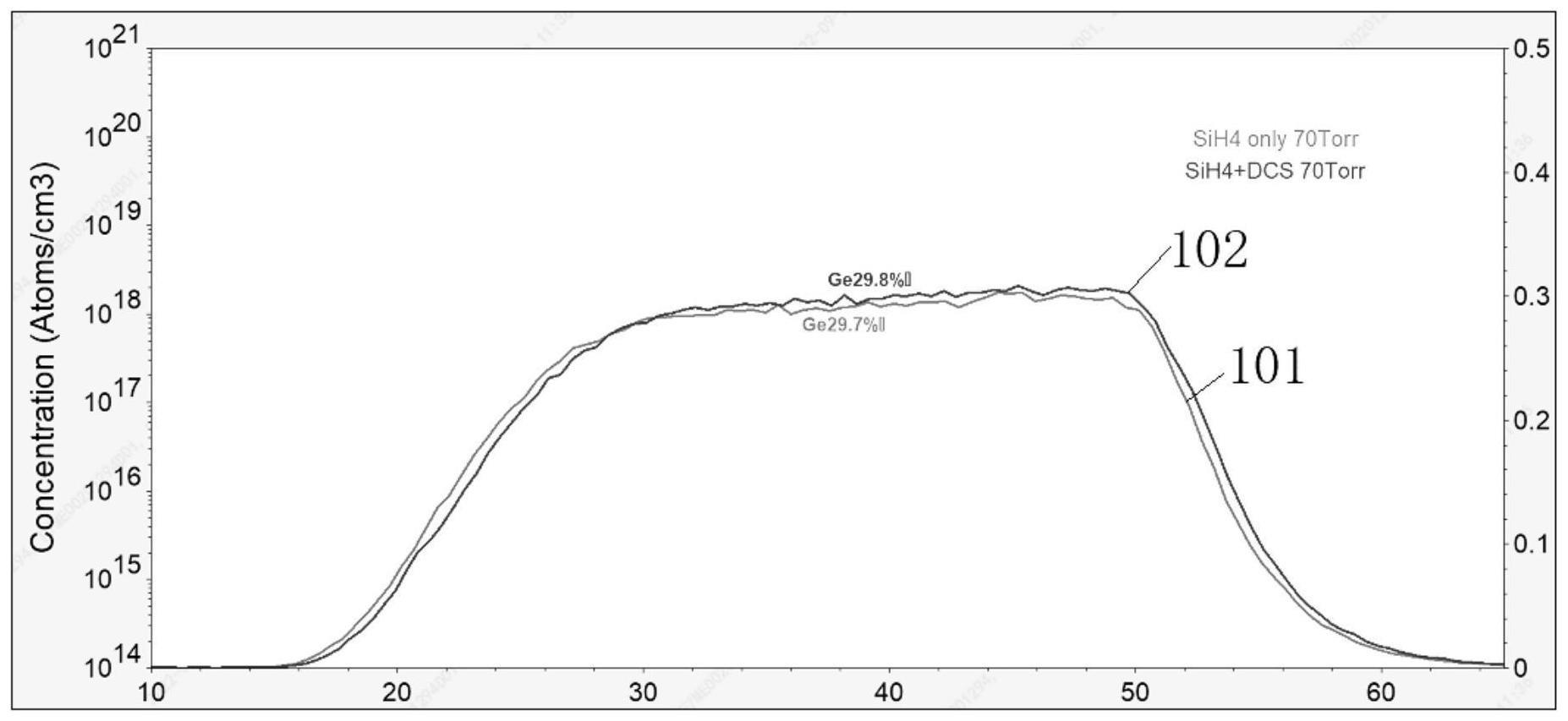

5、利用sih4气体作为第一硅源气体,sih2cl2气体作为第二硅源气体;

6、调节温度与压强,使得所述sih2cl2气体分解为硅气体和氯化氢,所述sih4气体分解为硅气体和氢气。

7、优选地,所述衬底为硅衬底。

8、优选地,所述外延层的形成工艺中压力范围为5至80torr。

9、优选地,所述外延层的形成工艺中温度范围为600至700摄氏度。

10、优选地,所述第二硅源气体相对于所述第一硅源气体的气体体积比小于等于1.5:1。

11、优选地,所述外延层为锗硅外延层。

12、优选地,所述外延层利用非选择性外延的方法形成。

13、优选地,所述非选择外延的方法包括:在形成集电极后,在所述衬底上淀积二氧化硅层,利用光刻、刻蚀打开所述锗硅外延层窗口,在去除所述锗硅外延窗口内的二氧化硅层和清洗后,非选择性生长所述锗硅外延层。

14、优选地,所述方法用于异质结双极型晶体管的制造工艺。

15、如上所述,本发明的改善外延工艺弛豫的方法,具有以下有益效果:

16、本发明利用非选择性锗硅工艺形成的外延层,改善弛豫提高工艺压力窗口的同时,不影响外延层中ge的浓度。

技术特征:

1.一种改善外延工艺弛豫的方法,其特征在于,至少包括:

2.根据权利要求1所述的改善外延工艺弛豫的方法,其特征在于:所述衬底为硅衬底。

3.根据权利要求1所述的改善外延工艺弛豫的方法,其特征在于:所述外延层的形成工艺中压力范围为5至80torr。

4.根据权利要求1所述的改善外延工艺弛豫的方法,其特征在于:所述外延层的形成工艺中温度范围为600至700摄氏度。

5.根据权利要求1所述的改善外延工艺弛豫的方法,其特征在于:所述第二硅源气体相对于所述第一硅源气体的气体体积比小于等于1.5:1。

6.根据权利要求1所述的改善外延工艺弛豫的方法,其特征在于:所述外延层为锗硅外延层。

7.根据权利要求6所述的改善外延工艺弛豫的方法,其特征在于:所述外延层利用非选择性外延的方法形成。

8.根据权利要求7所述的改善外延工艺弛豫的方法,其特征在于:所述非选择外延的方法包括:在形成集电极后,在所述衬底上淀积二氧化硅层,利用光刻、刻蚀打开所述锗硅外延层窗口,在去除所述锗硅外延窗口内的二氧化硅层和清洗后,非选择性生长所述锗硅外延层。

9.根据权利要求1所述的改善外延工艺弛豫的方法,其特征在于:所述方法用于异质结双极型晶体管的制造工艺。

技术总结

本发明提供一种改善外延工艺弛豫的方法,提供衬底,在衬底上形成外延层;其中,外延层的形成工艺包括:利用SiH4气体作为第一硅源气体,SiH2Cl2气体作为第二硅源气体;调节温度与压强,使得SiH2Cl2气体分解为硅气体和氯化氢,SiH4气体分解为硅气体和氢气。本发明利用非选择性锗硅工艺形成的外延层,改善弛豫提高工艺压力窗口的同时,不影响外延层中Ge的浓度。

技术研发人员:孙伟虎,周康,王勇,杨德明,赵正元

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!