薄膜晶体管及阵列基板的制作方法

本申请涉及显示,尤其涉及一种薄膜晶体管和阵列基板。

背景技术:

1、采用氧化物半导体的薄膜晶体管(tft),如氧化铟镓锌(igzo),凭借其高场效应迁移率和良好的均匀性,成为oled工艺的绝佳候选。且igzo与非晶质硅(a-si)材料相比,具有更低的漏电流和更高电子迁移率。同时为了提高基于igzo tft的稳定性和饱和特性,通常在igzo沟道下方设置遮光层(ls)。而igzo为半导体材料,沟道以外的部分需要进行导体化处理。通常在栅极绝缘层(gi)干法刻蚀(dry etch)后,采用氨气(nh3)、氢气(h2)和氦气(he)等任意一种气体对未被gi遮挡的igzo有源层进行导体化处理,从而与源/漏电极连通。

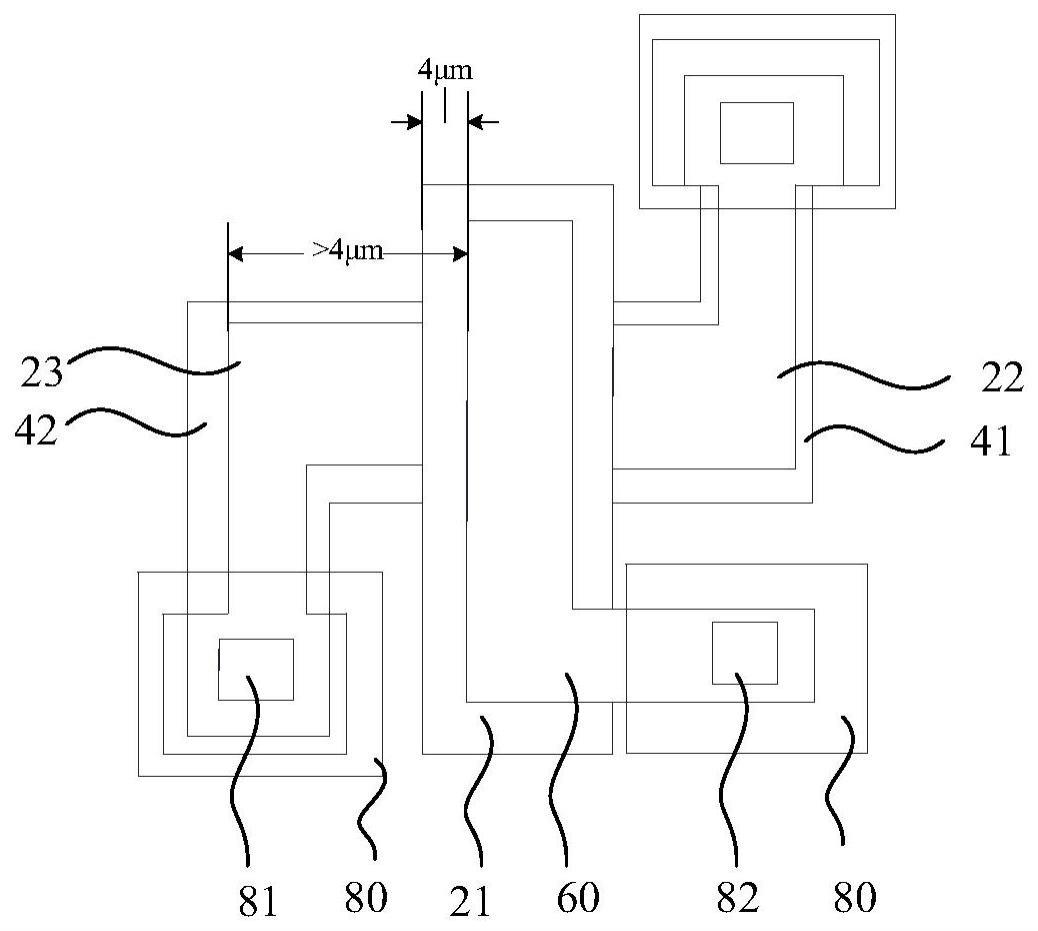

2、但是由于igzo走线会爬ls坡,且igzo导体化与gi dry etch在同一腔室,而dryetch存在纵向刻蚀快、横向刻蚀慢的各向异性特征,当ls厚度较厚(以上)或者taper较陡(60°以上)时,在ls爬坡位置上方的igzo容易出现导体化不足的问题,甚至是出现gi残留,导致导体化igzo电阻较大,出现开态电流降低(ion降低)的问题,导致功耗升高,屏幕亮度低。此外,当ls边界距离栅极边界较近(4μm以内)时,ls爬坡位置上方的igzo和gi容易被pr光刻胶遮挡,拐角处较难刻蚀加导体化,导致igzo电阻增加。

3、综上所述,现有的基于igzo tft器件的oled阵列基板存在有源层导体化不足导致的电阻较大、ion降低的问题。故,有必要提供一种薄膜晶体管及阵列基板来改善这一问题。

技术实现思路

1、本申请实施例提供一种薄膜晶体管及阵列基板,以改善igzo有源层导体化不足导致的igzo电阻较大、ion降低的问题,从而降低功耗、提升屏幕亮度。

2、本申请实施例提供一种薄膜晶体管,包括基板;

3、遮光层,位于所述基板的上方,所述遮光层包括相互连接的第一遮光图案、第二遮光图案和第三遮光图案;

4、有源层,位于所述遮光层的上方,所述有源层包括沟道区,以及位于所述沟道区两侧的导体化区,并分别定义为第一导体化区和第二导体化区;

5、源/漏电极,位于所述有源层的上方,且所述源/漏电极分别与所述第一导体化区和所述第二导体化区对应连接;

6、其中,所述第一遮光图案位于所述沟道区的下方,且其在所述基板上的投影至少覆盖所述沟道区在所述基板上的投影;

7、所述第二遮光图案位于所述第一导体化区的下方,且其在所述基板上的投影至少与部分所述第一导体化区在所述基板上的投影重合;

8、所述第三遮光图案位于所述第二导体化区的下方,且其在所述基板上的投影至少与部分所述第二导体化区在所述基板上的投影重合。

9、根据本申请一实施例,所述第一导体化和所述第二导体化区在所述基板上的投影为l形,且所述第一导体化区与所述第二导体化区通过所述沟道区连接,并在所述基板上形成直角z字形投影。

10、根据本申请一实施例,所述遮光层延伸至所述源/漏电极的下方。

11、根据本申请一实施例,在所述导体化区的延伸方向上,所述第一导体化区的下方均设有第二遮光图案,所述第二导体化区的下方均设有第三遮光图案;其中,所述导体化区在所述基板上的投影覆盖所述第二遮光图案和所述第三遮光图案在所述基板上的投影。

12、根据本申请一实施例,所述第二遮光图案与所述第三遮光图案为l形,且所述第二遮光图案与所述第三遮光图案通过第一遮光图案连接,并形成直角z字形图案。

13、根据本申请一实施例,在所述导体化区的延伸方向上,所述第一导体化区下方错位设置第二遮光图案,所述第二导体化区下方错位设有第三遮图案;其中,所述导体化区在基板的投影不完全覆盖所述第二遮光图和所述第三遮光图案在所述基板上的投影。

14、根据本申请一实施例,所述第二遮光图案与所述第三遮光图案为l形,且所述第二遮光图案与所述第三遮光图案通过第一遮光图案连接,并形成多阶梯形图案。

15、根据本申请一实施例,所述第二遮光图案在所述基板上的投影至少与部分沿水平方向延伸的第一导体化区在所述基板上的投影重合,所述第三遮光图案在基板上的投影至少与部分沿水平方向延伸的第二导体化区在所述基板上的投影重合。

16、根据本申请一实施例,所述第二遮光图案与所述第三遮光图案通过第一遮光图案连接,并至少形成一个矩形图案。

17、根据本申请一实施例,所述阵列基板包括上述优选实施例中任意一项所述的薄膜晶体管。

18、本申请实施例的有益效果:本申请实施例提供一种薄膜晶体管及阵列基板,所述薄膜晶体管包括遮光层,所述遮光层包括第一遮光图案和第二遮光图案;有源层,位于所述遮光层上方,所述有源层包括沟道区,以及位于所述沟道区两侧的导体化区,并定义为第一导体化区和第二导体化区;其中,所述第一遮光图案在所述基板上的投影覆盖所述沟道区在所述基板上的投影;所述第二遮光图案在所述基板上的投影至少与部分所述第一导体化区在所述遮光层的投影重合;所述第三遮光图案在所述基板上的投影至少与部分所述第二导体化区在所述遮光层的投影重合。通过增大所述遮光层的面积,将所述遮光层延伸至所述有源层的导体化区域,使遮光层爬坡位置上方igzo和gi拐角处不容易受到pr光刻胶阻挡,可以受到刻蚀和导体化的影响,从而改善igzo有源层导体化不足导致的igzo电阻较大、ion降低的问题,进而降低功耗、提升屏幕亮度。

技术特征:

1.一种薄膜晶体管,其特征在于,所述薄膜晶体管包括

2.如权利要求1所述的薄膜晶体管,其特征在于,所述第一导体化和所述第二导体化区在所述基板上的投影为l形,且所述第一导体化区与所述第二导体化区通过所述沟道区连接,并在所述基板上形成直角z字形投影。

3.如权利要求1所述的薄膜晶体管,其特征在于,所述遮光层延伸至所述源/漏电极的下方。

4.如权利要求3所述的薄膜晶体管,其特征在于,在所述导体化区的延伸方向上,所述第一导体化区的下方均设有第二遮光图案,所述第二导体化区的下方均设有第三遮光图案;其中,所述导体化区在所述基板上的投影覆盖所述第二遮光图案和所述第三遮光图案在所述基板上的投影。

5.如权利要求4所述的薄膜晶体管,其特征在于,所述第二遮光图案与所述第三遮光图案为l形,且所述第二遮光图案与所述第三遮光图案通过第一遮光图案连接,并形成直角z字形图案。

6.如权利要求3所述的薄膜晶体管,其特征在于,在所述导体化区的延伸方向上,所述第一导体化区下方错位设置第二遮光图案,所述第二导体化区下方错位设有第三遮图案;其中,所述导体化区在基板的投影不完全覆盖所述第二遮光图和所述第三遮光图案在所述基板上的投影。

7.如权利要求6所述的薄膜晶体管,其特征在于,所述第二遮光图案与所述第三遮光图案为l形,且所述第二遮光图案与所述第三遮光图案通过第一遮光图案连接,并形成多阶梯形图案。

8.如权利要求1所述的薄膜晶体管,其特征在于,所述第二遮光图案在所述基板上的投影至少与部分沿水平方向延伸的第一导体化区在所述基板上的投影重合,所述第三遮光图案在基板上的投影至少与部分沿水平方向延伸的第二导体化区在所述基板上的投影重合。

9.如权利要求8所述的薄膜晶体管,其特征在于,所述第二遮光图案与所述第三遮光图案通过第一遮光图案连接,并至少形成一个矩形图案。

10.一种阵列基板,其特征在于,所述阵列基板包括权利要求1-9任一项所述的薄膜晶体管。

技术总结

本申请提供一种薄膜晶体管和阵列基板,该薄膜晶体管包括遮光层;有源层,位于所述遮光层的上方,所述有源层包括沟道区,以及位于所述沟道区两侧的导体化区。通过增大所述遮光层的面积,将所述遮光层延伸至所述有源层的导体化区域,使遮光层在基板上的投影至少与部分导体化区在基板上的投影重合,使遮光层爬坡位置上方IGZO和GI拐角处不容易受到PR光刻胶阻挡,可以受到刻蚀和导体化的影响,从而改善IGZO有源层导体化不足导致的IGZO电阻较大、Ion降低的问题,进而降低功耗、提升屏幕亮度。

技术研发人员:郑帅,请求不公布姓名,宋志伟

受保护的技术使用者:深圳市华星光电半导体显示技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!