半导体器件、半导体器件的制作方法及电子设备与流程

本发明涉及半导体领域,尤其涉及一种半导体器件、半导体器件的制作方法及电子设备。

背景技术:

1、对于ic(integrated circuit,集成电路)与场效应管的集成芯片,二极管是ic的常用器件之一。另外,对于确保ic的esd(electro-static discharge,静电释放)耐量,齐纳二极管更是不可或缺。为防止产生寄生电路,通常采用poly型二极管。

2、为了确保二极管的导电能力,二极管的pn结宽比较大,而这将导致半导体器件的面积变大,增加了半导体器件的成本。另外,由于半导体器件面积的增大也会导致封装尺寸较大,无法实现多通道产品。

技术实现思路

1、本发明提供一种半导体器件、半导体器件的制作方法及电子设备,能够保证在二极管具有较好的导电能力的前提下,减少半导体器件的第一表面的面积,降低半导体器件的成本。

2、为解决上述技术问题,本发明采用如下技术方案:

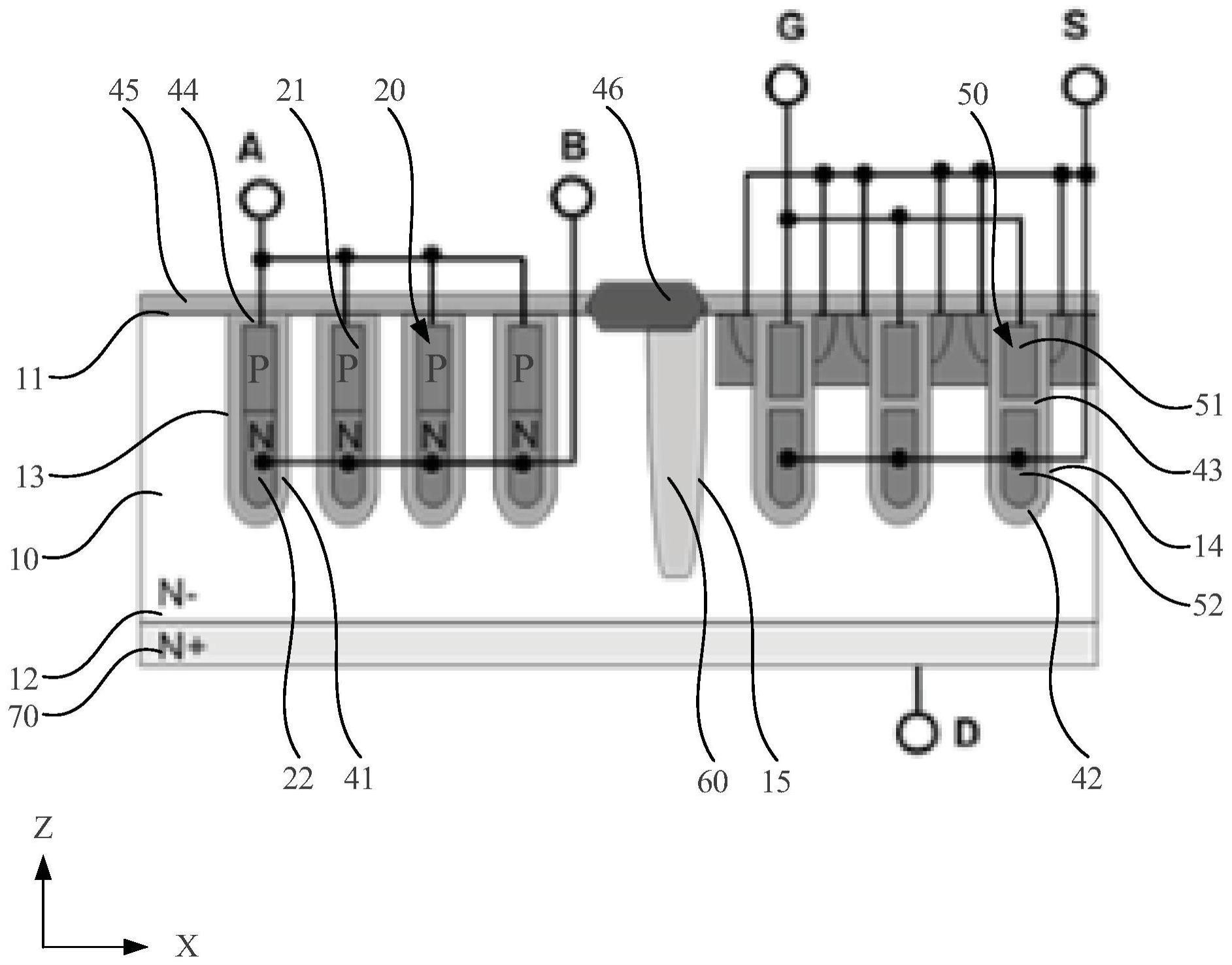

3、本发明的第一方面,提供一种半导体器件,包括衬底、二极管和第一绝缘层;所述衬底具有第一表面,所述第一表面上设有第一沟槽,所述第一绝缘层附着于所述第一沟槽的内壁;所述二极管包括p型导电层和n型导电层,所述p型导电层和所述n型导电层均位于所述第一沟槽内,部分所述第一绝缘层位于所述p型导电层与所述衬底之间,部分所述第一绝缘层位于所述n型导电层与所述衬底之间,所述p型导电层和所述n型导电层相连且沿第一方向层叠,所述第一方向为所述衬底的厚度方向。

4、本发明的有益效果:

5、p型导电层和n型导电层沿衬底的厚度方向排列,可增加其截面面积,且p型导电层和n型导电层沿长度方向的尺寸可设置为较小的尺寸,p型导电层和n型导电层沿宽度方向的尺寸也可设置为较小的尺寸,即可获得较好的导电性,由此可大大减小了二极管在长度方向和宽度方向所占用半导体器件的尺寸,进而减少占用半导体器件的第一表面的面积,由此减少半导体器件的第一表面的面积,进而降低了半导体器件的成本,同时也为实现多通道产品做出贡献。

6、可选地,所述第一表面上还设有第二沟槽,所述半导体器件还包括第二绝缘层、第三绝缘层和场效应管,所述第二绝缘层附着于所述第二沟槽的内壁;所述场效应管包括位于所述第二沟槽内的第一导电层和第二导电层,部分所述第二绝缘层位于所述第一导电层与所述衬底之间,部分所述第二绝缘层位于所述第二导电层与所述衬底之间,所述第一导电层和所述第二导电层沿所述第一方向层叠,所述第三绝缘层位于所述第一导电层和所述第二导电层之间。

7、场效应管中的第一导电层和第二导电层也沿第一方向层叠,其层叠方向与二极管的p型导电层和n型的层叠方向相同。由于,场效应管本身具有一定的厚度,因此,p型导电层和n型导电层的沿厚度方向的尺寸之和也可以与场效应管的厚度相同,因此,不需要增加半导体器件的厚度,并且还可以减小二极管沿长度方向和宽度方向的尺寸,由此可在减少半导体器件的第一表面的面积的基础上,还能够获得二极管较好的导电性。

8、可选地,所述第一沟槽与所述第二沟槽沿所述第一方向的尺寸相同。由于当半导体器件包括场效应管时,本身就需要在衬底上加工出第二沟槽,便于在第二沟槽内形成第二绝缘层、第一导电层和第二导电层等。因此,当第一沟槽与第二沟槽沿第一方向的尺寸相同时,即,第一沟槽与第二沟槽的深度相同,由此,可在同一道工序中加工第一沟槽和第二沟槽。

9、可选地,所述p型导电层相比所述n型导电层更加靠近所述第一表面,所述第一导电层相比所述第二导电层更加靠近所述第一表面,所述n型导电层与所述第二导电层沿第一方向的尺寸相同。

10、可选地,所述二极管、所述第一沟槽和所述第一绝缘层的数量均为多个且相同;多个所述第一绝缘层和多个所述二极管一一对应地位于多个所述第一沟槽内,每个所述二极管的p型导电层均连接,每个所述二极管的n型导电层均连接。

11、可选地,多个所述二极管沿第二方向排列,每个所述二极管均沿第三方向延伸,所述第二方向和所述第三方向均与所述第一方向垂直,所述第二方向与所述第三方向之间具有夹角。

12、可选地,所述半导体器件还包括隔离带,所述二极管和所述场效应管分别位于所述隔离带的两侧。

13、可选地,所述半导体器件还包括第四绝缘层和第五绝缘层,所述第四绝缘层覆盖于所述p型导电层上,且位于所述第一沟槽内,所述第四绝缘层背离所述p型导电层的表面与所述第一表面齐平;所述第五绝缘层设于所述第一表面上,且部分覆盖于所述第四绝缘层上。

14、本发明还提供一种电子设备,包括电路板以及上述任一项所述的半导体器件,所述半导体器件与所述电路板电连接。电子设备能够实现上述半导体器件的所有效果。

15、本发明还提供一种半导体器件的制作方法,所述制作方法包括:提供衬底,所述衬底具有第一表面;在所述第一表面进行刻蚀处理形成间隔的第一沟槽和第二沟槽;在所述第一沟槽内形成第一绝缘层,以及在所述第二沟槽内形成第二绝缘层;在所述第一绝缘层上形成n型导电层,以及在所述第二绝缘层上形成第二导电层;在所述n型导电层上形成p型导电层;在所述第二导电层上依次形成第三绝缘层和第一导电层。

16、p型导电层和n型导电层沿衬底的厚度方向排列,可增加其截面面积,且p型导电层和n型导电层沿长度方向的尺寸可设置为较小的尺寸,p型导电层和n型导电层沿宽度方向的尺寸也可设置为较小的尺寸,即可获得较好的导电性,由此可大大减小了二极管在长度方向和宽度方向所占用半导体器件的尺寸,进而减少占用半导体器件的第一表面的面积,由此减少半导体器件第一表面的面积,进而降低了半导体器件成本,同时也为实现多通道产品做出贡献。

17、由于当半导体器件包括场效应管时,本身就需要在衬底上加工出第二沟槽,便于在沟槽内形成第二绝缘层、第一导电层和第二导电层等。因此,当第一沟槽与第二沟槽沿第一方向的尺寸相同时,即,第一沟槽与第二沟槽的深度相同,由此,可在同一道工序中加工第一沟槽和第二沟槽。

技术特征:

1.一种半导体器件,其特征在于,包括衬底、二极管和第一绝缘层;

2.根据权利要求1所述的半导体器件,其特征在于,所述第一表面上还设有第二沟槽,所述半导体器件还包括第二绝缘层、第三绝缘层和场效应管,所述第二绝缘层附着于所述第二沟槽的内壁;

3.根据权利要求2所述的半导体器件,其特征在于,所述第一沟槽与所述第二沟槽沿所述第一方向的尺寸相同。

4.根据权利要求2所述的半导体器件,其特征在于,所述p型导电层相比所述n型导电层更加靠近所述第一表面,所述第一导电层相比所述第二导电层更加靠近所述第一表面,所述n型导电层与所述第二导电层沿第一方向的尺寸相同。

5.根据权利要求1或2所述的半导体器件,其特征在于,所述二极管、所述第一沟槽和所述第一绝缘层的数量均为多个且相同;

6.根据权利要求1或2所述的半导体器件,其特征在于,多个所述二极管沿第二方向排列,每个所述二极管均沿第三方向延伸,所述第二方向和所述第三方向均与所述第一方向垂直,所述第二方向与所述第三方向之间具有夹角。

7.根据权利要求2所述的半导体器件,其特征在于,所述半导体器件还包括隔离带,所述二极管和所述场效应管分别位于所述隔离带的两侧。

8.根据权利要求1、2或7所述的半导体器件,其特征在于,所述半导体器件还包括第四绝缘层和第五绝缘层,所述第四绝缘层覆盖于所述p型导电层上,且位于所述第一沟槽内,所述第四绝缘层背离所述p型导电层的表面与所述第一表面齐平;所述第五绝缘层设于所述第一表面上,且部分覆盖于所述第四绝缘层上。

9.一种电子设备,其特征在于,包括电路板以及权利要求1-8任一项所述的半导体器件,所述半导体器件与所述电路板电连接。

10.一种半导体器件的制作方法,其特征在于,所述制作方法包括:

技术总结

本发明公开了一种半导体器件、半导体器件的制作方法及电子设备,其中,半导体器件,包括衬底、二极管和第一绝缘层;衬底具有第一表面,第一表面上设有第一沟槽,第一绝缘层附着于第一沟槽的内壁;二极管包括P型导电层和N型导电层,P型导电层和N型导电层均位于第一沟槽内,部分第一绝缘层位于P型导电层与衬底之间,部分第一绝缘层位于N型导电层与衬底之间,P型导电层和N型导电层相连且沿第一方向层叠,第一方向为衬底的厚度方向。本发明能够保证在二极管具有较好的导电能力的前提下,减少半导体器件的第一表面的面积,降低半导体器件的成本。

技术研发人员:吕慧瑜,罗杰馨,柴展

受保护的技术使用者:上海功成半导体科技有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!