半导体封装器件及封装方法与流程

本发明涉及半导体,尤其涉及一种半导体封装器件及封装方法。

背景技术:

1、当前,针对扇出(fan out)封装工艺进行高密度晶粒(die,也称晶片)间互联的半导体器件,一般为高性能高功耗芯片。一方面此类芯片由于工艺较小耐压低,需要低压供电;一方面此类芯片由于性能需求,需要大电流;为此,低压大电流通过外部电源模块供电,链路上会带来大量的功耗损失。

技术实现思路

1、有鉴于此,本发明实施例提供一种半导体封装器件及封装方法,便于减少供电链路上的功耗损失。

2、为达到上述发明目的,采用如下技术方案:

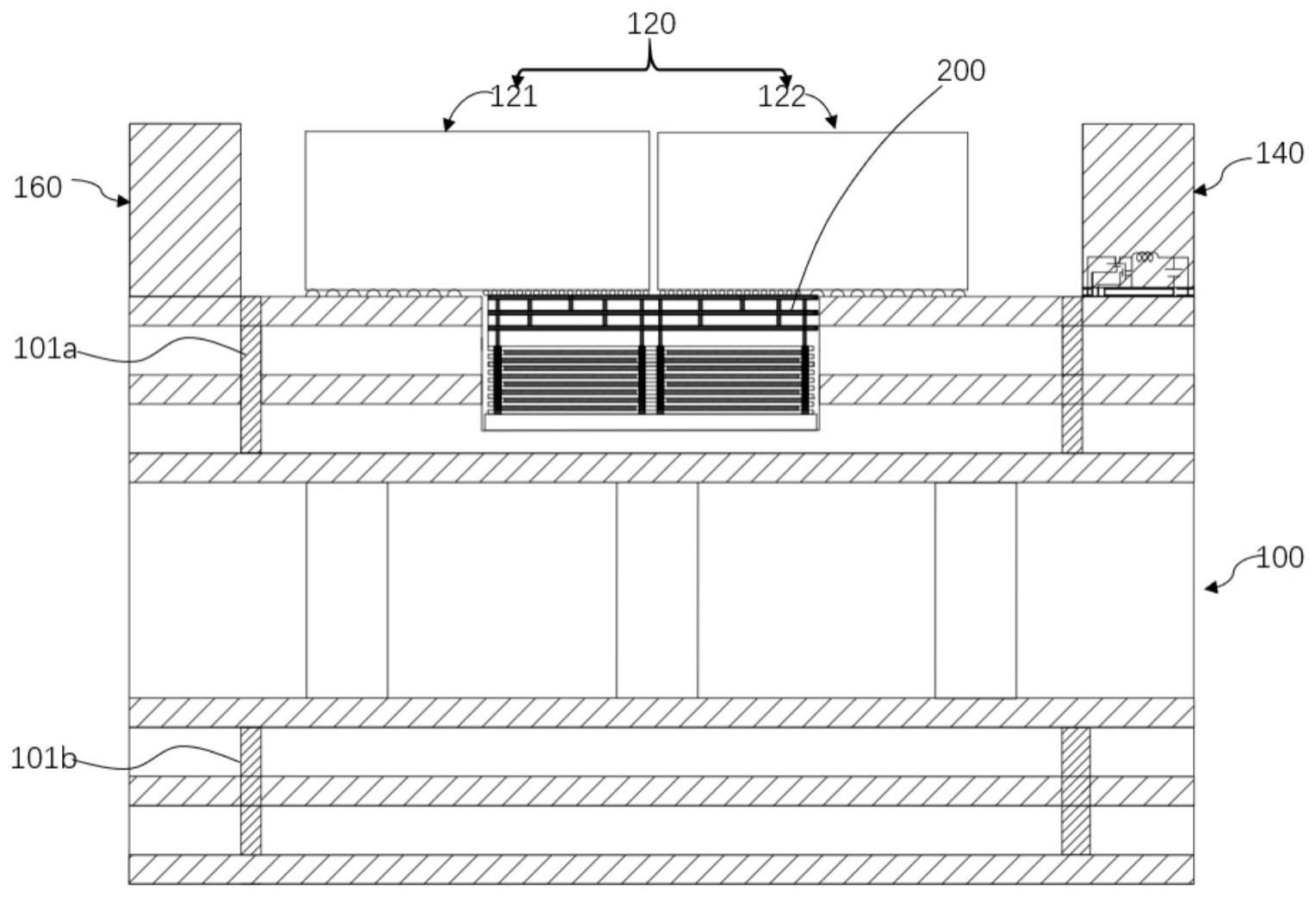

3、根据本发明实施例的第一个方面,提供了一种半导体封装器件,包括:封装基板;所述封装基板上具有互联导线;重布线层基板;所述重布线层基板布设于所述封装基板上;晶粒单元;所述晶粒单元的一部分连接于所述重布线层基板上,所述晶粒单元的另一部分连接于所述封装基板上;电源模块;所述电源模块位于所述晶粒单元的周边,且所述电源模块通过所述互联导线与所述晶粒单元电连接。

4、可选的,至少有一个所述电源模块上用于安设散热模组。

5、可选的,所述电源模块包括:电源电路,所电源电路封装于壳体内。

6、可选的,所述电源模块设有一个或多个。

7、可选的,所述电源模块包括:印制线路板、开关驱动电路、电感及电容,所述开关驱动电路、电感及电容分别电连接于所述印制线路板上,且所述开关驱动电路的输出端与所述电感的输入端电连接,所述电感的输出端与所述电容的输入端电连接,所述电容的输出端电连接至所述晶粒单元的供电引脚上。

8、可选的,所述电源模块还包括:去耦电容,所述去耦电容设于所述电容的输出端到所述晶粒单元的供电引脚之间的节点上。

9、可选地,至少在所述电源模块外部封装的壳体、与散热器对应的表面上镀有金属层。

10、可选地,所述晶粒单元,包括:第一晶粒及第二晶粒;

11、所述封装基板上设有重布线层基板,所述第一晶粒的第一部分与第二晶粒的第一部分分别电连接于所述重布线层基板上,所述第一晶粒的第二部分与第二晶粒的第二部分分别电连接于所述封装基板上,所述第一晶粒与第二晶粒间隔设置,且所述第一晶粒与第二晶粒之间通过重布线层基板上的互联线连接。

12、可选地,所述第一晶粒与第二晶粒并排间隔设置,且所述第一晶粒与第二晶粒分设于所述重布线层基板的第一中心线的两侧,当所述重布线层基板为矩形时,所述第一中心线为所述重布线层基板的长边的中心线。

13、可选地,所述重布线层基板至少有部分结构嵌入设于所述封装基板上,且所述重布线层基板的顶部暴露。

14、可选地,所述封装基板具有至少一个容置腔体,至少一个所述容置腔体暴露所述封装基板的至少一个表面,所述重布线层基板设于所述容置腔体内,且位于所述表面上。

15、可选地,当所述电源模块和晶粒单元的上部支撑安设散热模组时,所述散热模组的散热面分别与所述电源模块和晶粒单元的顶部接触。

16、可选地,所述半导体封装器件为芯片。

17、根据本发明实施例的第二个方面,提供了一种半导体器件的封装方法,所述方法包括:提供一具有互联导线的封装基板,在所述封装基板的至少一个表面上形成重布线层基板;将晶粒单元一部分连接于所述重布线层基板上,将所述晶粒单元的另一部分连接于所述封装基板上,其中,所述晶粒单元位于所述重布线层基板及封装基板的上方;在所述封装基板的表面、位于所述重布线层基板之外的位置上安装电源模块,且所述电源模块位于所述晶粒单元的周边;用封装外壳将所述电源模块及晶粒单元包覆封装。

18、可选地,所述在所述封装基板的至少一个表面上形成重布线层基板包括:

19、在所述封装基板的至少一个表面曝光显影蚀刻出至少一个容置腔体,至少一个所述容置腔体的底面暴露;

20、在所述容置腔体中、由其底面向上形成交替堆叠的介质层和金属层构成的所述重布线层基板;其中,各金属层层间相互耦合,所述介质层为绝缘材料。

21、可选地,所述在所述容置腔体中、由其底面向上形成交替堆叠的介质层和金属层构成的所述重布线层基板,包括;采用双面覆膜在该腔体内嵌入的基底材料介质上,形成具有互联导线的重布线层基板;所述基地材料介质包含所述介质层和金属层;在所述重布线层基板上表面进行电镀铜柱及焊球,形成导电凸块,以用于与晶粒单元互联。

22、可选地,将晶粒单元一部分连接于所述重布线层基板上,以及将所述晶粒单元的另一部分连接于所述封装基板上包括:将所述晶粒单元采用倒装方式贴合于所述重布线层基板与封装基板上,并将所述晶粒单元的信号引线与电源引线引出至所述封装基板外部。

23、可选地,所述晶粒单元至少包括一个第一晶粒与一个第二晶粒;将晶粒单元一部分连接于所述重布线层基板上,以及将所述晶粒单元的另一部分连接于所述封装基板上包括:将所述第一晶粒的金属接合面朝下连接于封装基板与重布线层基板二者上表面的第一侧区域,以及将第二晶粒的金属接合面朝下倒扣连接于封装基板与重布线层基板二者上表面的第二侧区域;其中,当所述重布线层基板为轴对称图形时,第一侧区域与第二侧区域关于重布线层基板的对称轴对称。

技术特征:

1.一种半导体封装器件,其特征在于,包括:封装基板;所述封装基板上具有互联导线;

2.根据权利要求1所述的半导体封装器件,其特征在于,至少有一个所述电源模块上用于安设散热模组。

3.根据权利要求1所述的半导体封装器件,其特征在于,所述电源模块包括:电源电路,所电源电路封装于壳体内。

4.根据权利要求3所述的半导体封装器件,其特征在于,所述电源模块设有一个或多个。

5.根据权利要求2所述的半导体封装器件,其特征在于,所述电源模块包括:印制线路板、开关驱动电路、电感及电容,所述开关驱动电路、电感及电容分别电连接于所述印制线路板上,且所述开关驱动电路的输出端与所述电感的输入端电连接,所述电感的输出端与所述电容的输入端电连接,所述电容的输出端电连接至所述晶粒单元的供电引脚上。

6.根据权利要求4所述的半导体封装器件,其特征在于,所述电源模块还包括:去耦电容,所述去耦电容设于所述电容的输出端到所述晶粒单元的供电引脚之间的节点上。

7.根据权利要求3或4所述的半导体封装器件,其特征在于,至少在所述电源模块外部封装的壳体、与散热器对应的表面上镀有金属层。

8.根据权利要求1所述的半导体封装器件,其特征在于,所述晶粒单元,包括:第一晶粒及第二晶粒;

9.根据权利要求7所述的半导体封装器件,其特征在于,所述第一晶粒与第二晶粒并排间隔设置,且所述第一晶粒与第二晶粒分设于所述重布线层基板的第一中心线的两侧,当所述重布线层基板为矩形时,所述第一中心线为所述重布线层基板的长边的中心线。

10.根据权利要求1或8所述的半导体封装器件,其特征在于,所述重布线层基板至少有部分结构嵌入设于所述封装基板上,且所述重布线层基板的顶部暴露。

11.根据权利要求10所述的半导体封装器件,其特征在于,所述封装基板具有至少一个容置腔体,至少一个所述容置腔体暴露所述封装基板的至少一个表面,所述重布线层基板设于所述容置腔体内,且位于所述表面上。

12.根据权利要求1所述的半导体封装器件,其特征在于,当所述电源模块和晶粒单元的上部支撑安设散热模组时,所述散热模组的散热面分别与所述电源模块和晶粒单元的顶部接触。

13.根据权利要求1所述的半导体封装器件,其特征在于,所述半导体封装器件为芯片。

14.一种半导体器件的封装方法,其特征在于,所述方法包括:

15.根据权利要求14所述的封装方法,其特征在于,所述在所述封装基板的至少一个表面上形成重布线层基板包括:

16.根据权利要求15所述的封装方法,其特征在于,所述在所述容置腔体中、由其底面向上形成交替堆叠的介质层和金属层构成的所述重布线层基板,包括;

17.根据权利要求14所述的封装方法,其特征在于,将晶粒单元一部分连接于所述重布线层基板上,以及将所述晶粒单元的另一部分连接于所述封装基板上包括:将所述晶粒单元采用倒装方式贴合于所述重布线层基板与封装基板上,并将所述晶粒单元的信号引线与电源引线引出至所述封装基板外部。

18.根据权利要求14或15所述的封装方法,其特征在于,所述晶粒单元至少包括一个第一晶粒与一个第二晶粒;

技术总结

本发明实施例公开的半导体封装器件及封装方法,涉及半导体技术领域,便于减少供电链路上的功耗损失。包括:封装基板;所述封装基板上具有互联导线,重布线层基板;所述重布线层基板布设于所述封装基板上;晶粒单元;所述晶粒单元的一部分连接于所述重布线层基板上,所述晶粒单元的另一部分连接于所述封装基板上;电源模块;所述电源模块位于所述晶粒单元的周边,且所述电源模块通过所述互联导线与所述晶粒单元电连接。本发明适用于芯片等器件封装场景中。

技术研发人员:杜树安,钱晓峰,林少芳,孟凡晓,韩亚男

受保护的技术使用者:海光信息技术股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!