半导体器件及其制造方法与流程

背景技术:

1、本公开涉及半导体器件及其制造方法,更具体地,涉及包括igbt的半导体器件及其制造方法。

2、具有低导通电阻的沟槽栅型igbt(绝缘栅双极型晶体管)被广泛使用。此外,在用于控制电动机的电源转换器等中使用包括igbt形成于其上的半导体芯片和续流二极管形成于其上的半导体芯片的半导体模块。续流二极管反向并联连接到igbt,并重复其中一个处于导通状态而另一个处于关断状态的操作。

3、例如,日本未审查专利申请公开2017-011000公开了一种逆向传导型igbt(rc-igbt),其通过将续流二极管反向并联连接到igbt而配置。igbt和续流二极管形成在同一个半导体板上,并结合在一个半导体芯片中。通过使用这种rc-igbt,可以减小功率转换器的尺寸。

技术实现思路

1、本发明人已经研究了包括rc-igbt的半导体器件(半导体芯片)。结果发现,虽然可以通过减小半导体衬底的厚度来减小导通电阻,但在关断时容易发生振铃(ringing)。例如,当半导体衬底的厚度足够大时,从形成在半导体衬底的背表面侧上的p型集电极区域重新注入空穴。结果,载流子甚至在关断结束时仍然存在,并且背表面侧的电场发生弛豫,从而不会发生振铃。如果半导体衬底的厚度太薄,则在关断结束时发生穿通。此时,由于耗尽层的厚度是波动的,因此当耗尽层厚度变得与半导体衬底的厚度大致相同时,载流子在背表面侧耗尽,产生高电场,从而发生振铃。

2、另一方面,在二极管中,在半导体衬底的背表面侧上形成n型阴极区域,并且由于没有来自背表面侧的空穴供应,耗尽层从前表面侧和背表面侧都扩展。这里,如果半导体衬底的厚度太薄,则来自前表面侧的耗尽层和来自背表面侧的损耗层被连接,发生穿通,从而发生振铃。当igbt和二极管形成在相同的半导体衬底上并且相应区域中的半导体衬底的厚度相同时,二极管更可能引起振铃。

3、因此,考虑到rc-igbt的可靠性,需要根据二极管的特性来设置半导体衬底的厚度,以便抑制振铃。也就是说,必须将半导体衬底的厚度增加到二极管中不发生振铃的程度。然而,在igbt中,由于半导体衬底的厚度不必要地增加,导通电阻增加。换言之,当优先考虑半导体器件的可靠性时,半导体器件的性能恶化。

4、因此,期望开发一种能够抑制igbt和二极管中的振铃并降低igbt的导通电阻的技术。也就是说,期望开发一种用于确保半导体器件的可靠性并提高半导体器件性能的技术。

5、从本说明书和附图的描述中,其他目的和新颖特征将变得明显。

6、下文将简要描述本申请中公开的实施方式中的典型实施方式。

7、根据一个实施方式的半导体器件包括第一区域和第二区域。此外,半导体器件包括具有前表面和背表面的第一导电类型的半导体衬底、形成在第一区域的半导体衬底上的igbt和形成在第二区域的半导体衬底上的二极管。这里,第一区域中的半导体衬底的厚度小于第二区域中的半导体衬底的厚度。

8、根据一个实施方式的制造包括第一区域和第二区域的半导体器件的方法包括以下步骤:(a)制备具有前表面和背表面的第一导电类型的半导体衬底;(b)在第一区域的半导体衬底上形成igbt,以及在第二区域的半导体衬底上形成二极管;(c)使得第一区域的半导体衬底的厚度比第二区域的半导体衬底的厚度薄。

9、根据该实施方式,可以确保半导体器件的可靠性,并且可以提高半导体器件的性能。

技术特征:

1.一种包括第一区域和第二区域的半导体器件,所述半导体器件包括:

2.根据权利要求1所述的半导体器件,其中在所述半导体衬底的所述背表面上形成台阶,使得所述第一区域中所述半导体衬底的所述背表面被定位在所述第二区域中所述半导体衬底的所述背表面上方。

3.根据权利要求2所述的半导体器件,其中在所述半导体衬底的表面上形成台阶,使得所述第一区域中所述半导体衬底的表面被定位在所述第二区域中所述半导体衬底的表面下方。

4.根据权利要求1所述的半导体器件,还包括:

5.根据权利要求4所述的半导体器件,还包括所述第二导电类型的空穴注入区域,

6.根据权利要求4所述的半导体器件,还包括在平面视图中围绕所述第一区域和所述第二区域的外周区域,

7.根据权利要求4所述的半导体器件,其中所述基极区域也形成在所述第二区域的所述半导体衬底上,

8.根据权利要求1所述的半导体器件,其中所述第一区域中的所述半导体衬底的厚度在1μm或更大并且在10μm或更小的范围内比所述第二区域中的所述半导体衬底的厚度薄。

9.一种制造包括第一区域和第二区域的半导体器件的方法,所述方法包括以下步骤:

10.根据权利要求9所述的制造半导体器件的方法,所述步骤(b)还包括:

11.根据权利要求10所述的制造半导体器件的方法,其中所述步骤(c)在所述步骤(b1)至(b8)之后且在所述步骤(b9)至(b11)之前被执行,并且所述步骤(c)还包括:

12.根据权利要求11所述的制造半导体器件的方法,其中所述步骤(c)在所述步骤(b8)之后且在所述步骤(c1)之前被执行,并且其中所述步骤(c)还包括以下步骤(c0):抛光所述第一区域和所述第二区域中的所述半导体衬底的所述背表面以减薄所述半导体衬底的厚度。

13.根据权利要求11所述的制造半导体器件的方法,其中所述步骤(c)在所述步骤(a)之后并且在所述步骤(b1)至(b11)之前被执行,

14.根据权利要求11所述的制造半导体器件的方法,其中在所述步骤(a)中制备的所述半导体衬底设置有沿<110>方向处理的取向平面,

15.根据权利要求11所述的制造半导体器件的方法,其中在所述步骤(a)中制备的所述半导体衬底设置有沿<110>方向处理的取向平面,

16.根据权利要求11所述的制造半导体器件的方法,其中在所述步骤(a)中制备的所述半导体衬底设置有沿<110>方向处理的取向平面,

17.根据权利要求10所述的制造半导体器件的方法,其中所述步骤(b)在所述步骤(b8)之后且在所述步骤(b11)之前执行,

18.根据权利要求10所述的制造半导体器件的方法,其中所述半导体衬底还包括在平面视图中围绕所述第一区域和所述第二区域的外周区域,

19.根据权利要求10所述的制造半导体器件的方法,其中在所述步骤(b4)中,所述基极区域也形成在所述第二区域的所述半导体衬底上,

20.根据权利要求9所述的制造半导体器件的方法,其中在所述步骤(c)之后,所述第一区域中的所述半导体衬底的厚度比所述第二区域中的所述半导体衬底的厚度薄1μm或更大且10μm或更小的范围。

技术总结

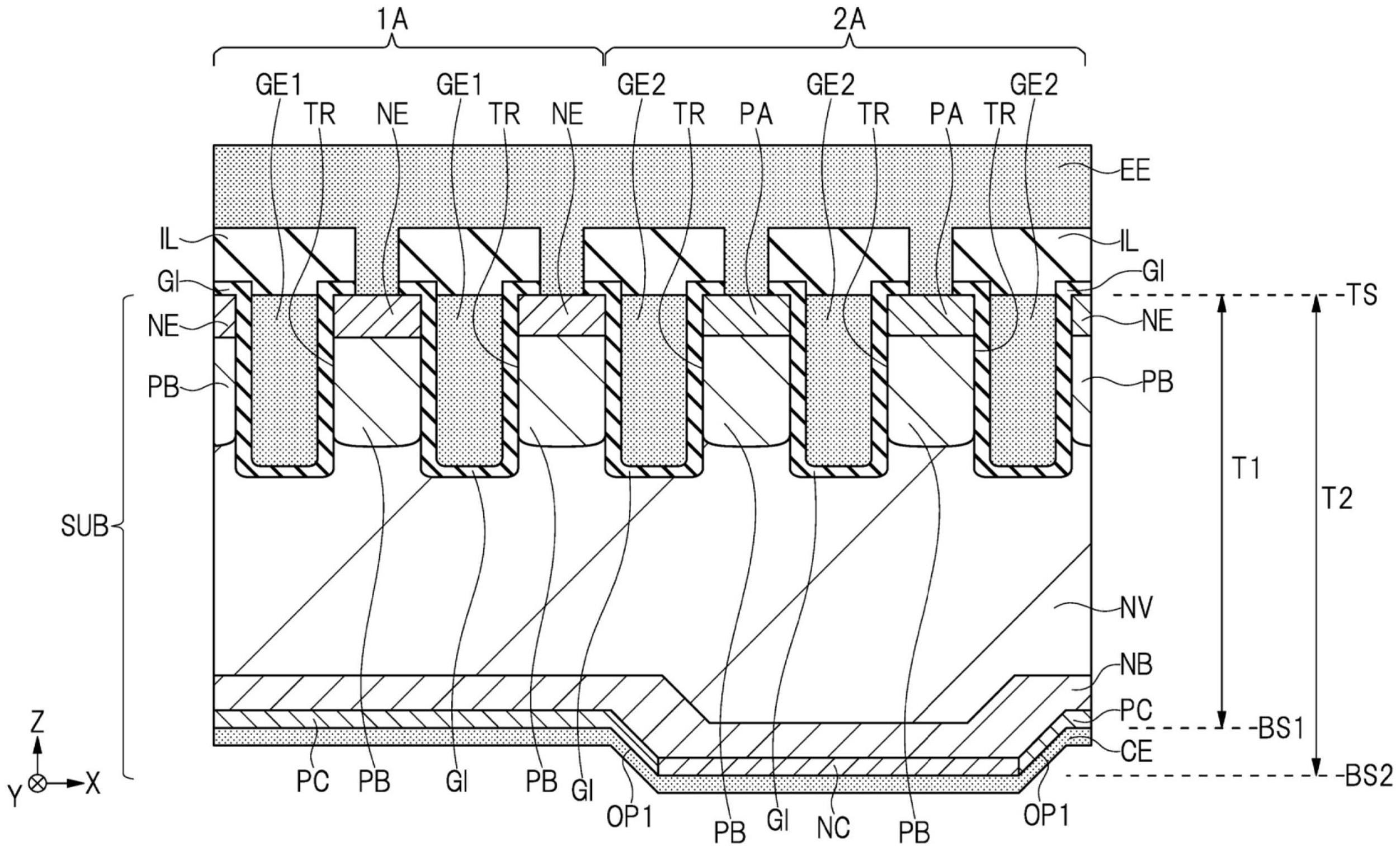

本公开的各种实施例涉及一种半导体器件及其制造方法。确保了半导体器件的可靠性,并且提高了器件的性能。包括区域1A和区域2A的半导体器件包括具有前表面BS1、BS2和背表面SUB的n型半导体衬底TS、形成在区域1A中的半导体衬底上的IGBT和形成在区域2A中的半导体衬底SUB上的二极管。而且区域1A中的半导体衬底SUB的厚度T1小于区域2A中的半导体衬底的厚度T2。

技术研发人员:小清水亮,中柴康隆,松浦仁

受保护的技术使用者:瑞萨电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!