一种存储器及其制造方法、电子设备与流程

本公开实施例涉及但不限于半导体领域,具体涉及一种存储器及其制造方法、电子设备。

背景技术:

1、动态随机存取存储器(dynamicrandomaccessmemory,dram)是一种半导体存储器,和静态存储器相比,dram存储器具有结构较为简单、制造成本较低、容量密度较高的优点,随着技术的发展,dram存储器的应用日益广泛。

2、随着互联网技术的发展,存储数据量实现大幅增长,hpc(high-performancecomputing)芯片和ai芯片(artificialintelligencechip)对高带宽存储的需求有增无减。常规的高带宽存储器基于常规的2.5d封装,芯片(die)与芯片(die)之间通过微米级硅微纳孔(tsv)连接,难以进一步微缩提升带宽和能效。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、第一方面,本公开实施例提供了一种存储器,包括:

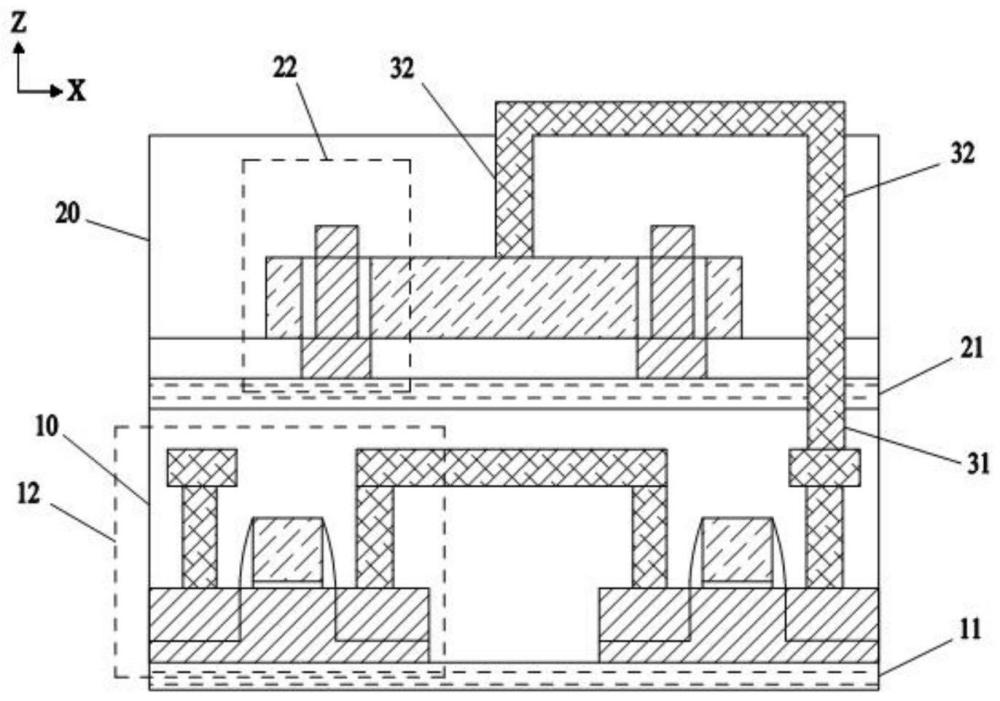

3、第一结构层,包括第一衬底以及设置在所述第一衬底上的逻辑电路,所述逻辑电路包括间隔设置在所述第一衬底上的多个逻辑晶体管,所述多个逻辑晶体管依次电连接;

4、第二结构层,层叠设置在所述第一结构层上,所述第二结构层包括第二衬底以及设置在所述第二衬底上的存储电路,所述存储电路包括至少一个存储单元,所述存储单元包括至少一个存储晶体管;

5、所述第一结构层中设置有与所述逻辑电路连通的第一通孔,所述第二结构层中设置有与所述存储电路连通的第二通孔,所述第一通孔与所述第二通孔互相连通,所述存储电路通过所述第一通孔和所述第二通孔,与所述逻辑电路连接。

6、在示例性实施例中,所述第一结构层还包括设置在所述第一衬底上第一复合绝缘层,所述第一复合绝缘层覆盖所述逻辑晶体管,所述第二结构层设置在所述第一复合绝缘层上,所述第一复合绝缘层中设置有所述第一通孔。

7、在示例性实施例中,所述第二结构层还包括设置在所述第二衬底上的第二复合绝缘层,所述第二复合绝缘层覆盖所述存储电路,所述第二通孔包括间隔设置在所述第二复合绝缘层中的第一子孔和第二子孔,所述第一子孔与所述存储电路连通,所述第二子孔与所述第一通孔连通。

8、在示例性实施例中,所述第二子孔与所述第一通孔在所述第一衬底上的正投影存在交叠。

9、在示例性实施例中,所述存储晶体管包括:

10、设置在所述第二衬底上的有源柱,所述有源柱包括沿着远离所述第二衬底方向依次设置的源极接触端、沟道区以及漏极接触端;

11、第一栅电极,环绕设置在所述沟道区的外侧,所述第一栅电极与所述沟道区相互绝缘;

12、位线,与所述漏极接触端连接;

13、字线,与所述第一栅电极连接。

14、在示例性实施例中,所述存储晶体管为n型金属氧化物半导体晶体管。

15、在示例性实施例中,所述逻辑晶体管包括设置在所述第一衬底上的有源层以及设置在所述有源层上的第二栅电极、源电极和漏电极,所述源电极和所述漏电极分别与所述有源层连接,所述第二栅电极与所述有源层之间设置有栅极绝缘层,所述第二栅电极的材料为金属材料,所述栅极绝缘层的材料为高介电常数材料。

16、在示例性实施例中,一个存储单元包括一个存储晶体管。

17、在示例性实施例中,多个存储晶体管间隔排列形成存储晶体管行或存储晶体管列,同一存储晶体管行或存储晶体管列的存储晶体管的栅电极相连。

18、在示例性实施例中,所述第一通孔和所述第二通孔均为纳米级通孔。

19、第二方面,本公开实施例还提供了一种电子设备,包括前述的存储器。

20、在示例性实施例中,所述电子设备包括智能电话、计算机、平板电脑、人工智能、可穿戴设备或智能移动终端。

21、第三方面,本公开实施例还提供了一种存储器的制造方法,包括:

22、形成第一结构层,所述第一结构层包括第一衬底以及设置在所述第一衬底上的逻辑电路,所述逻辑电路包括间隔设置在所述第一衬底上的多个逻辑晶体管,所述多个逻辑晶体管依次电连接;

23、在所述第一结构层上形成第二结构层,所述第二结构层包括第二衬底以及设置在所述第二衬底上的存储电路,所述存储电路包括至少一个存储单元,所述存储单元包括至少一个存储晶体管;

24、在所述第一结构层中形成与所述逻辑晶体管连通的第一通孔,在所述第二结构层中形成与所述存储电路连通的第二通孔,所述第一通孔与所述第二通孔互相连通;

25、对所述第一通孔和所述第二通孔进行互连工艺,使所述存储电路通过所述第一通孔和所述第二通孔,与所述逻辑电路连接。

26、在示例性实施例中,在所述第一结构层上形成第二结构层包括:

27、在所述第二衬底上形成半导体层;

28、将所述第二衬底与所述第一结构层键合;

29、对所述半导体层进行图案化工艺,以形成有源结构层;

30、使所述有源结构层形成存储晶体管。

31、在示例性实施例中,使所述有源结构层形成存储晶体管包括:

32、通过硬掩膜工艺,刻蚀部分所述有源结构层,使远离所述第二衬底一侧的部分有源结构层形成半导体柱,保留靠近所述第二衬底一侧的部分有源结构层;所述半导体柱包括第一沟道区以及漏极接触端;

33、通过图案化工艺,图案化保留的有源结构层,使保留的有源结构层形成源极接触端,所述源极接触端、第一沟道区以及漏极接触端形成有源柱;

34、形成环绕所述第一沟道区的第一栅电极。

35、本申请实施例存储器通过将第二结构层层叠设置在第一结构层上,使存储电路通过第一通孔和第二通孔,与逻辑电路连接,从而提升存储器的集成度,实现更高带宽存储。

36、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种存储器,其特征在于,包括:

2.根据权利要求1所述的存储器,其特征在于,所述第一结构层还包括设置在所述第一衬底上第一复合绝缘层,所述第一复合绝缘层覆盖所述逻辑晶体管,所述第二结构层设置在所述第一复合绝缘层上,所述第一复合绝缘层中设置有所述第一通孔。

3.根据权利要求1所述的存储器,其特征在于,所述第二结构层还包括设置在所述第二衬底上的第二复合绝缘层,所述第二复合绝缘层覆盖所述存储电路,所述第二通孔包括间隔设置在所述第二复合绝缘层中的第一子孔和第二子孔,所述第一子孔与所述存储电路连通,所述第二子孔与所述第一通孔连通。

4.根据权利要求3所述的存储器,其特征在于,所述第二子孔与所述第一通孔在所述第一衬底上的正投影存在交叠。

5.根据权利要求1至4任一所述的存储器,其特征在于,所述存储晶体管包括:

6.根据权利要求1至4任一所述的存储器,其特征在于,所述存储晶体管为n型金属氧化物半导体晶体管。

7.根据权利要求1至4任一所述的存储器,其特征在于,所述逻辑晶体管包括设置在所述第一衬底上的有源层以及设置在所述有源层上的第二栅电极、源电极和漏电极,所述源电极和所述漏电极分别与所述有源层连接,所述第二栅电极与所述有源层之间设置有栅极绝缘层,所述第二栅电极的材料为金属材料,所述栅极绝缘层的材料为高介电常数材料。

8.根据权利要求1至4任一所述的存储器,其特征在于,一个存储单元包括一个存储晶体管。

9.根据权利要求1至4任一所述的存储器,其特征在于,多个存储晶体管间隔排列形成存储晶体管行或存储晶体管列,同一存储晶体管行或存储晶体管列的存储晶体管的栅电极相连。

10.根据权利要求1至4任一所述的存储器,其特征在于,所述第一通孔和所述第二通孔均为纳米级通孔。

11.一种电子设备,其特征在于,包括权利要求1至10任一所述的存储器。

12.根据权利要求11所述的电子设备,其特征在于,所述电子设备包括智能电话、计算机、平板电脑、人工智能、可穿戴设备或智能移动终端。

13.一种存储器的制造方法,其特征在于,包括:

14.根据权利要求13所述的存储器的制造方法,其特征在于,在所述第一结构层上形成第二结构层包括:

15.根据权利要求14所述的存储器的制造方法,其特征在于,使所述有源结构层形成存储晶体管包括:

技术总结

一种存储器及其制造方法、电子设备,该存储器包括:第一结构层,包括第一衬底以及设置在所述第一衬底上的逻辑电路,所述逻辑电路包括间隔设置在所述第一衬底上的多个逻辑晶体管,所述多个逻辑晶体管依次电连接;第二结构层,层叠设置在所述第一结构层上,所述第二结构层包括第二衬底以及设置在所述第二衬底上的存储电路,所述存储电路包括至少一个存储单元,所述存储单元包括至少一个存储晶体管;所述第一结构层中设置有与所述逻辑电路连通的第一通孔,所述第二结构层中设置有与所述存储电路连通的第二通孔,所述第一通孔与所述第二通孔互相连通,所述存储电路通过所述第一通孔和所述第二通孔,与所述逻辑电路连接。

技术研发人员:毛淑娟,王桂磊,赵超,项金娟

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!