半导体封装结构及其制作方法与流程

本发明的实施例涉及半导体器件,特别地,涉及改善半导体器件的可靠性以及焊接面积的一种半导体封装结构及其制作方法。

背景技术:

1、随着电源芯片功率密度不断增加,单芯片需要承载的电流能力要求越来越高,相应的,焊线直径需要不断变粗以满足大电流和低电阻的需求。

2、再布线层的引入很好的提升了焊接位置的灵活性,同时解决了粗线径引起的焊接质量问题,如铝层破裂和衬底弹坑。但产品在高温高湿环境中,再布线层的铜金属容易因为电化学腐蚀,形成铜树枝状凸起,引起漏电甚至短路,存在严重的可靠性风险。

3、用绝缘层覆盖再布线层表面可以有效降低电化学腐蚀风险,但绝缘层会覆盖部分再布线层表面,减少可焊接面积,同时也会影响到焊球质量检查中的推球项目的测量效果。

技术实现思路

1、针对现有技术中的一个或多个问题,本发明提供一种半导体封装结构及其制作方法。

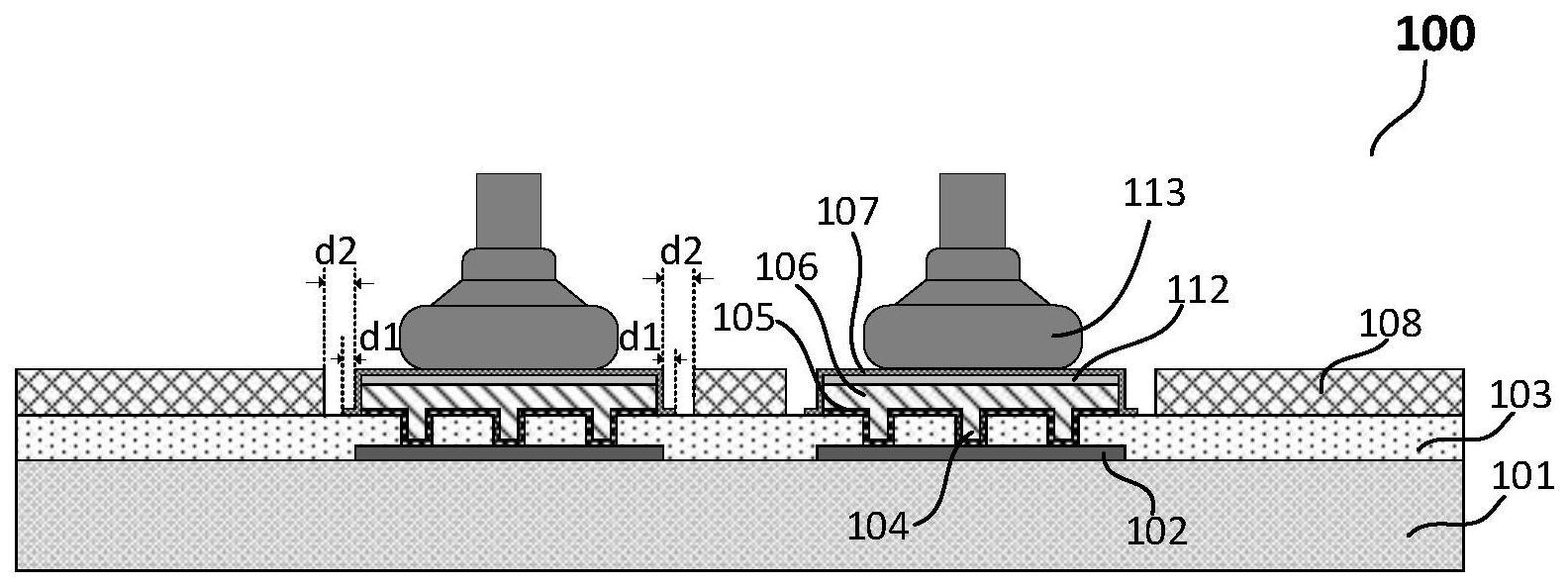

2、本发明的第一方面提出一种半导体封装结构,包括:半导体衬底,包括至少一个导电焊盘制作于该半导体衬底上;钝化层,覆盖所述半导体衬底;多个通孔,每个通孔穿过所述钝化层直至暴露出部分所述导电焊盘;导电性再布线层,填充所述多个通孔并覆盖部分所述钝化层;焊接层,形成在所述导电性再布线层的顶面;以及腐蚀阻挡层,完全覆盖所述焊接层的顶面和侧面、所述导电性再布线层的侧面,并从所述导电性再布线层的侧面根部向外延伸覆盖部分钝化层的顶面,其中,所述腐蚀阻挡层在钝化层顶面上向外延伸的宽度为第一宽度。

3、本申请的第二方面提出一种半导体器件的制作方法,包括:在半导体衬底上制作钝化层;在所述钝化层中制作多个通孔;形成导电性再布线层,所述导电性再布线层填充所述多个通孔并覆盖所述钝化层的一部分;在所述导电性再布线层的顶面制作焊接层;以及在所述焊接层的顶面和侧面、所述导电性再布线层的侧面以及与所述导电性再布线层的侧面根部相邻的钝化层顶面上形成腐蚀阻挡层,其中,所述腐蚀阻挡层在钝化层顶面上从所述导电性再布线层的侧面根部向外延伸的宽度为第一宽度。

4、本发明提供的半导体封装结构的可靠性高,焊接面积大,有利于大电流场合使用,同时可靠性高,工艺步骤简单。

技术特征:

1.一种半导体封装结构,其特征在于,所述封装结构包括:

2.如权利要求1所述的封装结构,其特征在于,所述封装结构进一步包括至少一个导电凸点,所述至少一个导电凸点形成于腐蚀阻挡层的顶面上。

3.如权利要求2所述的封装结构,其特征在于,所述封装结构进一步包括:

4.如权利要求3所述的封装结构,其特征在于,所述导电性再布线层侧面的腐蚀阻挡层与相邻绝缘层之间具有空隙,空隙宽度为第二宽度,其中,第二宽度大于第一宽度。

5.如权利要求2所述的封装结构,其特征在于,所述导电凸点包括焊球。

6.如权利要求1所述的封装结构,其特征在于,所述腐蚀阻挡层的厚度为0.1微米至0.5微米。

7.如权利要求1所述的封装结构,其特征在于,所述焊接层包括镍。

8.如权利要求1所述的封装结构,其特征在于,所述封装结构进一步包括:

9.一种半导体器件的制作方法,其特征在于,所述制作方法包括:

10.如权利要求9所述的制作方法,其特征在于,所述制作方法进一步包括:

11.如权利要求10所述的制作方法,其特征在于,所述制作方法进一步包括:

12.如权利要求10所述的制作方法,其特征在于,在所述焊接层的顶面和侧面、所述导电性再布线层的侧面以及与所述导电性再布线层的侧面根部相邻的钝化层顶面上形成腐蚀阻挡层的步骤包括:

技术总结

公开了一种半导体封装结构及其制作方法。该半导体封装结构具有导电性再布线层、焊接层、腐蚀阻挡层和绝缘层。腐蚀阻挡层用于完全覆盖焊接层和导电性再布线层,并形成致密接触。绝缘层形成在所述钝化层的顶面用于将每个导电凸点下对应的腐蚀阻挡层与其他相邻导电凸点下的腐蚀阻挡层相互之间隔开。由于腐蚀阻挡层的顶面不再涂覆绝缘层,因此在腐蚀阻挡层上用于制作导电凸点的面积很大,可满足更大电流的需求。此外,腐蚀阻挡层同时也可作为导电凸点焊接时的焊接粘合层,减少了工艺步骤。

技术研发人员:万亮

受保护的技术使用者:晶艺半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!