封装结构、电子设备及封装结构的制备方法与流程

本发明涉及半导体封装,更具体地,本发明涉及一种封装结构、电子设备及封装结构的制备方法。

背景技术:

1、随着消费类电子产品的不断更新演进,产品的小型化发展已经成为了新的需求。sip(system in package)技术由于具有较高的集成度和小型化优势,广泛应用于消费类电子产品中,通过sip技术能够将复杂多样的芯片进行集成封装,便于消费类电子产品的小型化发展。

2、为了实现电子产品的通信功能,还需要再增加天线模块。目前的电子产品,通常将天线模块贴设于sip封装结构的上方或者下方,以能够实现通信功能。然而,这导致天线模块很容易对sip封装结构内部的芯片造成干扰,影响了电子产品的正常工作。

技术实现思路

1、鉴于上述现有技术的缺点,本发明的目的在于提供一种新型的封装结构、电子设备及封装结构的制备方法,旨在解决现有技术中的至少一个问题。

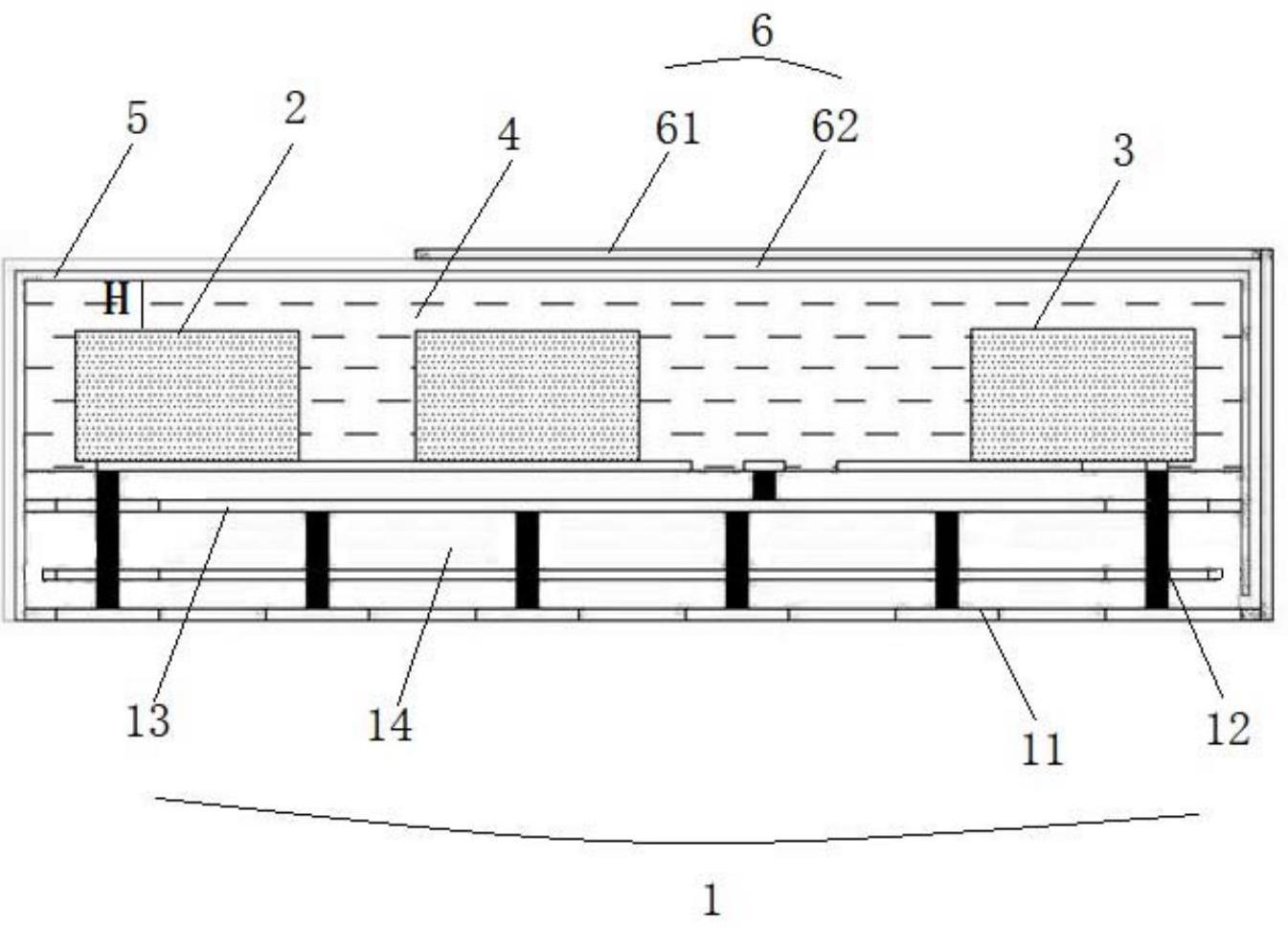

2、根据本发明的一个方面,提供了一种封装结构。所述封装结构包括:

3、基底;

4、第一芯片和第二芯片,所述第一芯片和所述第二芯片均设置于所述基底上;

5、封装层,所述封装层设置于所述基底靠近所述第一芯片的一侧,且所述封装层包覆所述第一芯片和所述第二芯片;

6、屏蔽层,所述屏蔽层设置于所述封装层远离所述基底的一侧,所述屏蔽层至少覆盖所述封装层并延伸至所述基底,以使所述屏蔽层与所述基底之间形成电连接;

7、天线模块,所述天线模块设置于所述屏蔽层远离所述基底的一侧,所述天线模块的一端与所述基底相连,以使所述天线模块能够通过所述基底与所述第二芯片之间形成电连接。

8、可选地,所述屏蔽层的厚度范围为6微米至10微米,所述屏蔽层与所述第一芯片之间的最小距离范围为70微米至130微米。

9、可选地,所述屏蔽层包括相连的顶壁和侧壁,所述天线模块位于所述屏蔽层的顶壁或侧壁上。

10、可选地,所述基底上还设置有馈线,所述天线模块的一端与所述馈线连接。

11、可选地,所述天线模块包括天线和第一绝缘层,所述第一绝缘层设置于所述屏蔽层远离所述基底的一侧,所述天线设置于所述第一绝缘层远离所述屏蔽层的一侧,所述天线的一端与所述基底相连,以使所述天线能够通过所述基底与所述第二芯片电连接。

12、可选地,所述第一绝缘层为聚酰亚胺层,所述第一绝缘层的厚度范围为3微米至6微米。

13、可选地,所述天线包括微带天线,所述微带天线呈阵列排布。

14、可选地,所述第一芯片为敏感芯片,所述第一芯片的数量为一个或者多个。

15、可选地,所述第二芯片为射频芯片,所述天线模块通过所述基底与所述射频芯片形成电连接。

16、可选地,所述基底包括连接层,所述基底上还开设有连接通道,所述连接通道的一端与所述射频芯片相连,所述连接通道的另一端与所述连接层相连,所述连接层与所述天线模块的一端相连。

17、可选地,所述基底还包括接地层和第二绝缘层,所述接地层与所述连接层平行设置,且所述接地层与所述屏蔽层相连,所述第二绝缘层设置于所述连接层与所述接地层之间。

18、可选地,所述连接层和所述接地层均为金属层,所述基底的厚度范围为150微米至350微米。

19、根据本发明的另一个方面,提供了一种电子设备。该电子设备包括上述任意一项所述的封装结构。

20、根据本发明的再一个方面,提供了一种封装结构的制备方法。所述制备方法包括:

21、制作基底;

22、将第一芯片和第二芯片依次设置于所述基底上;

23、在所述基底靠近所述第一芯片的一侧制作封装层,且所述封装层包覆所述第一芯片和所述第二芯片;

24、在所述封装层远离所述基底的一侧制作屏蔽层,所述屏蔽层至少覆盖所述封装层并延伸至所述基底,以使所述屏蔽层与所述基底之间形成电连接;

25、在所述屏蔽层远离所述基底的一侧制作天线模块,所述天线模块的一端与所述基底相连,以使所述天线模块能够通过所述基底与所述第二芯片之间形成电连接。

26、可选地,所述制作基底包括:

27、制作连接层、接地层和第二绝缘层,所述第二绝缘层设置于所述连接层与所述接地层之间,且所述连接层和所述接地层均包括延伸段,所述延伸段的长度范围为80微米至120微米。

28、可选地,所述在所述封装层远离所述基底的一侧制作屏蔽层,包括:

29、去除所述延伸段,以使所述连接层外露;

30、将第一uv胶膜设置在所述连接层的外露部分以对所述连接层的外露部分形成覆盖;

31、制作屏蔽层,所述屏蔽层与所述接地层相连;

32、去除所述第一uv胶膜,以使所述连接层外露。

33、可选地,所述在所述屏蔽层远离所述基底的一侧制作天线模块,包括:

34、在所述屏蔽层远离所述基底的一侧设置第一绝缘层,并保持所述连接层外露;

35、在所述第一绝缘层远离所述屏蔽层的一侧设置第二uv胶膜,所述第二uv胶膜包括镂空部分,所述镂空部分的形状与天线的形状相同;

36、在所述第二uv胶膜远离所述第一绝缘层的一侧设置金属层,并去除所述第二uv胶膜,以形成所述天线模块。

37、本发明的一个技术效果在于,通过在封装层远离基底的一侧设置屏蔽层,且屏蔽层至少覆盖封装层并延伸至基底,以能够利用屏蔽层屏蔽外界天线信号或者其它信号对封装结构内的第一芯片和第二芯片的干扰,从而保证第一芯片和第二芯片能够正常工作。

38、通过以下参照附图对本发明的示例性实施例的详细描述,本发明的其它特征及其优点将会变得清楚。

技术特征:

1.一种封装结构,其特征在于,包括:

2.根据权利要求1所述的一种封装结构,其特征在于,所述屏蔽层(5)的厚度范围为6微米至10微米,所述屏蔽层(5)与所述第一芯片(2)之间的最小距离范围为70微米至130微米。

3.根据权利要求1所述的一种封装结构,其特征在于,所述屏蔽层(5)包括相连的顶壁和侧壁,所述天线模块(6)位于所述屏蔽层(5)的顶壁或侧壁上。

4.根据权利要求1所述的一种封装结构,其特征在于,所述基底(1)上还设置有馈线,所述天线模块(6)的一端与所述馈线连接。

5.根据权利要求1所述的一种封装结构,其特征在于,所述天线模块(6)包括天线(61)和第一绝缘层(62),所述第一绝缘层(62)设置于所述屏蔽层(5)远离所述基底(1)的一侧,所述天线(61)设置于所述第一绝缘层(62)远离所述屏蔽层(5)的一侧,所述天线(61)的一端与所述基底(1)相连,以使所述天线(61)能够通过所述基底(1)与所述第二芯片(3)电连接。

6.根据权利要求5所述的一种封装结构,其特征在于,所述第一绝缘层(62)为聚酰亚胺层,所述第一绝缘层(62)的厚度范围为3微米至6微米。

7.根据权利要求5所述的一种封装结构,其特征在于,所述天线(61)包括微带天线,所述微带天线呈阵列排布。

8.根据权利要求1所述的一种封装结构,其特征在于,所述第一芯片(2)为敏感芯片,所述第一芯片(2)的数量为一个或者多个。

9.根据权利要求1所述的一种封装结构,其特征在于,所述第二芯片(3)为射频芯片,所述天线模块(6)通过所述基底(1)与所述射频芯片形成电连接。

10.根据权利要求9所述的一种封装结构,其特征在于,所述基底(1)包括连接层(11),所述基底(1)上还开设有连接通道(12),所述连接通道(12)的一端与所述射频芯片相连,所述连接通道(12)的另一端与所述连接层(11)相连,所述连接层(11)与所述天线模块(6)的一端相连。

11.根据权利要求10所述的一种封装结构,其特征在于,所述基底(1)还包括接地层(13)和第二绝缘层(14),所述接地层(13)与所述连接层(11)平行设置,且所述接地层(13)与所述屏蔽层(5)相连,所述第二绝缘层(14)设置于所述连接层(11)与所述接地层(13)之间。

12.根据权利要求11所述的一种封装结构,其特征在于,所述连接层(11)和所述接地层(13)均为金属层,所述基底(1)的厚度范围为150微米至350微米。

13.一种电子设备,其特征在于,包括权利要求1至12中任意一项所述的封装结构。

14.一种封装结构的制备方法,其特征在于,包括:

15.根据权利要求14所述的一种封装结构的制备方法,其特征在于,所述制作基底包括:

16.根据权利要求15所述的一种封装结构的制备方法,其特征在于,所述在所述封装层远离所述基底的一侧制作屏蔽层,包括:

17.根据权利要求16所述的一种封装结构的制备方法,其特征在于,所述在所述屏蔽层远离所述基底的一侧制作天线模块,包括:

技术总结

本发明公开了一种封装结构、电子设备及封装结构的制备方法。所述封装结构包括基底、第一芯片和第二芯片、封装层、屏蔽层和天线模块。所述封装层设置于所述基底靠近所述第一芯片的一侧,且所述封装层包覆所述第一芯片和所述第二芯片。本发明的一个技术效果在于,通过在封装层远离基底的一侧设置屏蔽层,且屏蔽层至少覆盖封装层并延伸至基底,以能够利用屏蔽层屏蔽外界天线信号或者其它信号对封装结构内的第一芯片和第二芯片的干扰,从而保证第一芯片和第二芯片能够正常工作。

技术研发人员:吴海鸿

受保护的技术使用者:青岛歌尔微电子研究院有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!