多芯片封装结构及其制造方法、晶圆级封装方法与流程

本公开涉及芯片封装,特别涉及一种多芯片封装结构及其制造方法、晶圆级封装方法。

背景技术:

1、多芯片封装技术是将多个具有不同功能或相同功能的晶片(die)一并封装到同一基板(substrate)或导线架(lead frame)上,并通过基板或导线架与外部电路电性连接。相较于多个独立封装结构芯片,多芯片封装结构具有更快的传输速度、更短的传输路径以及更佳的电气特性,并进一步缩小芯片封装结构的尺寸及面积,因而使得多芯片封装技术已经普遍应用于各种电子产品之中,并成为未来的主流产品。

技术实现思路

1、本公开提供一种多芯片封装结构及其制造方法、晶圆级封装方法。

2、第一方面,本公开提供了一种多芯片封装结构的制造方法,该制造方法包括:

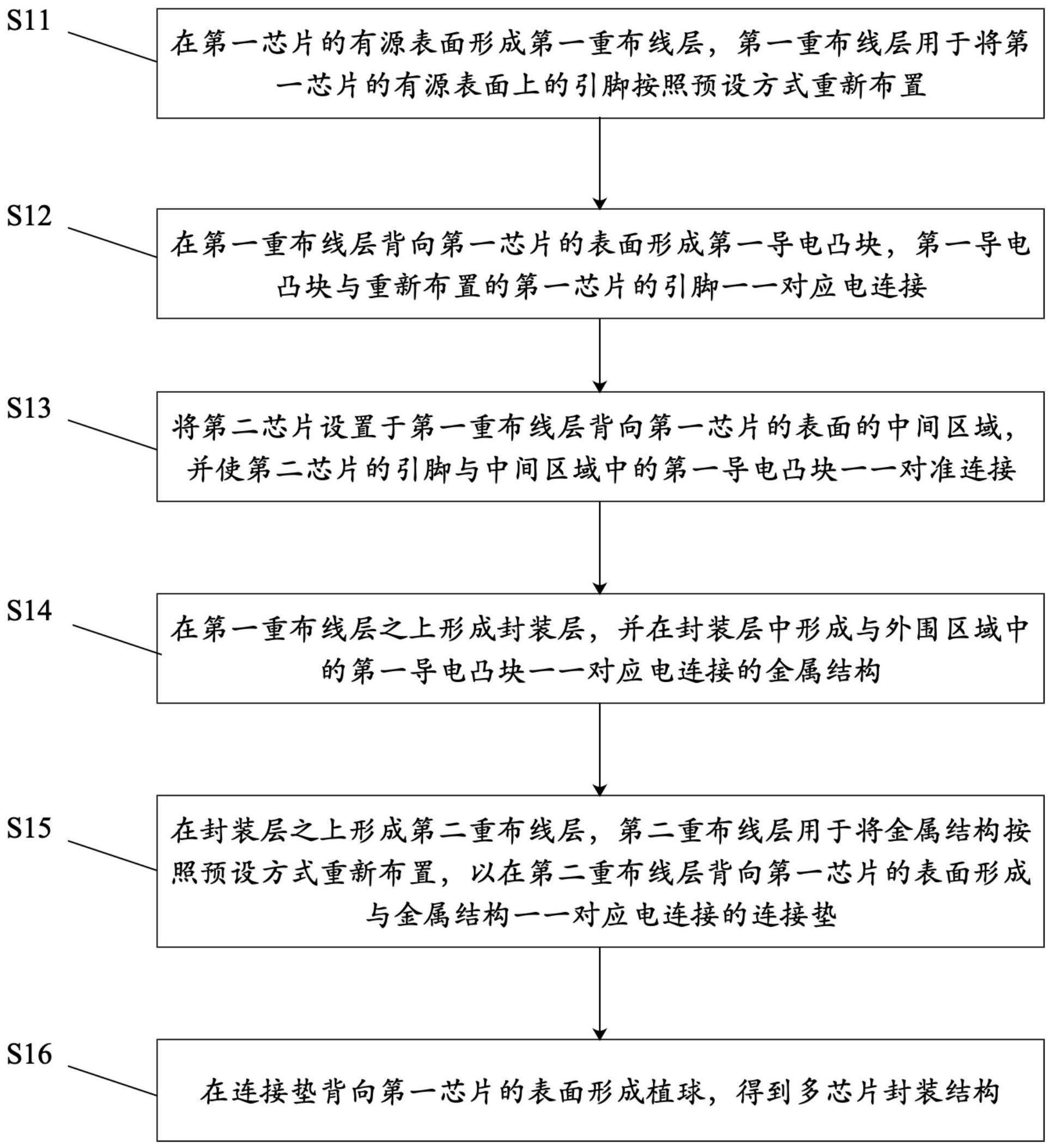

3、在第一芯片的有源表面形成第一重布线层,并在所述第一重布线层背向所述第一芯片的表面形成第一导电凸块,所述第一重布线层用于将所述第一芯片的所述有源表面上的引脚按照预设方式重新布置,所述第一导电凸块与重新布置的所述第一芯片的引脚一一对应电连接,所述第一重布线层背向所述第一芯片的表面包括中间区域和位于所述中间区域周边的外围区域,所述中间区域具有至少一个所述第一导电凸块,且所述外围区域具有至少一个所述第一导电凸块;

4、将第二芯片设置于所述第一重布线层背向所述第一芯片的表面的中间区域,并使所述第二芯片的引脚与所述中间区域中的所述第一导电凸块一一对准连接;

5、在所述第一重布线层之上形成封装层,并在所述封装层中形成与所述外围区域中的第一导电凸块一一对应电连接的金属结构;

6、在所述封装层之上形成第二重布线层,所述第二重布线层用于将金属结构按照预设方式重新布置,以在所述第二重布线层背向所述第一芯片的表面形成与金属结构一一对应电连接的连接垫;

7、在所述连接垫背向所述第一芯片的表面形成植球,得到多芯片封装结构。

8、第二方面,本公开提供了一种晶圆级封装方法,该晶圆级封装方法包括:

9、提供晶圆,所述晶圆包含所述多个第一芯片;

10、针对所述晶圆上的每个第一芯片,在所述第一芯片的有源表面形成第一重布线层,并在所述第一重布线层背向所述第一芯片的表面形成第一导电凸块,所述第一重布线层用于将所述第一芯片的所述有源表面上的引脚按照预设方式重新布置,所述第一导电凸块与重新布置的所述第一芯片的引脚一一对应电连接,所述第一重布线层背向所述第一芯片的表面包括中间区域和位于所述中间区域周边的外围区域,所述中间区域具有至少一个所述第一导电凸块,且所述外围区域具有至少一个所述第一导电凸块;

11、将第二芯片设置于所述第一重布线层背向所述第一芯片的表面的中间区域,并使所述第二芯片的引脚与所述中间区域中的所述第一导电凸块一一对准连接;

12、在所述第一重布线层之上形成封装层,并在所述封装层中形成与所述外围区域中的第一导电凸块一一对应电连接的金属结构;

13、在所述封装层之上形成第二重布线层,所述第二重布线层用于将金属结构按照预设方式重新布置,以在所述第二重布线层背向所述第一芯片的表面形成与金属结构一一对应电连接的连接垫;

14、在所述连接垫背向所述第一芯片的表面形成植球;

15、对所述晶圆进行切割,得到多个多芯片封装结构。

16、第三方面,本公开提供了一种多芯片封装结构,该多芯片封装结构包括:

17、第一芯片;

18、在所述第一芯片的有源表面设置的第一重布线层,所述第一重布线层用于将所述第一芯片的所述有源表面上的引脚按照预设方式重新布置;

19、在所述第一重布线层背向所述第一芯片的表面设置的第一导电凸块,所述第一导电凸块与重新布置的所述第一芯片的引脚一一对应电连接,所述第一重布线层背向所述第一芯片的表面包括中间区域和位于所述中间区域周边的外围区域,所述中间区域具有至少一个所述第一导电凸块,且所述外围区域具有至少一个所述第一导电凸块;

20、设置于所述第一重布线层背向所述第一芯片的表面的中间区域的第二芯片,所述第二芯片的引脚与所述中间区域中的所述第一导电凸块一一对准连接;

21、在所述第一重布线层之上设置的封装层,所述封装层中形成有与所述外围区域中的第一导电凸块一一对应电连接的金属结构;

22、在所述封装层之上设置的第二重布线层,所述第二重布线层用于将金属结构按照预设方式重新布置,以在所述第二重布线层背向所述第一芯片的表面形成与金属结构一一对应电连接的连接垫;

23、在所述连接垫背向所述第一芯片的表面设置的植球。

24、第四方面,本公开提供了一种多芯片封装结构,该多芯片封装结构包括:

25、第一芯片;

26、在所述第一芯片的有源表面设置的第一重布线层,所述第一重布线层用于将所述第一芯片的所述有源表面上的引脚按照预设方式重新布置;

27、在所述第一重布线层背向所述第一芯片的表面设置的第一导电凸块,所述第一导电凸块与重新布置的所述第一芯片的引脚一一对应电连接,所述第一重布线层背向所述第一芯片的表面包括中间区域和位于所述中间区域周边的外围区域,所述中间区域具有至少一个所述第一导电凸块,且所述外围区域具有至少一个所述第一导电凸块;

28、设置于所述第一重布线层背向所述第一芯片的表面的中间区域的第二芯片,所述第二芯片的引脚与所述中间区域中的所述第一导电凸块一一对准连接;

29、在所述第二芯片之上设置的第三芯片;

30、在所述第一重布线层之上设置的封装层,所述封装层中形成有与所述外围区域中的第一导电凸块一一对应电连接的金属结构,所述第三芯片背向所述第一芯片的有源表面与所述封装层背向所述第一芯片的表面平齐;

31、在所述封装层之上设置的第二重布线层,所述第二重布线层用于将金属结构按照预设方式重新布置,以在所述第二重布线层背向所述第一芯片的表面形成与金属结构一一对应电连接的连接垫,所述第二重布线层覆盖所述第三芯片背向所述第一芯片的有源表面与所述封装层背向所述第一芯片的表面,且所述第三芯片的有源表面上的引脚通过所述第二重布线层与所述外围区域中的金属结构连接;

32、在所述连接垫背向所述第一芯片的表面设置的植球。

33、根据本公开实施例提供的多芯片封装结构及其制造方法、晶圆级封装方法的技术方案,多芯片之间通过rdl重布线方式进行电连接,无需采用tsv技术,一方面,在不采用高级复杂工艺制程的情况下,能够实现3d封装并提高单位面积的集成度,有利于提升芯片的整体性能;另一方面,能够有利于降低工艺复杂度,节省工艺制程,降低成本,且有利于提高产品良率。

34、应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特征,也不用于限制本公开的范围。本公开的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种多芯片封装结构的制造方法,其特征在于,包括:

2.根据权利要求1所述的制造方法,其特征在于,在所述将第二芯片设置于所述第一重布线层背向所述第一芯片的表面的中间区域之前,所述制造方法还包括:

3.根据权利要求1所述的制造方法,其特征在于,所述第二芯片与所述第一芯片之间通过电镀方式电连接或者通过凸点bump电连接。

4.根据权利要求1所述的制造方法,其特征在于,所述在所述封装层中形成与在所述外围区域的第一导电凸块一一对应电连接的金属结构,包括:

5.根据权利要求1所述的制造方法,其特征在于,所述第二芯片背向所述第一芯片的表面与所述封装层背向所述第一芯片的表面平齐,所述第二重布线层覆盖所述第二芯片背向所述第一芯片的表面与所述封装层背向所述第一芯片的表面。

6.根据权利要求1所述的制造方法,其特征在于,在所述第一重布线层之上形成封装层之前,所述制造方法还包括:

7.根据权利要求1-6中任一项所述的制造方法,其特征在于,所述第一芯片为众核芯片,所述众核芯片包括多个处理核,所述处理核包括计算单元;

8.根据权利要求6所述的制造方法,其特征在于,所述第三芯片为外部存储芯片、电源芯片或者传感器芯片。

9.一种晶圆级封装方法,其特征在于,所述晶圆级封装方法包括:提供晶圆,所述晶圆包含所述多个第一芯片;

10.一种多芯片封装结构,其特征在于,所述多芯片封装结构包括:

11.一种多芯片封装结构,其特征在于,所述多芯片封装结构包括:

技术总结

本公开提供了一种多芯片封装结构及其制造方法、晶圆级封装方法,该制造方法包括:在第一芯片的有源表面形成第一重布线层,并在第一重布线层背向第一芯片的表面形成第一导电凸块;将第二芯片设置于第一重布线层背向第一芯片的表面的中间区域,并使第二芯片的引脚与中间区域中的第一导电凸块一一对准连接;在第一重布线层之上形成封装层,并在封装层中形成与外围区域中的第一导电凸块一一对应电连接的金属结构;在封装层之上形成第二重布线层,第二重布线层用于将金属结构按照预设方式重新布置,以在第二重布线层背向第一芯片的表面形成与金属结构一一对应电连接的连接垫;在连接垫背向第一芯片的表面形成植球,得到多芯片封装结构。

技术研发人员:何伟,祝夭龙

受保护的技术使用者:无锡灵汐类脑科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!