半导体器件的制作方法

本申请属于半导体,特别是涉及半导体器件。

背景技术:

1、半导体器件在光电领域具有广泛的应用,对于硅基的光电半导体器件而言,硅的表面反射率很高,如果对硅表面不进行任何处理,那么它对可见光和近红外光的反射率较高。晶体硅对光的高反射率,使得采用晶体硅制备的相关光电半导体器件的量子效率非常不理性,最终严重制约其光电产品的应用领域和使用性能。

2、人们常常在硅表面制备各种“绒面”结构,如金字塔阵列,这些结构可增加光在硅表面的反射次数,从而来增强硅表面对入射光能的俘获能力,即减少光能反射损失,提高半导体器件对光的吸收和转化效率。

3、目前制备的硅半导体器件仍然存在暗电流较大,量子效率有待提高的问题。

技术实现思路

1、有鉴于此,本申请主要解决的技术问题是提供一种半导体器件,能够降低半导体器件的暗电流,提高量子效率。

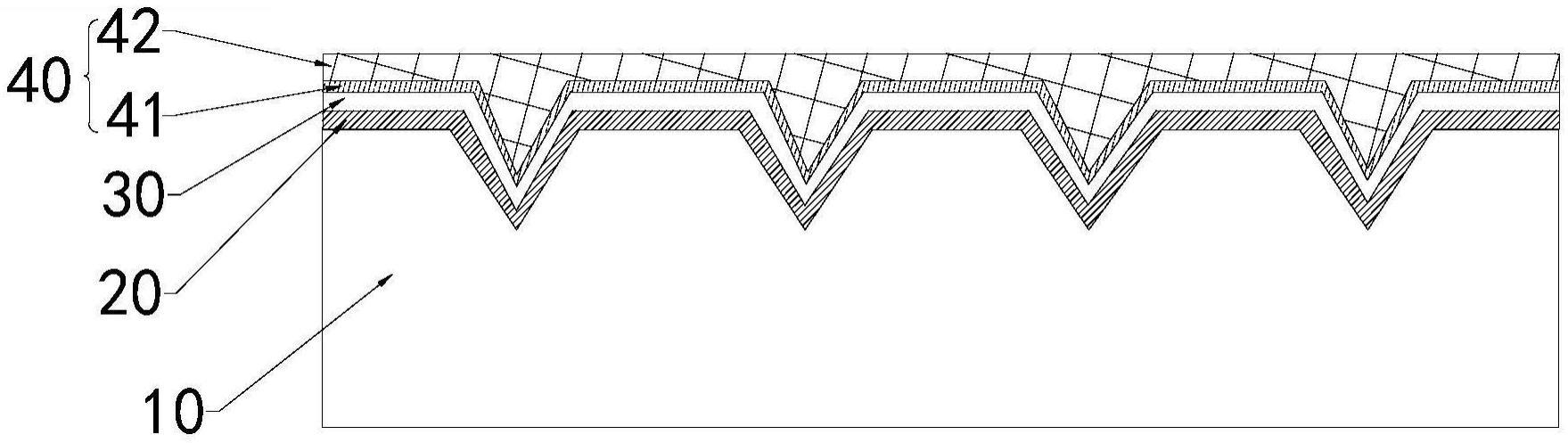

2、为解决上述技术问题,本申请采用的一个技术方案是:一种半导体器件,包括基底层、缓冲层和修复层,基底层包括相对设置的第一表面和第二表面,第一表面设置多个第一凹槽;缓冲层设置于第一表面上,且覆盖第一凹槽,并形成第二凹槽;修复层设置于缓冲层背离基底层的一侧,且至少部分修复层填充于第二凹槽中,修复层用于修复第一凹槽所在位置处基底层表面的缺陷。

3、其中,修复层填充于第二凹槽中,形成第三凹槽;半导体器件还包括抗反射层,抗反射层设置于修复层背离基底层一侧至少部分抗反射层填充于第三凹槽中。

4、其中,抗反射层背离基底层一侧的表面为平面。

5、其中,抗反射层包括第一抗反射层和第二抗反射层,第一抗反射层设置于修复层背离基底层一侧,且至少部分第一抗反射层填充于第三凹槽中,并形成第四凹槽;第二抗反射层位于第一抗反射层背离基底层一侧,且至少部分第二抗反射层填充于第四凹槽中。

6、其中,第一凹槽在沿第一表面指向第二表面的方向上横截面积逐渐减小。

7、其中,第一凹槽的侧面与第一凹槽的开口所在面之间的夹角为54.7度±测量误差。

8、其中,第一凹槽的形状包括倒四棱锥型或倒四棱台型或三角形。

9、其中,第一凹槽的侧面为{111}晶面族。

10、其中,缓冲层的材质为氧化层,氧化层的材质为氧化硅;修复层的材质为氧化铝或氧化铪。

11、其中,第一抗反射层的材质包括氧化钽,第二抗反射层的材质为透光介质层。

12、本申请的有益效果是:区别于现有技术,本申请实施例中,基底层的第一表面上设置多个第一凹槽,多个第一凹槽阵列排布,根据斯涅耳定律,垂直于基底层的入射光线照射至第一凹槽侧面上,在第一凹槽侧面上发生全反射,经折射进入基底层,增加了光在基底层内部的反射次数,扩展了进入基底层内的光路长度,有效光程长度随着在基底层中延长,增加了光的吸收效率,从而来增强基底层表面对入射光能的俘获能力,减少光能反射损失,提高半导体器件对光的吸收和转化效率。本发明实施例中,通过设置一层缓冲层于基底层上,缓冲层覆盖基底层的表面及基底层的第一凹槽表面,可以改善基底层的应力。本发明实施例中,通过设置一层修复层,修复层位于缓冲层背离基底层一侧,修复层覆盖缓冲层,本发明的修复层可以修复基底层的第一凹槽侧面所形成的缺陷,修复基底层的第一凹槽侧面损伤,中和基底层中的电荷,减小基底层的暗电流,提高量子效率。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述至少部分所述修复层(30)填充于所述第二凹槽(21)中,形成第三凹槽(31),

3.根据权利要求2所述的半导体器件,其特征在于,所述抗反射层(40)背离所述基底层(10)一侧的表面为平面。

4.根据权利要求2所述的半导体器件,其特征在于,所述抗反射层(40)包括:

5.根据权利要求1所述的半导体器件,其特征在于,所述第一凹槽(13)在沿所述第一表面(11)指向所述第二表面(12)的方向上横截面积逐渐减小。

6.根据权利要求5所述的半导体器件,其特征在于,所述第一凹槽(13)的侧面与所述第一凹槽(13)的开口所在面之间的夹角为54.7度±测量误差。

7.根据权利要求5所述的半导体器件,其特征在于,所述第一凹槽(13)的形状包括倒四棱锥型或倒四棱台型或三角形。

8.根据权利要求4所述的半导体器件,其特征在于,所述第一凹槽的侧面为{111}晶面族。

9.根据权利要求1所述的半导体器件,其特征在于,所述缓冲层(20)的材质为氧化层,所述氧化层的材质为氧化硅;所述修复层(30)的材质为氧化铝或氧化铪。

10.根据权利要求4所述的半导体器件,其特征在于,所述第二抗反射层(42)的材质为透光介质层。

技术总结

本申请属于半导体技术领域,特别是涉及一种半导体器件,包括基底层、缓冲层和修复层,基底层包括相对设置的第一表面和第二表面,第一表面设置多个第一凹槽;缓冲层设置于第一表面上,且覆盖第一凹槽,并形成第二凹槽;修复层设置于缓冲层背离基底层一侧,且至少部分所述修复层填充于所述第二凹槽中,所述修复层用于修复所述第一凹槽所在位置处所述基底层表面的缺陷。本申请的半导体器件可以减小基底层的暗电流,提高量子效率。

技术研发人员:古立亮

受保护的技术使用者:武汉新芯集成电路制造有限公司

技术研发日:20220722

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!