用于不对称瞬态电压抑制器的封装结构的制作方法

本公开总体上涉及功率半导体分立器件的领域,并且特别地,涉及表面安装封装,包括不对称瞬态电压抑制器器件的封装结构。

背景技术:

1、封装集成电路通常是半导体器件制造工艺的最后阶段。在封装过程中,代表半导体器件核心的半导体管芯被包裹在保护管芯免受物理损坏和腐蚀的外壳中。例如,半导体管芯通常使用焊料合金回流焊、导电环氧树脂等被安装在铜衬底上。安装的半导体管芯然后通常被封装在塑料或环氧化合物中。

2、瞬态电压抑制器(tvs)器件代表功率半导体器件的一个重要分支,其可被用于保护敏感电子设备免受电压瞬态的影响,例如,闪电和/或其他瞬态电压事件。目前,tvs器件封装的典型特征是小尺寸和高功率。tvs器件封装的示例包括表面安装c型(smc)封装,其被用于许多不同的技术领域,例如多点式数据传输系统。通常,多点式数据传输系统要求使用不对称tvs器件,其中smc封装为印刷电路板中的电子部件提供保护以免受静电放电(esd)、电快速瞬变(eft)、闪电等的影响。然而,tvs器件的当前smc封装在解决不同的散热要求、不同的制造工艺特征等以及其他电子部件和/或系统要求方面存在不足。

技术实现思路

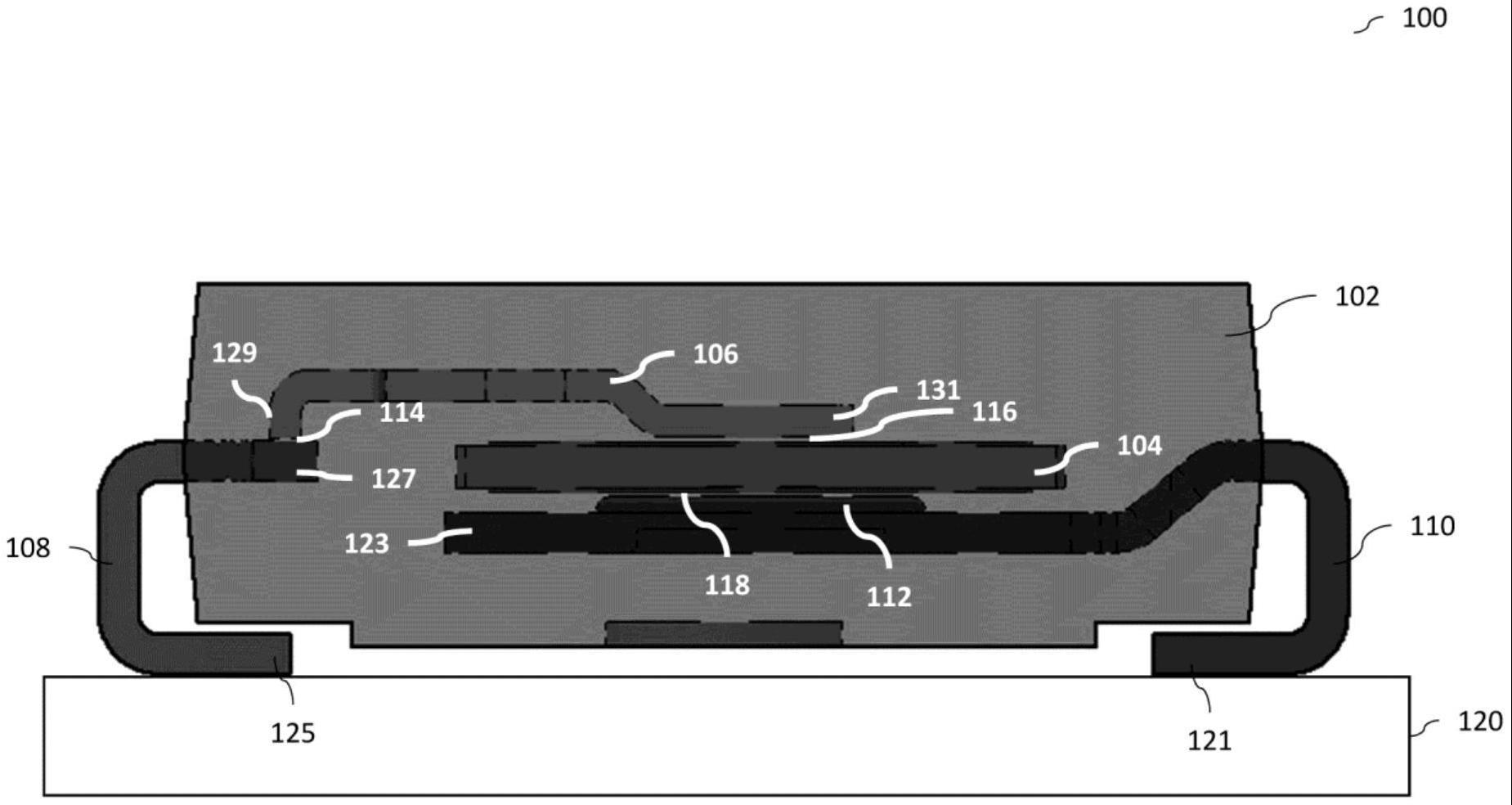

1、在一些实施方式中,当前主题涉及表面安装结构和/或装置。该结构可以包括:外壳;至少部分地被外壳封装的引线框架,其中引线框架可以包括具有芯片安装垫的芯片安装表面;以及设置在芯片安装表面外部的一个或多个第一应力消除特征件。该结构还可以包括至少部分地被外壳封装的另一引线框架,其中另一引线框架可以包括一个或多个第二应力消除特征件。

2、在一些实施方式中,当前主题可以包括以下可选特征中的一个或多个。在一些实施方式中,半导体芯片可以被配置为耦接到芯片安装垫。在将半导体芯片耦接到芯片安装垫时,芯片安装表面不接触半导体芯片。

3、在一些实施方式中,当前主题的结构还可以包括由外壳完全封装的夹片,其中,另一引线框架可以被配置为耦接到夹片。半导体芯片可以包括半导体芯片工作区。夹片可以被配置为被耦接到半导体芯片工作区。此外,夹片可以被配置为包括远离夹片的一个或多个边缘横向延伸的一个或多个支撑杆。

4、在一些实施方式中,一个或多个第二应力消除特征件可以包括远离另一引线框架横向延伸的一个或多个应力消除杆。

5、在一些实施方式中,夹片可以被配置为具有弯曲结构,其中,夹片的弯曲结构的至少一部分可以被配置为远离半导体芯片延伸。

6、在一些实施方式中,引线框架可以包括倾斜部分,该倾斜部分被配置为远离芯片安装表面有角度地延伸。第一应力消除特征件可以被配置为形成在倾斜部分中。第一应力消除特征件可以包括以下至少一个:应力消除开口、一个或多个应力消除凹槽、以及它们的任意组合。一个或多个应力消除凹槽可以被配置为围绕引线框架的倾斜部分中的应力消除开口对称地形成。

7、在一些实施方式中,引线框架可以包括引线框架终端,并且另一引线框架可以包括另一个引线框架终端。引线框架终端和另一引线框架终端可以被配置为耦接到以下至少之一:衬底、印刷电路板及其任意组合。

8、在一些实施方式中,外壳可以由以下至少一种制成:环氧化合物、塑料及其任意组合。

9、在一些实施方式中,装置可以被配置为表面安装装置。该装置可以被配置为包括瞬态电压抑制器件。

10、在一些实施方式中,当前主题涉及用于制造上述装置的方法或装置。该方法可以包括:提供半导体芯片;在引线框架中形成一个或多个第一应力消除特征件,引线框架被配置为包括设置在引线框架的芯片安装表面上的芯片安装垫,一个或多个第一应力消除特征件被配置为形成在芯片安装表面的外部;使用芯片安装垫将引线框架耦接到所述半导体芯片;在另一个引线框架中形成一个或多个第二应力消除特征件;以及形成外壳以封装引线框架、另一引线框架和半导体芯片,其中,引线框架和另一引线框架中的每一个的至少一部分被配置为延伸到外壳的外部。

11、在一些实施方式中,第一应力消除特征件可以包括以下至少一个:一个或多个应力消除开口、一个或多个应力消除凹槽以及它们的任意组合。第二应力消除特征件可以包括一个或多个应力消除杆。

12、本文所述主题的一个或多个变体的细节在以下附图和描述中阐述。本文所述主题的其他特征和优点将从描述和附图以及权利要求书中显而易见。

技术特征:

1.一种用于不对称瞬态电压抑制器的封装结构,其特征在于,包括:

2.根据权利要求1所述的封装结构,其特征在于,半导体芯片被配置为被耦接到所述芯片安装垫。

3.根据权利要求2所述的封装结构,其特征在于,在将所述半导体芯片耦接到所述芯片安装垫时,所述芯片安装表面不接触所述半导体芯片。

4.根据权利要求2所述的封装结构,其特征在于,还包括被所述外壳完全封装的夹片,其中,所述另一个引线框架被配置为被耦接到所述夹片。

5.根据权利要求4所述的封装结构,其特征在于,所述半导体芯片包括半导体芯片工作区。

6.根据权利要求5所述的封装结构,其特征在于,所述夹片被配置为被耦接到所述半导体芯片工作区。

7.根据权利要求4所述的封装结构,其特征在于,所述夹片被配置为包括远离所述夹片的一个或多个边缘横向延伸的一个或多个支撑杆。

8.根据权利要求4所述的封装结构,其特征在于,所述一个或多个第二应力消除特征件包括远离所述另一个引线框架横向延伸的一个或更多个应力消除杆。

9.根据权利要求8所述的封装结构,其特征在于,所述夹片被配置为具有弯曲结构,其中,所述夹片的弯曲结构的至少一部分被配置为远离所述半导体芯片延伸。

10.根据权利要求1所述的封装结构,其特征在于,所述引线框架包括倾斜部分,所述倾斜部分被配置为远离所述芯片安装表面有角度地延伸。

11.根据权利要求10所述的封装结构,其特征在于,所述一个或多个第一应力消除特征件被配置为形成在所述倾斜部分中。

12.根据权利要求11所述的封装结构,其特征在于,所述一个或多个第一应力消除特征件包括以下至少一个:应力消除开口、一个或多个应力消除凹槽、以及它们的任意组合。

13.根据权利要求12所述的封装结构,其特征在于,所述一个或多个应力消除凹槽被配置为围绕所述引线框架的所述倾斜部分中的应力消除开口对称地形成。

14.根据权利要求1所述的封装结构,其特征在于,所述引线框架包括引线框架终端,并且所述另一个引线框架包括另一个引线框架终端。

15.根据权利要求14所述的封装结构,其特征在于,所述引线框架终端和所述另一个引线框架终端被配置为耦接到以下至少一个:衬底、印刷电路板以及它们的任意组合。

16.根据权利要求1所述的封装结构,其特征在于,所述封装结构被配置为表面安装封装结构。

17.根据权利要求1所述的封装结构,其特征在于,还包括瞬态电压抑制器件。

18.一种用于不对称瞬态电压抑制器的封装结构,其特征在于,包括:

技术总结

本技术公开了一种用于不对称瞬态电压抑制器的封装结构。包括外壳、至少部分地被外壳封装的引线框架。引线框架包括具有芯片安装垫的芯片安装表面和设置在芯片安装表面外部的一个或多个第一应力消除特征件。该装置还包括至少部分地被外壳封装的另一个引线框架。另一引线框架包括一个或多个第二应力消除特征件。

技术研发人员:张锋,高超,何磊

受保护的技术使用者:力特半导体(无锡)有限公司

技术研发日:20220916

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!