一种模压电感的制作方法

本技术涉及电感的,特别涉及一种模压电感。

背景技术:

1、现有的模压电感是将线圈绕组置于磁粉内部,一体模压成型,由于线圈绕组埋于磁粉中部,通电时线圈产生的磁场在模压电感的内部就可以形成闭合回路,相对于传统电感,模压电感的漏磁相对较少,但由于磁粉一般采用合金磁粉或羰基磁粉,而合金磁粉或羰基磁粉的相对磁导率处于25-35的范围内,相对磁导率较低,仍然有少部分磁通从模压电感的内部漏出,而模压电感通常放置在电路板上,在元件密集的电路板上,这微量漏磁通仍然会对周边元件造成电磁干扰,影响周边元件的性能。

技术实现思路

1、基于此,有必要提供一种降低漏磁通的模压电感。

2、一种模压电感,包括:

3、壳体,所述壳体为磁性材料制成;

4、线圈组件,设置于所述壳体内部,所述线圈组件包括线圈绕组和金属磁粉,所述金属磁粉包裹于所述线圈绕组外;以及

5、磁片,设置于所述壳体的外表面,所述磁片的相对磁导率大于所述金属磁粉的相对磁导率。

6、可选的,所述磁片的材质为锰锌铁氧体。

7、可选的,所述磁片的相对磁导率大于2000。

8、可选的,所述磁片设置于所述壳体的顶部和/或外侧壁上。

9、可选的,所述壳体为矩形体结构,所述壳体的顶部和所述壳体的四个外侧壁均设置有所述磁片。

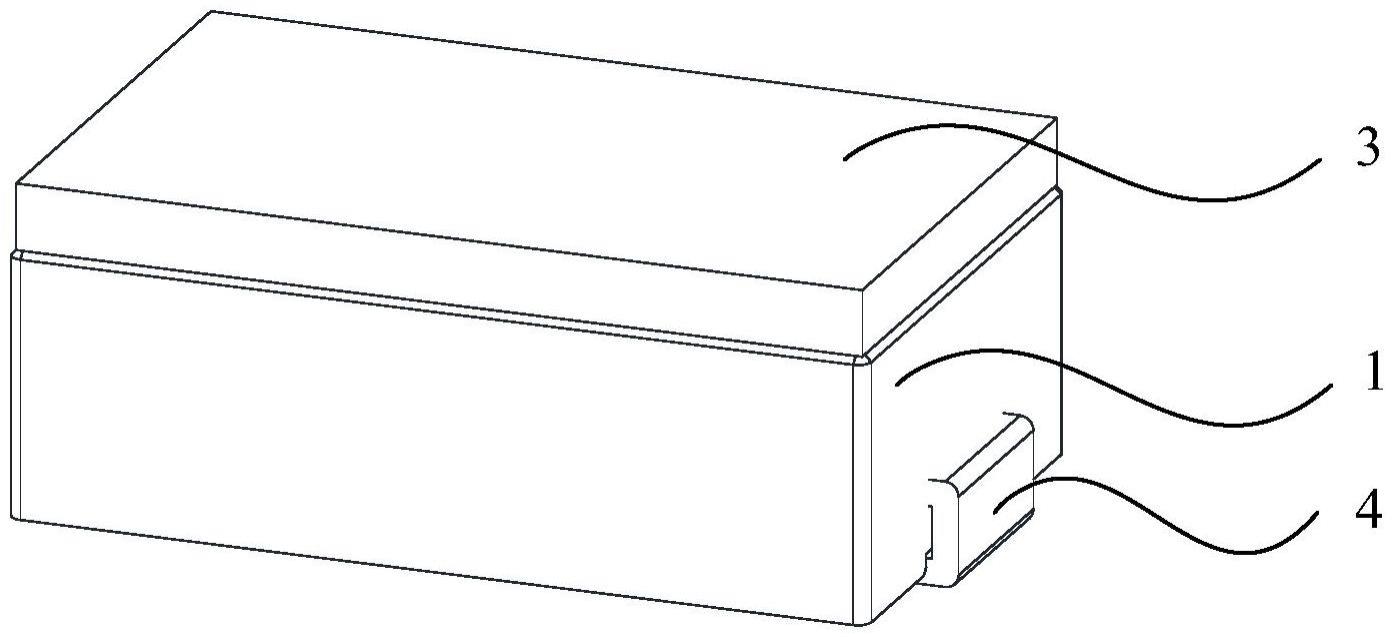

10、可选的,所述模压电感还包括连接端子,连接端子设置于所述壳体的外侧壁上,且与所述线圈组件连接。

11、可选的,所述连接端子包括第一端子和第二端子,所述第一端子和所述第二端子相对设置于所述壳体的两外侧壁上,所述第一端子与所述线圈绕组的一端连接,所述第二端子与所述线圈绕组的另一端连接。

12、可选的,所述第一端子包括第一铜片、第一镍层和第一锡层,所述第一铜片和所述第一镍层包裹于所述第一锡层内,所述第一铜片包裹于所述第一镍层内。

13、可选的,所述第二端子包括第二铜片、第二镍层和第二锡层,所述第二铜片和所述第二镍层包裹于所述第二锡层内,所述第二铜片包裹于所述第二镍层内。

14、可选的,所述壳体包括盖体和底座,所述盖体设置于所述底座的上方,所述线圈组件设置于所述底座内,所述第一端子和所述第二端子设置于所述底座的相对两外侧壁上。

15、本申请通过在壳体的外表面上设置有相对磁导率大于金属磁粉的相对磁导率的磁片,可以使得从线圈组件流出至壳体外部的磁通,被磁片吸收并聚集在磁片的内部流通,从而减小或消除模压电感的漏磁通,从而避免模压电感的漏磁通对电路板上的周边元件造成电磁干扰,避免影响周边元件的性能。

技术特征:

1.一种模压电感,设置于电路板上,其特征在于,包括:

2.根据权利要求1所述的模压电感,其特征在于,所述磁片的材质为锰锌铁氧体。

3.根据权利要求2所述的模压电感,其特征在于,所述磁片的相对磁导率大于2000。

4.根据权利要求1所述的模压电感,其特征在于,所述磁片设置于所述壳体的顶部和/或外侧壁上。

5.根据权利要求4所述的模压电感,其特征在于,所述壳体为矩形体结构,所述壳体的顶部和所述壳体的四个外侧壁均设置有所述磁片。

6.根据权利要求1所述的模压电感,其特征在于,所述模压电感还包括连接端子,连接端子设置于所述壳体的外侧壁上,且与所述线圈组件连接。

7.根据权利要求6所述的模压电感,其特征在于,所述连接端子包括第一端子和第二端子,所述第一端子和所述第二端子相对设置于所述壳体的两外侧壁上,所述第一端子与所述线圈绕组的一端连接,所述第二端子与所述线圈绕组的另一端连接。

8.根据权利要求7所述的模压电感,其特征在于,所述第一端子包括第一铜片、第一镍层和第一锡层,所述第一铜片和所述第一镍层包裹于所述第一锡层内,所述第一铜片包裹于所述第一镍层内。

9.根据权利要求7所述的模压电感,其特征在于,所述第二端子包括第二铜片、第二镍层和第二锡层,所述第二铜片和所述第二镍层包裹于所述第二锡层内,所述第二铜片包裹于所述第二镍层内。

10.根据权利要求7所述的模压电感,其特征在于,所述壳体包括盖体和底座,所述盖体设置于所述底座的上方,所述线圈组件设置于所述底座内,所述第一端子和所述第二端子设置于所述底座的相对两外侧壁上。

技术总结

本技术公开一种模压电感,包括:壳体、线圈组件和磁片;所述壳体为磁性材料制成,线圈组件设置于所述壳体内部,所述线圈组件包括线圈绕组和金属磁粉,所述金属磁粉包裹于所述线圈绕组外;磁片设置于所述壳体的外表面,所述磁片的相对磁导率大于所述金属磁粉的相对磁导率。本申请的磁片能够使得从线圈组件流出至壳体外部的磁通,被磁片吸收并聚集在磁片的内部流通,从而减小或消除模压电感的漏磁通,从而避免模压电感的漏磁通对电路板上的周边元件造成电磁干扰,避免影响周边元件的性能。

技术研发人员:周玮

受保护的技术使用者:联振电子(深圳)有限公司

技术研发日:20221026

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!