一种VDMOS器件的制作方法

本技术涉及半导体器件领域,尤其涉及一种vdmos器件。

背景技术:

1、屏蔽栅场效应晶体管是在传统的沟槽vdmos的基础上发展而来的,具有上下两层多晶结构,上层多晶是门极控制栅结构,与传统沟槽结构类似,下层多晶通过走线与源极相联,起到屏蔽门极作用。它和传统的沟槽vdmos相比,在同等耐压下拥有更小的导通电阻,以及更低的米勒电容,具有更快的开关速度。由于实际应用环境的复杂,对功率vdmos的可靠性要求比较高,功率器件产品在其生产、制造、装配以及工作过程中极易受到esd的影响,造成产品内部损伤、可靠性降低,功率vdmos的esd薄弱点是栅源端的薄层栅氧化层击穿,屏蔽栅vdmos因具有双栅结构,其失效点还有上下两层多晶结构间的氧化层击穿。两层多晶结构的隔离主要两种形成方法,一种是通过淀积二氧化硅形成隔离,另外一种是通过多晶硅热氧化形成介质隔离。第一种通过淀积形成的二氧化硅,在刻蚀时不容易控制厚度,并且刻蚀容易造成氧化层损伤,降低栅源两端的击穿电压;第二种多晶硅热氧化形成的氧化层,氧化层的质量较差,抗esd能力也较差。

技术实现思路

1、本实用新型实施例提供一种vdmos器件,用以至少解决现有技术中vdmos器件抗esd能力也较差的问题。

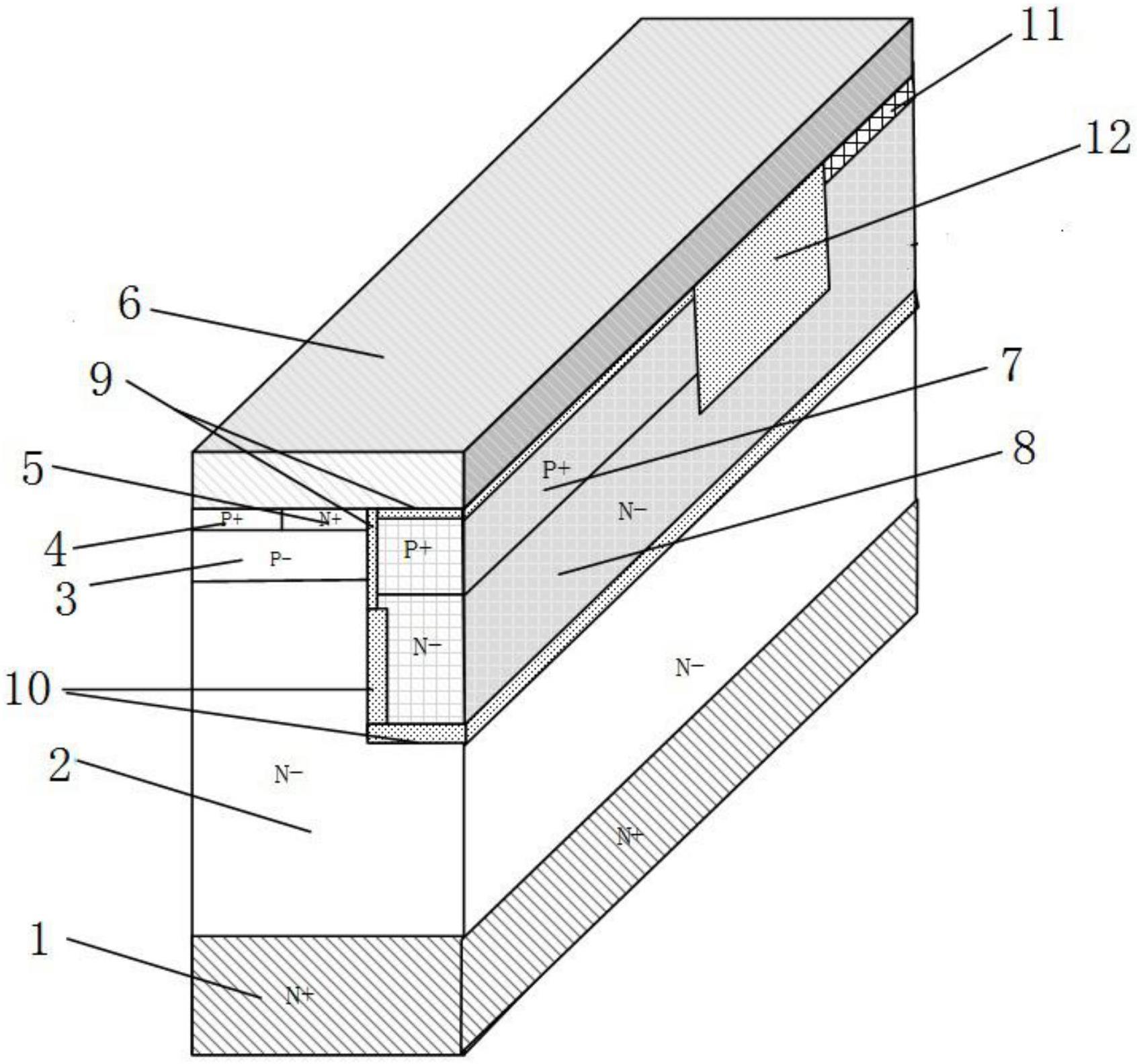

2、根据本实用新型提出的一种vdmos器件,包括:

3、衬底层,为n型重掺杂层;

4、外延层,生长于所述衬底层的一侧,所述外延层为n型轻掺杂层;

5、p-body层,设置于所述外延层远离所述衬底层的一侧;

6、欧姆接触层,设置于所述p-body层远离所述外延层的一侧;

7、源极电子层,与所述欧姆接触层并列,设置于所述p-body层远离所述外延层的一侧;

8、第一金属层,覆盖所述欧姆接触层与所述源极电子层,且与所述欧姆接触层、所述源极电子层均电连接;

9、沟道,设置于所述第一金属层与所述外延层之间,所述沟道靠近所述源极电子层远离所述欧姆接触层的一侧;

10、栅极多晶硅层,设置于所述沟道,与所述第一金属层、所述p-body层、所述源极电子层均通过第一隔离层隔离;

11、源极多晶硅层,设置于所述栅极多晶硅层远离所述第一金属层的一侧,与所述外延层通过第二隔离层隔离;

12、所述栅极多晶硅层的头端与所述源极多晶硅层的头端平齐,所述源极多晶硅层的尾端通过第二金属层与所述第一金属层连接,所述第二金属层为肖特基势垒金属;所述栅极多晶硅层的尾端通过第三隔离层与所述源极多晶硅层的尾端隔离,且所述第三隔离层在第一金属层至衬底层方向的深度要大于所述栅极多晶硅层的深度。

13、根据本实用新型的一些实施例,所述第一隔离层的厚度小于所述第二隔离层的厚度。

14、根据本实用新型的一些实施例,所述第一隔离层的厚度为30-150nm。

15、根据本实用新型的一些实施例,所述第二隔离层的厚度为0.1-0.8um。

16、根据本实用新型的一些实施例,所述栅极多晶硅层为p型重掺杂层,所述源极多晶硅层为n型轻掺杂层。

17、根据本实用新型的一些实施例,所述栅极多晶硅层的掺杂杂质为硼或铝。

18、根据本实用新型的一些实施例,所述源极多晶硅层的掺杂杂质为磷或砷,掺杂浓度为1e15-1e17cm-3。

19、根据本实用新型的一些实施例,所述肖特基势垒金属为钛或镍。

20、采用本实用新型实施例的技术方案,将传统的双层多晶结构之间的氧化层转化为新型的pn结隔离,同时源极多晶硅层与第一金属层源极金属的连接采用肖特基势垒金属进行连接,使得栅极与源极之间形成pn结二极管与肖特基二极管,在达到降低米勒电容效果的同时,还能在静电释放时,使得二极管先被击穿,直接从栅源之间的寄生二极管释放能量,从而进一步提高了抗esd能力。

21、上述说明仅是本实用新型技术方案的概述,为了能够更清楚了解本实用新型的技术手段,而可依照说明书的内容予以实施,并且为了让本实用新型的上述和其它目的、特征和优点能够更明显易懂,以下特举本实用新型的具体实施方式。

技术特征:

1.一种vdmos器件,其特征在于,包括:

2.如权利要求1所述的vdmos器件,其特征在于,所述第一隔离层的厚度小于所述第二隔离层的厚度。

3.如权利要求2所述的vdmos器件,其特征在于,所述第一隔离层的厚度为30-150nm。

4.如权利要求2所述的vdmos器件,其特征在于,所述第二隔离层的厚度为0.1-0.8um。

5.如权利要求1所述的vdmos器件,其特征在于,所述栅极多晶硅层为p型重掺杂层,所述源极多晶硅层为n型轻掺杂层。

6.如权利要求5所述的vdmos器件,其特征在于,所述栅极多晶硅层的掺杂杂质为硼或铝。

7.如权利要求5所述的vdmos器件,其特征在于,所述源极多晶硅层的掺杂杂质为磷或砷,掺杂浓度为1e15-1e17cm-3。

8.如权利要求1所述的vdmos器件,其特征在于,所述肖特基势垒金属为钛或镍。

技术总结

本技术公开了VDMOS器件,包括:衬底层;外延层,生长于衬底层的一侧;P‑body层,设置于外延层远离衬底层的一侧;欧姆接触层,设置于P‑body层远离外延层的一侧;源极电子层,与欧姆接触层并列,设置于P‑body层远离外延层的一侧;第一金属层,覆盖欧姆接触层与源极电子层;沟道,设置于第一金属层与外延层之间,沟道靠近源极电子层远离欧姆接触层的一侧;栅极多晶硅层,设置于沟道;源极多晶硅层,设置于沟道内栅极多晶硅层远离第一金属层的一侧;源极多晶硅层的尾端通过第二金属层与第一金属层连接,第二金属层为肖特基势垒金属;栅极多晶硅层的尾端通过第三隔离层与源极多晶硅层的尾端隔离。采用本技术,使用新的隔离结构,提高了抗ESD能力。

技术研发人员:单亚东,谢刚,胡丹

受保护的技术使用者:广微集成技术(深圳)有限公司

技术研发日:20221216

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!