降低信号间串扰的量子计算芯片接地结构的制作方法

本申请属于量子计算芯片封装,涉及一种超导量子芯片封装结构。

背景技术:

1、超导量子计算芯片接地情况影响引线串扰、封装谐振模式,对超导量子处理器整体性能有重要影响。在现有技术中,对于采用蓝宝石衬底的超导量子计算芯片,芯片线路位于芯片的上表面,其接地主要有两种方案,如图1和图2所示。

2、在图1和图2中,印制电路板下表面一般与封装结构金属基座直接接触实现接地,印制电路板上表面通过印制电路板中的通孔或侧边金属化层与下表面相连,进而与金属基座连通实现接地。在图1的方案中,在芯片与印制电路板之间键合引线,如铝丝,实现芯片与印制电路板间的信号连接,并通过印制电路板间接接地。在图2方案中,印制电路板中间的开口比芯片略小,在封装时印制电路板直接压在芯片上,实现了芯片表面的地焊盘与印制电路板背面相连,进而实现了与金属基座连通,进行了间接接地。

3、在图1方案中,芯片通过与印制电路板上层相连,然后通过印制电路板中通孔或侧边金属化层与下面的封装结构金属基座连通,实现间接接地。该方案从芯片到金属基座,接地路径较长,会引入通孔寄生电感。另外,印制电路板与金属基座间并不是良好接触,会存在一些缝隙或空洞,因此还会引入寄生电容。接地路径上的寄生电感和寄生电容会带来两方面性能的恶化。一是传输性能下降,这主要是回波损耗变差、插入损耗增加和串扰增加;二是封装盒体内的谐振频率下降,谐振频率下降可使得谐振频率落入量子比特的工作频带内,进而引起量子比特性能下降,如退相干时间缩短、串扰增加等。

4、在图2方案中,印制电路板直接压在芯片上,实现芯片表面接地。该方案有四方面的缺点。一是印制电路板的平整性对芯片接地情况有很大影响,若印制电路板存在部分区域翘曲,则对应的芯片上的区域无法实现良好接触。二是为了实现印制电路板与芯片间的良好接触,印制电路板与金属基座之间一般留有缝隙,以便印制电路板与芯片优先接触,这样会影响印制电路板接地。三是印制电路板与芯片之间存在较大高度差,若印制电路板较厚,则信号引线较长,会降低微波传输性能。四是印制电路板对芯片的压力不可过大,否则芯片存在一定碎裂风险。

5、并且上述图1和图2的方案中,信号引线也都是暴露在外部,相邻信号引线间增加了串扰的风险。

6、公布号为cn110446369 a的发明专利申请公开了一种键合结构,键合结构包括:量子芯片;pcb板,用于与该量子芯片进行键合,该pcb板上设置有开孔,该开孔的尺寸大于所述量子芯片的尺寸以容纳所述量子芯片;其中,所述量子芯片位于所述pcb板的开孔内且与所述pcb板电性连接。通过设置开孔,将量子芯片放置于开孔中,且开孔的尺寸略大于量子芯片的尺寸,从而缩短了引线长度,减小了微波信号在键合处产生的阻抗不匹配,提高了信号质量。该专利申请中采用是上述图1方案的接地方式,同样存在上述图1方案的缺陷。

技术实现思路

1、本实用新型所要解决的技术问题在于如何实现超导量子计算芯片的良好接地并且降低相邻信号引线间的串扰。

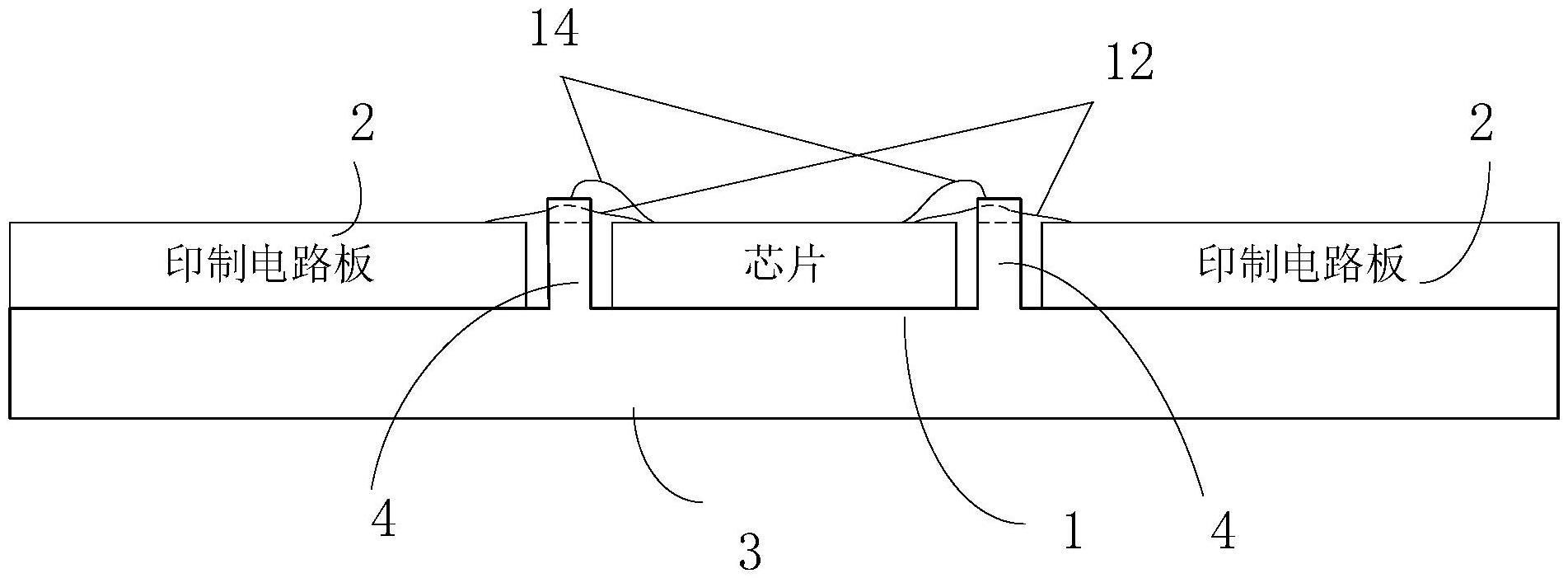

2、本实用新型通过以下技术手段实现解决上述技术问题的:一种降低信号间串扰的量子计算芯片接地结构,包括芯片(1)、印制电路板(2)、金属基座(3),所述芯片(1)、印制电路板(2)封装在金属基座(3)的上表面,所述印制电路板(2)上开设有孔,所述芯片(1)容纳在孔中,该降低信号间串扰的量子计算芯片接地结构还包括金属棱(4),所述金属棱(4)设置在芯片(1)与印制电路板(2)之间,芯片(1)与印制电路板(2)通过第一键合引线(12)实现信号连接,所述芯片(1)与金属棱(4)之间通过第二键合引线(14)实现接地连接,所述金属棱(4)上开窄槽,所述第一键合引线(12)穿过金属棱(4)的窄槽。

3、作为进一步优化的技术方案,所述金属棱(4)与芯片(1)和印制电路板(2)均不接触。

4、作为进一步优化的技术方案,所述金属棱(4)呈环形分布在芯片(1)与印制电路板(2)之间。

5、作为进一步优化的技术方案,所述金属棱(4)与金属基座(3)加工成一体。

6、作为进一步优化的技术方案,所述金属棱(4)高于芯片(1)和印制电路板(2)。

7、作为进一步优化的技术方案,所述金属基座(3)为铜基座,表面镀金或银,或者所述金属基座(3)为铝基座。

8、作为进一步优化的技术方案,所述窄槽顶端开口,所述窄槽的底部与芯片(1)和印制电路板(2)的顶端平齐或低或高于芯片(1)和印制电路板(2)的顶端。

9、作为进一步优化的技术方案,所述金属棱(4)宽度为0.2毫米~0.5毫米,所述窄槽宽度为0.2毫米~0.5毫米,金属棱(4)高于芯片(1)和印制电路板(2)的上表面0.2毫米~0.4毫米。

10、作为进一步优化的技术方案,所述金属基座(3)分成基座本体(32)和金属板(34),基座本体(32)外围是金属板(34),所述芯片(1)位于基座本体(32)上,印制电路板(2)位于金属板(34)上,金属棱(4)加工在基座本体(32)上。

11、作为进一步优化的技术方案,所述基座本体(32)与金属板(34)厚度一致,高度一致,所述基座本体(32)与金属板(34)之间相互固定。

12、本实用新型的优点在于:

13、1、本申请在封装结构中的金属基座上增加金属棱,使量子芯片可通过键合引线接到金属棱,从而直接接地,接地路径较短,解决现有技术方案中芯片通过印制电路板间接接地引入的寄生电感,另外,因为量子芯片通过键合引线接地,印制电路板与金属基座间存在的缝隙或空洞对结构整体性能没有影响,避免引入寄生电容,从而可降低信号线间的串扰,提高了封装盒体的谐振频率。

14、2、本申请中的印制电路板没有直接压在芯片上,降低了对印制电路板的平整性的要求;在本申请中,无需在印制电路板与金属基座之间留有缝隙,使得印制电路板可与封装结构中的金属基座和金属板紧密接触,改善了印制电路板的接地状况;本申请的方案中,印制电路板与芯片之间不存在高度差,不会使得信号引线较长,避免了微波传输性能降低;由于在本申请所提出的技术方案中,芯片没有受到印制电路板的压力,因此避免了芯片被压碎的风险。

15、3、本申请中在金属棱上开窄槽,在键合信号引线时,使信号引线穿过金属棱的窄槽内,这样可在一定程度上降低相邻信号引线间的串扰,提高隔离度。

技术特征:

1.一种降低信号间串扰的量子计算芯片接地结构,包括芯片(1)、印制电路板(2)、金属基座(3),所述芯片(1)、印制电路板(2)封装在金属基座(3)的上表面,所述印制电路板(2)上开设有孔,所述芯片(1)容纳在孔中,其特征在于:还包括金属棱(4),所述金属棱(4)设置在芯片(1)与印制电路板(2)之间,芯片(1)与印制电路板(2)通过第一键合引线(12)实现信号连接,所述芯片(1)与金属棱(4)之间通过第二键合引线(14)实现接地连接,所述金属棱(4)上开窄槽,所述第一键合引线(12)穿过金属棱(4)的窄槽。

2.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属棱(4)与芯片(1)和印制电路板(2)均不接触。

3.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属棱(4)呈环形分布在芯片(1)与印制电路板(2)之间。

4.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属棱(4)与金属基座(3)加工成一体。

5.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属棱(4)高于芯片(1)和印制电路板(2)。

6.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属基座(3)为铜基座,表面镀金或银,或者所述金属基座(3)为铝基座。

7.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述窄槽顶端开口,所述窄槽的底部与芯片(1)和印制电路板(2)的顶端平齐或低或高于芯片(1)和印制电路板(2)的顶端。

8.如权利要求1所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属棱(4)宽度为0.2毫米~0.5毫米,所述窄槽宽度为0.2毫米~0.5毫米,金属棱(4)高于芯片(1)和印制电路板(2)的上表面0.2毫米~0.4毫米。

9.如权利要求1至8任一项所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述金属基座(3)分成基座本体(32)和金属板(34),基座本体(32)外围是金属板(34),所述芯片(1)位于基座本体(32)上,印制电路板(2)位于金属板(34)上,金属棱(4)加工在基座本体(32)上。

10.如权利要求9所述的降低信号间串扰的量子计算芯片接地结构,其特征在于:所述基座本体(32)与金属板(34)厚度一致,高度一致,所述基座本体(32)与金属板(34)之间相互固定。

技术总结

本技术提供一种降低信号间串扰的量子计算芯片接地结构,包括芯片(1)、印制电路板(2)、金属基座(3)和金属棱(4),芯片(1)、印制电路板(2)封装在金属基座(3)的上表面,金属棱(4)设置在芯片(1)与印制电路板(2)之间,芯片(1)与印制电路板(2)通过第一键合引线(12)实现信号连接,芯片(1)与金属棱(4)之间通过第二键合引线(14)实现接地连接,金属棱(4)上开窄槽,第一键合引线(12)穿过金属棱(4)的窄槽。本技术使量子芯片通过键合引线接到金属棱,从而直接接地,接地路径较短,在金属棱上开窄槽,使信号引线穿过金属棱的窄槽,在一定程度上降低相邻信号引线间的串扰,提高隔离度。

技术研发人员:杨威风,沈慧妍,薛春,李东东

受保护的技术使用者:科大国盾量子技术股份有限公司

技术研发日:20221230

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!