半导体装置及其制造方法与流程

本发明涉及一种内置有功率半导体芯片的半导体装置(半导体模块)及其制造方法。

背景技术:

1、主要用于工业的igbt模块(半导体模块)是通过焊料将功率半导体芯片、绝缘电路基板以及散热构件相互接合,最终隔着导热膏(thermal compound)安装于冷却翅片来使用的。另外,在车载领域,还使用了不用导热膏而将绝缘电路基板与冷却翅片进行焊料接合的构造,来作为直接水冷冷却构造。

2、当前,在功率半导体芯片与绝缘电路基板的接合中主要实施焊接,但近年来,以高耐热性、高散热性、高可靠性等为目的,正在推进研究使用了银(ag)等金属的纳米颗粒或微粒的烧结接合技术。在烧结接合技术中,基于能够在低温下接合并且在接合后成为与构成纳米颗粒或微粒的金属相同的熔点这样的特征,不提高接合温度就能够得到耐热性高且高可靠性的接合层。

3、专利文献1和2公开了以下内容:使用掩模来涂布糊状的烧结材料(烧结糊剂),在烧结糊剂上搭载半导体芯片之后进行加热和加压。专利文献3公开了以下内容:以在烧结糊剂上搭载有半导体芯片的状态,在烧结糊剂的烧结前进行加热和加压。专利文献4公开了以下内容:在涂布了烧结糊剂之后取下掩模时会形成糊剂突起。专利文献5公开了一种在俯视时接合材料的外周缘比半导体元件的外周缘大的半导体装置。

4、现有技术文献

5、专利文献

6、专利文献1:美国专利第8253233号说明书

7、专利文献2:美国专利第8415207号说明书

8、专利文献3:美国专利第8835299号说明书

9、专利文献4:日本特开2019-216183号公报

10、专利文献5:日本特开2018-148168号公报

技术实现思路

1、发明要解决的问题

2、在烧结接合技术中主要使用烧结糊剂,但与焊接材料不同,由于不会熔融,因此烧结糊剂在印刷时的表面形状很重要。但是,在印刷烧结糊剂时,有时在烧结糊剂的表面的端部附近会形成突起部。当在烧结材料的表面形成突起部时,在将功率半导体芯片搭载在烧结糊剂上并进行接合时,会被不均匀地加压,有可能导致功率半导体芯片的损坏。另外,为了避开烧结糊剂的表面的突起部地搭载功率半导体芯片,需要采取烧结糊剂的多余的印刷区域,从而安装密度的提高受到限制。

3、鉴于上述问题,本发明的目的在于提供一种能够在搭载功率半导体芯片之前使烧结糊剂的表面平坦化且能够实现高密度安装的半导体装置及其制造方法。

4、用于解决问题的方案

5、本发明的一个方式的主旨在于,一种半导体装置,具备:(a)导电板,其具有主面;(b)半导体芯片,其与导电板的主面相向地配置;以及(c)接合层,其具有配置在导电板与半导体芯片之间的烧结材料,其中,接合层的中央部的空隙率与接合层的端部的至少一部分的空隙率不同。

6、本发明的另一方式的主旨在于,一种半导体装置的制造方法,包括以下工序:(a)在导电板的主面涂布表面设置有突起部的烧结糊剂;(b)使烧结糊剂干燥;(c)通过对烧结糊剂进行加压来将突起部压扁,从而使烧结糊剂的表面平坦化;(d)在导电板的主面隔着烧结糊剂搭载半导体芯片;(e)通过加热和加压使烧结糊剂烧结而形成接合层,经由接合层将导电板与半导体芯片接合。

7、发明的效果

8、根据本发明,能够提供一种能够在搭载功率半导体芯片之前使烧结糊剂的表面平坦化且能够实现高密度安装的半导体装置及其制造方法。

技术特征:

1.一种半导体装置,其特征在于,具备:

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求2所述的半导体装置,其特征在于,

4.根据权利要求1所述的半导体装置,其特征在于,

5.根据权利要求1所述的半导体装置,其特征在于,

6.根据权利要求1~5中的任一项所述的半导体装置,其特征在于,

7.根据权利要求1~5中的任一项所述的半导体装置,其特征在于,

8.根据权利要求1~5中的任一项所述的半导体装置,其特征在于,

9.一种半导体装置的制造方法,其特征在于,包括以下工序:

10.根据权利要求9所述的半导体装置的制造方法,其特征在于,

11.根据权利要求9或10所述的半导体装置的制造方法,其特征在于,

12.根据权利要求9或10所述的半导体装置的制造方法,其特征在于,

13.根据权利要求9或10所述的半导体装置的制造方法,其特征在于,

14.根据权利要求9或10所述的半导体装置的制造方法,其特征在于,

15.根据权利要求9或10所述的半导体装置的制造方法,其特征在于,

16.根据权利要求9或10所述的半导体装置的制造方法,其特征在于,

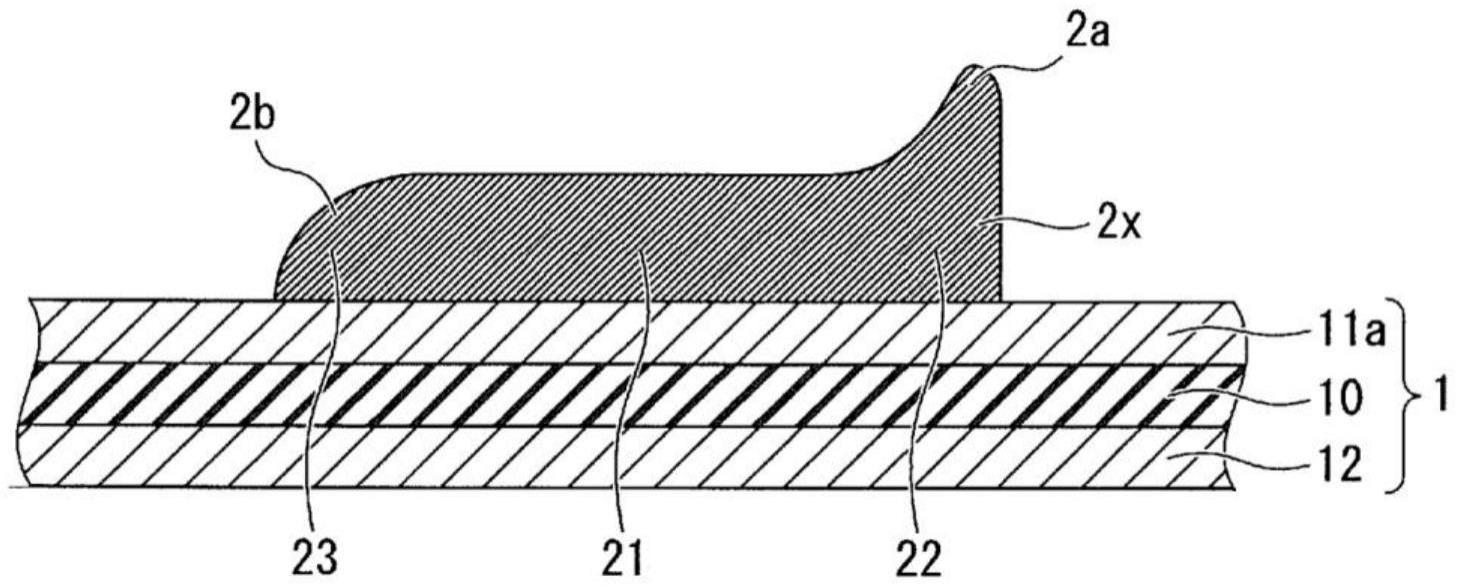

技术总结

提供一种能够在搭载功率半导体芯片之前使烧结糊剂的表面平坦化且能够实现高密度安装的半导体装置的制造方法。包括以下工序:在导电板(11a)的主面涂布表面设置有突起部(2a)的烧结糊剂(2x);使烧结糊剂(2x)干燥;通过对烧结糊剂(2x)进行加压来将突起部(2a)压扁,从而使烧结糊剂(2x)的表面平坦化;在导电板(11a)的主面隔着烧结糊剂(2x)搭载半导体芯片;以及通过加热和加压使烧结糊剂(2x)烧结而形成接合层,经由接合层将导电板(11a)与半导体芯片接合。

技术研发人员:齐藤隆

受保护的技术使用者:富士电机株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!