用以改善装置效能的处理的制作方法

本公开内容的实施方式一般关于半导体装置、系统、工艺、设备和制造。更特定而言,实施方式关于用于增强栅极结构中的装置效能的处理。

背景技术:

1、随着金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effecttransistor;mosfet)的大小减小以实现高装置效能及低功率消耗,传统二氧化硅(sio2)栅极电介质的厚度已减小到其物理极限。因此,用高介电常数介电材料替代二氧化硅栅极电介质来实现进一步缩放已经是不可避免的。在各种高介电常数介电材料之中,由于氧化铪(hfo2)的高介电常数及在硅基板上的优异热稳定性,自45nm mosfet技术节点以来已经应用氧化铪(hfo2)。然而,为了进一步缩放(scaling)32nm mosfet技术节点及以上的等效氧化物厚度(equivalent oxide thickness;eot),由于穿过高介电常数介电材料层的泄漏电流的增加,简单地减小高介电常数介电材料层的厚度是有问题的。

2、因此,需要可以用于形成薄(例如,eot小于1nm)高介电常数介电材料层的系统及方法,这些高介电常数介电材料层具有可以经控制以确保期望结构及电气性质的化学结构。

技术实现思路

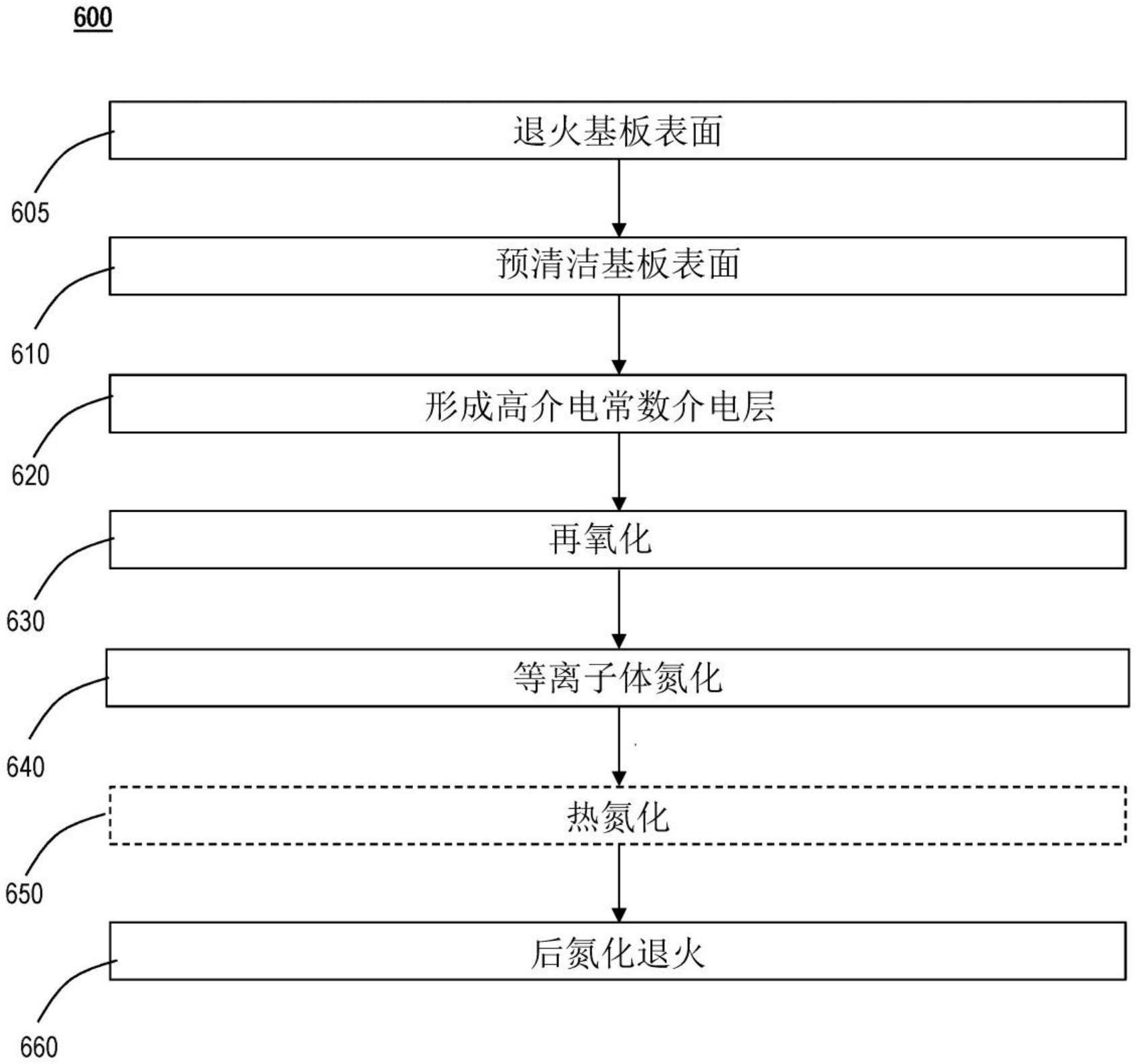

1、本公开内容的一个或多个实施方式涉及形成半导体装置的方法。在一个或多个实施方式中,该方法包含:退火基板表面以形成平整(smooth)表面;预清洁平整表面以形成预清洁的表面;在预清洁的表面上沉积高介电常数介电层;执行再氧化工艺以热氧化基板;执行等离子体氮化工艺以将氮原子插入高介电常数介电层中来形成等离子体氮化的高介电常数介电层;和执行后氮化退火工艺(post-nitridation anneal process)以钝化等离子体氮化的高介电常数介电层中的化学键。

2、本公开内容的一个或多个实施方式涉及形成半导体装置的方法。在一个或多个实施方式中,该方法包含:退火基板表面以形成平整表面;在基板表面上形成高介电常数介电层;执行再氧化工艺以热氧化基板表面;执行等离子体氮化工艺以将氮原子插入高介电常数介电层中来形成等离子体氮化的高介电常数介电层;和执行后氮化退火工艺以钝化等离子体氮化的高介电常数介电层中的化学键。

3、本公开内容的其他实施方式涉及处理系统。在一个或多个实施方式中,一种处理系统包含:第一处理腔室;第二处理腔室;第三处理腔室;第四处理腔室;第五处理腔室;以及系统控制器,该系统控制器被构造为:在第一处理腔室中退火基板表面以形成平整表面;在第二处理腔室中在基板表面上沉积高介电常数介电层;在第三处理腔室中将沉积的高介电常数介电层暴露于氮等离子体以形成等离子体氮化的高介电常数介电层;在第四处理腔室中执行再氧化工艺以热氧化基板表面;以及在第五处理腔室中退火等离子体氮化的高介电常数介电层,其中基板在第一、第二、第三、第四和第五处理腔室之中传送而不破坏处理系统中的真空环境。

技术特征:

1.一种形成半导体结构的方法,所述方法包含以下步骤:

2.如权利要求1所述的方法,其中沉积所述高介电常数介电层、执行所述再氧化工艺、执行所述等离子体氮化工艺和执行所述后氮化退火工艺在处理系统中执行而不破坏真空。

3.如权利要求1所述的方法,其中退火所述基板的所述表面的步骤包含以下步骤:在从500℃至700℃的范围中的温度下在氢(h2)氛围中尖峰退火所述基板。

4.如权利要求1所述的方法,其中所述等离子体氮化工艺包含以下步骤:将所述高介电常数介电层暴露于包含氮(n2)及氨(nh3)的混合物的等离子体。

5.如权利要求1所述的方法,其中所述再氧化工艺包含以下步骤:在从400℃至900℃的范围中的温度下在氧(o2)、氧化亚氮(n2o)和氢(h2)氛围中退火所述高介电常数介电层。

6.如权利要求1所述的方法,其中所述后氮化退火工艺包含以下步骤:在从700℃至850℃的范围中的温度下在氮(n2)及氩(ar)氛围中尖峰退火所述高介电常数介电层。

7.如权利要求1所述的方法,进一步包含以下步骤:在所述等离子体氮化工艺之前执行后沉积退火工艺以硬化及致密化所述高介电常数介电层。

8.如权利要求7所述的方法,其中所述后沉积退火工艺包含以下步骤:在从500℃至800℃的范围中的温度下在氮(n2)及氩(ar)氛围中退火所述高介电常数介电层。

9.如权利要求1所述的方法,其中所述高介电常数介电层包含氧化铪。

10.一种形成半导体结构的方法,所述方法包含以下步骤:

11.如权利要求10所述的方法,其中形成所述半导体结构的步骤在处理系统中执行而不破坏真空。

12.如权利要求10所述的方法,其中退火所述基板的所述表面的步骤包含以下步骤:在从500℃至700℃的范围中的温度下在氢(h2)氛围中尖峰退火所述基板。

13.如权利要求10所述的方法,其中所述高介电常数介电层包含氧化铪。

14.如权利要求10所述的方法,其中所述等离子体氮化工艺包含以下步骤:将所述高介电常数介电层暴露于包含氮(n2)及氨(nh3)的混合物的等离子体。

15.如权利要求10所述的方法,进一步包含以下步骤:在所述平整表面上形成所述高介电常数介电层之前预清洁所述平整表面。

16.如权利要求10所述的方法,进一步包含以下步骤:在退火所述基板的所述表面之前预清洁所述基板的所述表面。

17.如权利要求10所述的方法,其中所述后氮化退火工艺包含以下步骤:在700℃至850℃的范围中的温度下在氮(n2)及氩(ar)氛围中尖峰退火所述高介电常数介电层。

18.如权利要求10所述的方法,进一步包含以下步骤:在所述等离子体氮化工艺之前执行后沉积退火工艺以硬化及致密化所述高介电常数介电层。

19.如权利要求18所述的方法,其中所述后沉积退火工艺包含以下步骤:在从500℃至800℃的范围中的温度下在氮(n2)及氩(ar)氛围中退火所述高介电常数介电层。

20.一种处理系统,包含:

技术总结

一种形成半导体结构的方法包括在氢的氛围中退火基板表面以使表面平整,预清洁基板表面,在基板的预清洁表面上沉积高介电常数介电层,执行再氧化工艺以热氧化基板表面;执行等离子体氮化工艺以将氮原子插入沉积的高介电常数介电层中,以及执行后氮化退火工艺以钝化等离子体氮化的高介电常数介电层中的化学键。

技术研发人员:史蒂文·C·H·洪,董琳,本杰明·科伦坡,约翰内斯·F·斯温伯格,王林林

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!