碳化硅半导体装置及使用它的逆变器电路、碳化硅半导体装置的制造方法与流程

本公开涉及具有沟槽栅构造的碳化硅(以下也简称作sic)半导体装置及使用它的逆变器(inverter)电路、sic半导体装置的制造方法。

背景技术:

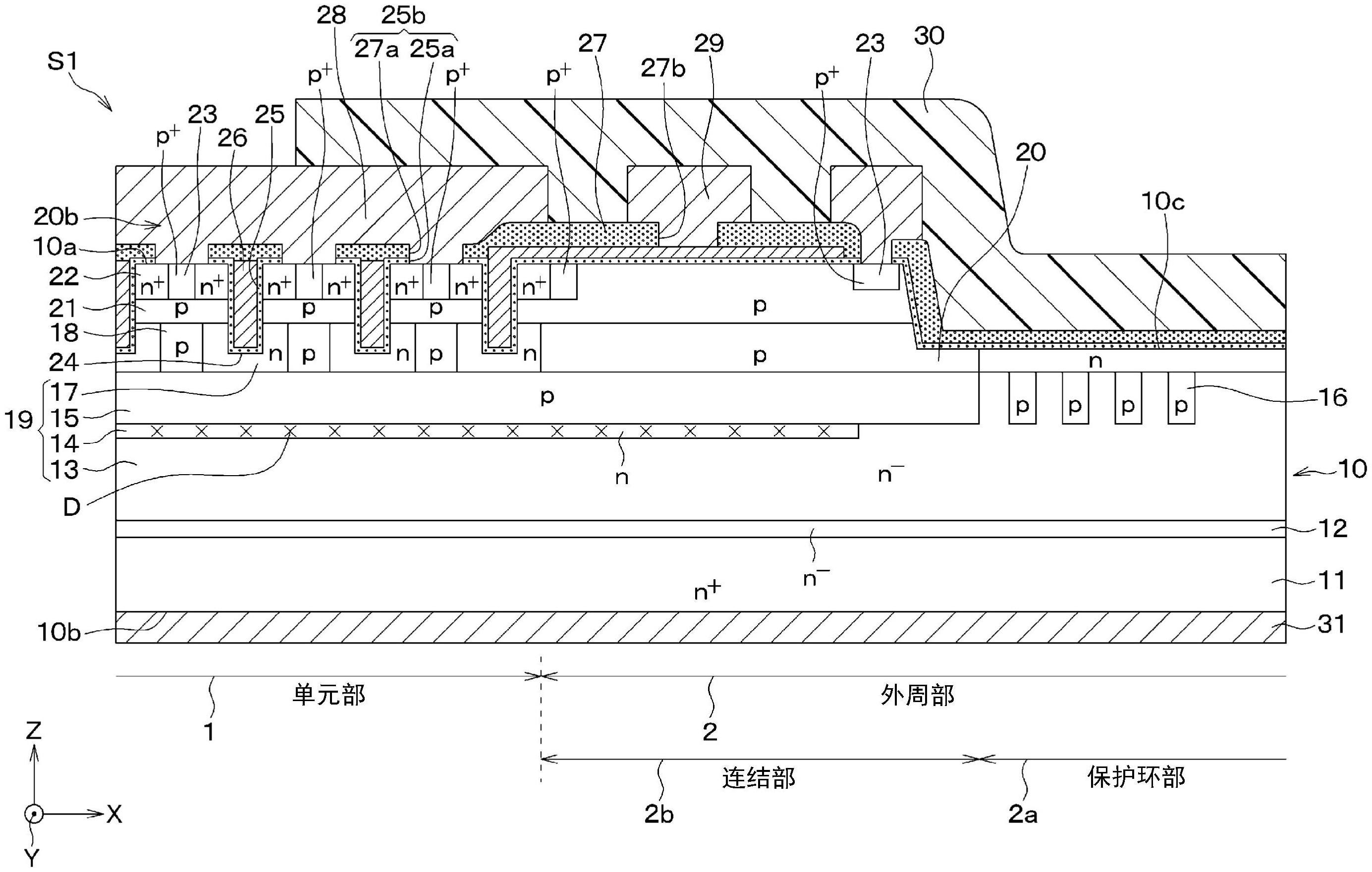

1、以往,提出了形成有具有沟槽栅构造的mosfet(metal oxide semiconductorfield effect transistor的简称)的sic半导体装置(例如参照专利文献1)。具体而言,在该sic半导体装置中,在n+型的衬底上,形成有杂质浓度比衬底低的n-型的缓冲层,在缓冲层上,形成有杂质浓度比缓冲层低的低浓度层。而且,在低浓度层上,形成有以一个方向作为长度方向而延伸设置的p型的第1深层、和n型的jfet部。另外,第1深层及jfet部以在相邻的第1深层之间配置jfet部的方式,沿着与长度方向交叉的方向交替地配置第1深层和jfet部。

2、在第1深层及jfet部上,配置有n型的电流分散层及p型的第2深层。在电流分散层及第2深层上,配置有p型的基极(base)层。另外,第2深层以将第1深层与基极层连接的方式配置。

3、在基极层的表层部,形成有n+型的源极区域。并且,以将源极区域及基极层贯通而达到电流分散层的方式形成有多个沟槽,在各沟槽中依次形成有栅极绝缘膜及栅极电极。由此,形成沟槽栅构造。

4、现有技术文献

5、专利文献

6、专利文献1:日本特开2019-016775号公报

技术实现思路

1、此外,上述那样的sic半导体装置,通过基极层等与电流分散层等的pn结而构成寄生二极管。因此,可以认为,这样的sic半导体装置在反向导通时利用寄生二极管。

2、但是,在上述那样的sic半导体装置中,有在衬底中存在基面位错(即,basalplane dislocation,以下也简称作bpd)的情况。并且,在上述那样的sic半导体装置中,有可能反向导通时注入的空穴到达基面位错而基面位错扩展为堆垛层错(stacking fault,以下也简称作sf)。该情况下,bpd由于是线状缺陷所以对元件动作带来的影响较小,而sf由于为面状缺陷所以对元件动作带来的影响较大。因而,在上述那样的sic半导体装置中,导通电压有可能升高。

3、本公开的目的在于,提供能够抑制导通电压的升高的sic半导体装置及使用它的逆变器电路、sic半导体装置的制造方法。

4、根据本公开的一个方面,sic半导体装置,具有:单元部,形成有开关元件;以及外周部,将单元部包围;单元部具备:第1导电型的衬底,由碳化硅构成;第1导电型的缓冲层,形成在衬底上,杂质浓度比衬底低;第1导电型的低浓度层,形成在缓冲层上,杂质浓度比衬底低;第2导电型的第1深层,形成在低浓度层上,具有以衬底的面方向中的一个方向为长度方向的多个线状部分;第1导电型的jfet部,配置在低浓度层上,具有被第1深层夹着的线状部分;第1导电型的电流分散层,配置在jfet部上,杂质浓度比低浓度层高;第2导电型的第2深层,配置在第1深层上;第2导电型的基极层,配置在电流分散层及第2深层之上;第1导电型的杂质区域,形成在基极层的表层部;沟槽栅构造,具有在沟槽的壁面形成的栅极绝缘膜和在栅极绝缘膜上形成的栅极电极,沟槽将杂质区域及基极层贯通而达到电流分散层;第1电极,与杂质区域及基极层电连接;以及第2电极,与衬底电连接。并且,在jfet部中形成有缺陷部。

5、由此,在sic半导体装置的反向导通时,载流子(例如空穴)被缺陷部俘获从而能够抑制其到达bpd。因而,能够抑制bpd扩展为sf,能够抑制导通电压的变高。

6、根据本公开的另一方面,具有并联连接着mosfet和续流二极管的臂的逆变器电路具备上述的sic半导体装置;mosfet由开关元件构成;续流二极管由在开关元件内构成的寄生二极管构成。

7、由此,作为在逆变器电路中具备的续流二极管,利用在sic半导体装置中构成的寄生二极管。因此,不需要在mosfet之外准备构成续流二极管的其他部件,能够实现结构的简化。

8、根据本公开的另一方面,关于上述的sic半导体装置的制造方法,进行以下工序:通过外延层配置低浓度层;以及通过对低浓度层的表层部进行离子注入而构成jfet部;通过进行离子注入,在jfet部中形成缺陷部。

9、由此,能够容易地制造形成有在反向导通时将载流子(例如空穴)俘获的缺陷部的sic半导体装置。

10、另外,对各构成要素等赋予的带括号的标号表示该构成要素等与在后述的实施方式中记载的具体的构成要素等的对应关系的一例。

技术特征:

1.一种碳化硅半导体装置,形成有具有沟槽栅构造的mos构造的开关元件,其特征在于,

2.如权利要求1所述的碳化硅半导体装置,其特征在于,

3.如权利要求1或2所述的碳化硅半导体装置,其特征在于,

4.如权利要求1~3中任一项所述的碳化硅半导体装置,其特征在于,

5.如权利要求1~4中任一项所述的碳化硅半导体装置,其特征在于,

6.如权利要求1~5中任一项所述的碳化硅半导体装置,其特征在于,

7.如权利要求1~6中任一项所述的碳化硅半导体装置,其特征在于,

8.如权利要求7所述的碳化硅半导体装置,其特征在于,

9.如权利要求1~8中任一项所述的碳化硅半导体装置,其特征在于,

10.如权利要求1~9中任一项所述的碳化硅半导体装置,其特征在于,

11.如权利要求1~10中任一项所述的碳化硅半导体装置,其特征在于,

12.如权利要求11所述的碳化硅半导体装置,其特征在于,

13.如权利要求12所述的碳化硅半导体装置,其特征在于,

14.一种逆变器电路,具有并联连接着mosfet(s11)和续流二极管(s12)的臂,其特征在于,

15.一种碳化硅半导体装置的制造方法,

16.如权利要求15所述的碳化硅半导体装置的制造方法,其特征在于,

17.如权利要求15或16所述的碳化硅半导体装置的制造方法,其特征在于,

18.如权利要求15~17中任一项所述的碳化硅半导体装置的制造方法,其特征在于,

技术总结

具备:第1导电型的衬底(11),由碳化硅构成;第1导电型的缓冲层(12),形成在衬底(11)上;低浓度层(13),形成在缓冲层(12)上;第1深层(15)及JFET部(14),形成在低浓度层(13)上;第1导电型的电流分散层(17),配置在JFET部(14)上,杂质浓度比低浓度层(13)高;第2导电型的第2深层(18),配置在第1深层(15)上;第2导电型的基极层(21),配置在电流分散层(17)及第2深层(18)之上;第1导电型的杂质区域(22),形成在基极层(21)的表层部;以及沟槽栅构造,以将杂质区域(22)及基极层(21)贯通而达到电流分散层(17)的方式形成。并且,使得在JFET部(14)中形成缺陷部(D)。

技术研发人员:上原准市,羽山优介

受保护的技术使用者:株式会社电装

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!