半导体装置及其制造方法与流程

本发明涉及半导体装置及其制造方法,特别涉及树脂密封型的半导体装置及其制造方法。

背景技术:

1、例如,在专利文献1中公开了如下电子装置,在层叠有多个布线的多层基板的上表面上装载了半导体芯片及无源元件等多个电子部件。并且,各电子部件通过接合线被连接于在多层基板的上表面配置的各布线。

2、并且,在专利文献2中公开了如下设备,在引线框的上表面上通经由凸块装载了半导体芯片。并且,在上述引线框的周围设有由与上述引线框相同的材料被蚀刻加工而成的端子,半导体芯片的电路径经由上述引线框及上述端子被拉上至装置的上表面侧。

3、现有技术文献

4、专利文献

5、专利文献1:日本专利第5983523号公报

6、专利文献2:日本特表2013-524552号公报

技术实现思路

1、发明所要解决的技术问题

2、专利文献1是在多层基板的上表面上装载多个电子部件的平面安装,所以受到接合线及层叠布线的影响,导致各部件之间的电阻值及电感值升高,容易产生开闭损耗。并且,在平面安装中,若部件的数量增多,则安装面积(封装体的尺寸)增大,难以促进封装体的小型化。并且,由于是多层基板,与需要较高的散热性的大功率mos晶体管的多芯片化困难。

3、专利文献2是使用了引线框的倒装芯片安装构造,由于从半导体芯片到装置的上表面的电路径较长,所以与专利文献1同样导致电阻值及电感值升高,产生开闭损耗。

4、本申请的主要目的在于,在半导体芯片及无源元件等多个电子部件之间,抑制电阻值及电感值的上升,改善开闭损耗。即,本申请的主要目的在于使半导体装置的性能提高。其他的问题及新的特征由本说明书的记述及附图得以明确。

5、用于解决问题的技术方案

6、一个实施方式中的半导体装置具备:第一芯片焊盘,由导电材料构成;第一半导体芯片,设于所述第一芯片焊盘的上表面上;以及第二半导体芯片。在此,所述第一半导体芯片具有第一焊盘电极以及第三焊盘电极,所述第一焊盘电极在所述第一半导体芯片的上表面形成,所述第三焊盘电极在所述第一半导体芯片的下表面形成,并且电连接于所述第一芯片焊盘,所述第二半导体芯片具有在所述第二半导体芯片的上表面形成的第二焊盘电极,在所述第一焊盘电极的上表面上,以电连接于所述第一焊盘电极的方式设有第一导电层,在所述第二焊盘电极的上表面上,以电连接于所述第二焊盘电极的方式设有第二导电层,通过第一树脂层以使得所述第一导电层的上表面、所述第二导电层的上表面及所述第一芯片焊盘的下表面暴露的方式,将所述第一芯片焊盘、所述第一半导体芯片、所述第二半导体芯片、所述第一导电层以及所述第二导电层密封,在所述第一导电层及所述第二导电层各自的上表面上,以电连接于所述第一导电层及所述第二导电层的方式设有一个以上的无源元件。

7、一实施方式中的半导体装置的制造方法包括:(a)工序,准备金属板、第一半导体芯片、第二半导体芯片、第一导电层、以及第二导电层,所述金属板由导电材料构成,所述第一半导体芯片具有在上表面形成的第一焊盘电极及在下表面形成的第三焊盘电极,所述第二半导体芯片具有在上表面形成的第二焊盘电极,所述第一导电层设于所述第一焊盘电极的上表面上且电连接于所述第一焊盘电极的第一导电层,所述第二导电层设于所述第二焊盘电极的上表面上且电连接于所述第二焊盘电极的第二导电层;(b)工序,在所述(a)工序之后,在基材的上表面上设置所述金属板;(c)工序,在所述(b)工序之后,通过选择性地蚀刻所述金属板而形成第一芯片焊盘;(d)工序,在所述(c)工序之后,以所述第三焊盘电极电连接于所述第一芯片焊盘的方式,在所述第一芯片焊盘的上表面上设置所述第一半导体芯片;(e)工序,在所述(c)工序之后,在所述基材的上表面上设置所述第二半导体芯片;(f)工序,在所述(d)工序及所述(e)工序之后,通过第一树脂层以覆盖所述第一导电层及所述第二导电层各自的上表面的方式,将所述第一芯片焊盘、所述第一半导体芯片、所述第二半导体芯片、所述第一导电层以及所述第二导电层密封;(g)工序,在所述(f)工序之后,通过研磨所述第一树脂层,使所述第一导电层及所述第二导电层各自的上表面从所述第一树脂层暴露;(h)工序,在所述(g)工序之后,通过将所述基材去除,使所述第一芯片焊盘的下表面从所述第一树脂层暴露;(i)工序,在所述(h)工序之后,在所述第一导电层及所述第二导电层各自的上表面上,以将所述第一导电层及所述第二导电层电连接的方式设置一个以上的无源元件。

8、发明效果

9、根据一个实施方式,能够提高半导体装置的性能。

技术特征:

1.一种半导体装置,具备:

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1所述的半导体装置,其中,

4.根据权利要求1所述的半导体装置,其中,

5.根据权利要求4所述的半导体装置,其中,

6.根据权利要求4所述的半导体装置,其中,

7.根据权利要求1所述的半导体装置,其中,

8.根据权利要求1所述的半导体装置,其中,

9.根据权利要求1所述的半导体装置,其中,

10.根据权利要求1所述的半导体装置,其中,

11.一种半导体装置的制造方法,包括:

12.根据权利要求11所述的半导体装置的制造方法,其中,

13.根据权利要求11所述的半导体装置的制造方法,其中,

14.根据权利要求11所述的半导体装置的制造方法,其中,

15.根据权利要求14所述的半导体装置的制造方法,其中,

16.根据权利要求14所述的半导体装置的制造方法,其中,

17.根据权利要求11所述的半导体装置的制造方法,其中,

18.根据权利要求1所述的半导体装置的制造方法,其中,

19.根据权利要求11所述的半导体装置的制造方法,其中,

20.根据权利要求11所述的半导体装置的制造方法,其中,

技术总结

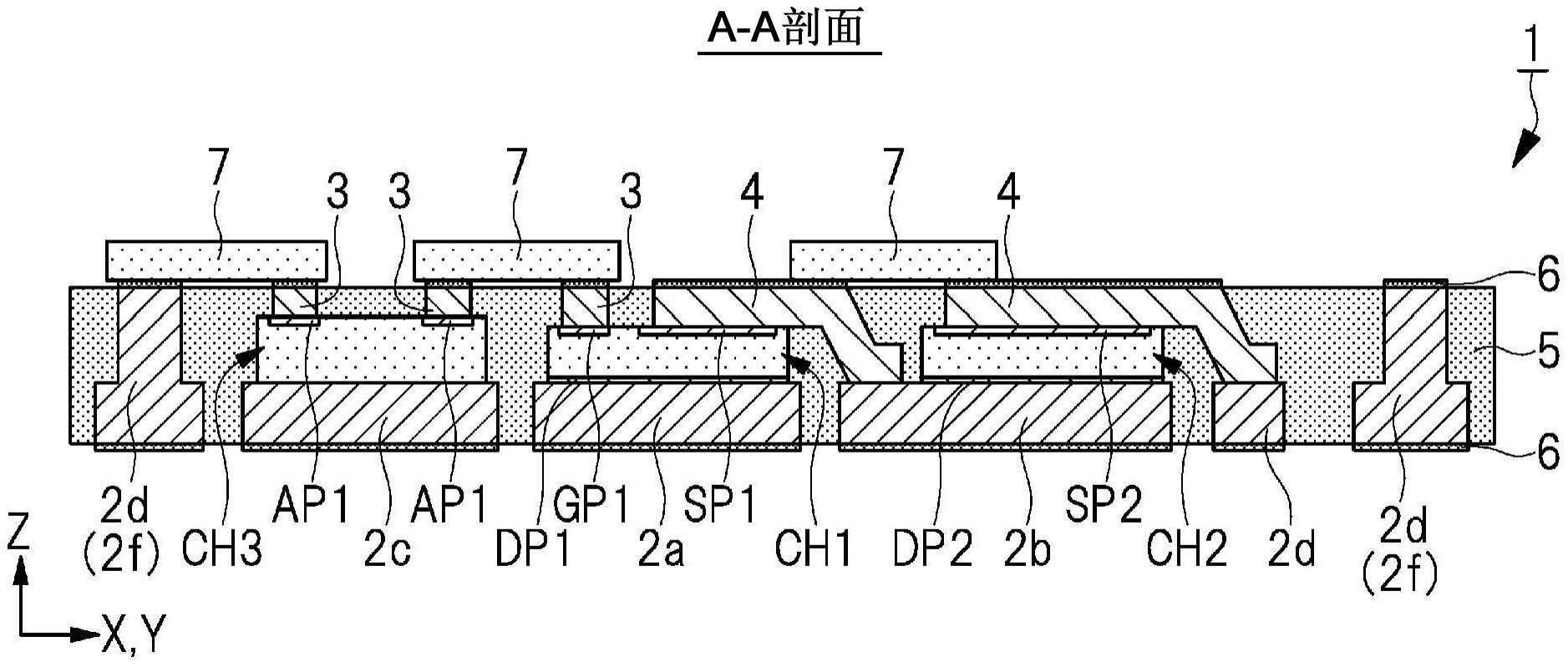

本发明使半导体装置的性能提高。半导体装置(1)具备由导电材料构成的芯片焊盘(2a)、在芯片焊盘(2a)的上表面上设置的半导体芯片(CH1)、以及半导体芯片(CH3)。半导体芯片(CH1)具有栅极焊盘电极(GP1)及漏极焊盘电极(DP1),半导体芯片(CH3)具有焊盘电极(AP1)。在栅极焊盘电极(GP1)及焊盘电极(AP1)各自的上表面上,以电连接于栅极焊盘电极(GP1)及焊盘电极(AP1)的方式设有导电层(3)。通过树脂层(5)以使得导电层(3)的上表面及芯片焊盘(2a)的下表面暴露的方式,将芯片焊盘(2a)、半导体芯片(CH1)、半导体芯片(CH3)及导电层(3)密封。在两个导电层(3)的上表面上设有具备一个以上的无源元件的无源元件部件(7)。

技术研发人员:高尾胜大,黑羽淳史,相沢吉昭

受保护的技术使用者:青井电子株式会社

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!