碳化硅半导体装置及其制造方法与流程

本发明涉及一种碳化硅(sic)半导体装置及其制造方法。

背景技术:

1、已知在市售的碳化硅(sic)单晶基板中包含有以基面位错(bpd)为首的大量的位错。这种位错被在基板上外延生长sic单晶而得到的外延基板所继承。因此,会对外延基板中形成的半导体装置的特性造成不良影响。

2、在将sic用作半导体材料的mos场效应晶体管(fet)等半导体装置(sic半导体装置)中,在外延基板设置有具有pn结的内置二极管。基面位错成为在关断时进行双极动作的内置二极管的正向特性的劣化的原因。例如,在双极动作时通过正向通电而产生的少数载流子、例如n型半导体中的空穴在外延基板之中扩散。当少数载流子在基面位错复合而将复合能量提供给基面位错时,以基面位错为起点,层错在外延基板中扩展。若层错扩展,则在内置二极管中流通了正向电流时,正向电压(接通电压)上升,正向电阻(接通电阻)增大。这样,当元件特性劣化时,产生的损耗随着时间推移而增加,发热量也变大,因此成为半导体装置故障的原因。

3、层错从n型的基板与作为n型外延生长层的漂移层的界面扩展。因此,通过在基板与漂移层之间配置高浓度的n+型的复合促进层,能够使从表面电极侧注入到漂移层的空穴复合。另外,还已知,取代复合促进层,而是通过照射质子等寿命抑制剂形成寿命抑制区来防止层错的扩展。关于寿命抑制剂的照射,与将硅(si)用于半导体材料的半导体装置(si半导体装置)的情况同样地,一般在表面侧的金属的金属形成后进行寿命抑制剂的照射。

4、在专利文献1中公开了以下内容:向sic半导体基板与n型边界层的界面附近注入质子等来作为寿命抑制剂。在专利文献2中公开了以下内容:向n型漂移层上的p型外延层的内部注入质子等来形成寿命抑制区。

5、现有技术文献

6、专利文献

7、专利文献1:日本特开2019-102493号公报

8、专利文献2:日本特开2019-003969号公报

技术实现思路

1、发明要解决的问题

2、在形成复合促进层的情况下,要求复合促进层为10μm左右的厚度,因此制造成本增大。另一方面,在形成寿命抑制区的情况下,如果是si半导体装置,则寿命抑制剂一般会对少数载流子有影响,但是对多数载流子几乎没有影响,从而对mosfet的接通电阻几乎没有影响。然而,在sic半导体装置中,寿命抑制剂对多数载流子也造成影响,特别是,当向漂移层中照射寿命抑制剂时mosfet的接通电阻增大。

3、另外,在si半导体装置中,为了降低对栅极绝缘膜的影响,将寿命抑制剂从si基板的背面侧照射到不会对栅极绝缘膜造成影响的程度的深度。另一方面,在sic半导体装置中,sic基板的厚度比si基板的厚度厚,因此厚度存在偏差,在sic基板上外延生长出的漂移层的厚度比si半导体装置的漂移层的厚度薄。因此,当从sic基板的背面侧照射寿命抑制剂时,寿命抑制剂在漂移层内存在偏差地分布,mosfet的接通电阻存在偏差。

4、本发明鉴于上述问题,目的在于提供一种能够抑制内置二极管的通电劣化、以及有源元件的接通电阻的偏差的sic半导体装置及其制造方法。

5、用于解决问题的方案

6、为了实现上述目的,本发明的一个方式的主旨在于,一种sic半导体装置,具备:(a)第一导电型的漂移层,其设置于第一导电型的碳化硅基板的上表面侧;(b)第二导电型的基区,其设置于漂移层的上表面侧;(c)第一导电型的主区,其与基区相接地设置于漂移层的上表面侧;(d)绝缘栅型电极构造,其与主区及基区相接地设置;以及(e)寿命抑制区,其被设置为包括漂移层的下表面。

7、本发明的其它方式的主旨在于,一种sic半导体装置的制造方法,包括以下工序:(a)在第一导电型的碳化硅基板的上表面侧外延生长第一导电型的漂移层;(b)在漂移层的上表面侧形成第二导电型的基区;(c)在漂移层的上表面侧以与基区相接的方式形成第一导电型的主区;(d)以与基区及主区相接的方式形成栅极绝缘膜;(e)以隔着栅极绝缘膜来与基区及主区相接的方式形成栅极电极;以及(f)在外延生长漂移层的工序之后、且形成栅极绝缘膜的工序之前,从漂移层的上表面侧照射寿命抑制剂,来在包括漂移层的下表面的深度处形成寿命抑制区。

8、发明的效果

9、根据本发明,能够提供一种能够抑制内置二极管的通电劣化、以及有源元件的接通电阻的偏差的sic半导体装置及其制造方法。

技术特征:

1.一种碳化硅半导体装置,其特征在于,具备:

2.根据权利要求1所述的碳化硅半导体装置,其特征在于,

3.根据权利要求2所述的碳化硅半导体装置,其特征在于,

4.根据权利要求2所述的碳化硅半导体装置,其特征在于,

5.根据权利要求1或2所述的碳化硅半导体装置,其特征在于,

6.根据权利要求1或2所述的碳化硅半导体装置,其特征在于,

7.一种碳化硅半导体装置的制造方法,其特征在于,包括以下工序:

8.根据权利要求7所述的碳化硅半导体装置的制造方法,其特征在于,

9.根据权利要求7或8所述的碳化硅半导体装置的制造方法,其特征在于,

10.根据权利要求7或8所述的碳化硅半导体装置的制造方法,其特征在于,

11.根据权利要求7或8所述的碳化硅半导体装置的制造方法,其特征在于,

12.根据权利要求7或8所述的碳化硅半导体装置的制造方法,其特征在于,

13.根据权利要求7或8所述的碳化硅半导体装置的制造方法,其特征在于,

14.根据权利要求7或8所述的碳化硅半导体装置的制造方法,其特征在于,

15.根据权利要求8所述的碳化硅半导体装置的制造方法,其特征在于,

技术总结

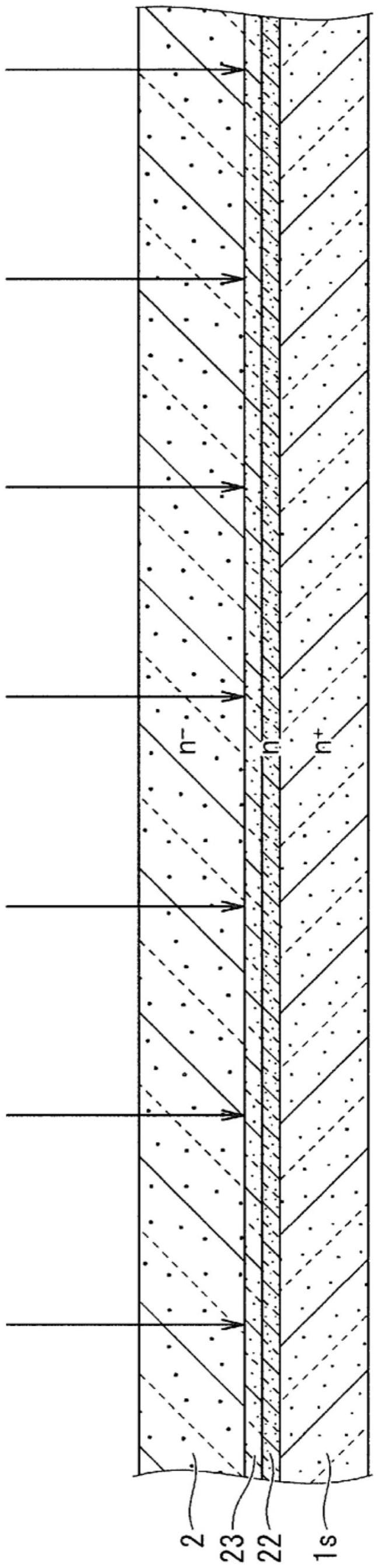

提供一种能够抑制内置二极管的通电劣化、以及有源元件的接通电阻的偏差的碳化硅半导体装置的制造方法。包括以下工序:在第一导电型的碳化硅基板(1s)的上表面侧外延生长第一导电型的漂移层(2);在漂移层(2)的上表面侧形成第二导电型的基区;在漂移层(2)的上表面侧以与基区相接的方式形成第一导电型的主区;以与基区及主区相接的方式形成栅极绝缘膜;以隔着栅极绝缘膜来与基区及主区相接的方式形成栅极电极;以及在外延生长漂移层(2)的工序之后、且形成栅极绝缘膜的工序之前,从漂移层(2)的上表面侧照射寿命抑制剂,来在包括漂移层(2)的下表面的深度处形成寿命抑制区(23)。

技术研发人员:市川义人,木下明将

受保护的技术使用者:富士电机株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!