晶体管及其制造方法与流程

本发明涉及一种晶体管及其制造方法,更详细地涉及一种其尺寸小型化的晶体管和其制造方法。

背景技术:

1、随着5g通信服务的构建扩大,在高速开关环境或高电压环境下工作的高耐压晶体管的必要性正在增加。为响应这样的必要性,最近登场的氮化镓(gan)类晶体管比起以往的硅(si)类晶体管,能够高速开关工作,不仅适合超高速信号处理、还可以通过元件自身的高耐压特性稳定地适用于高电压环境而备受瞩目。

2、利用氮化镓(gan)的高电子迁移率晶体管(hemt,high electron mobilitytransistor)利用在异物质间表面上发生的二维电子气(2deg,2-dimensional electrongas),从而具有可以提高电子迁移率(mobility),适合高速信号传输的优点。

3、这样的高电子迁移率晶体管如碳化硅(sic)基板那样,制造于通孔(via-hole)蚀刻非常困难的基板上。具体而言,为了在基板形成通孔,通过背面研磨(back-grinding)工艺将基板加工为薄至100μm以下之后,在基板的背面形成掩模图案,执行等离子体蚀刻。

4、在进行等离子体蚀刻期间,可以破坏形成于基板前面的构造物,因此若表面的构造物暴露时就要停止蚀刻。

5、随之,以往,作为能够在外延层上部使蚀刻停止的蚀刻停止层在配置ni层的状态下,以蚀刻基板和外延层的方式进行。

6、但是,在以往方式中,为了蚀刻基板和外延层,不仅蚀刻工艺复杂,由于蚀刻停止层导致晶体管的尺寸变大,存在因过少或过度的蚀刻而产生不良品的问题。

7、本发明的背景技术是为了更容易理解本发明而制定的。在本发明的背景技术中所记载的事项不应被理解为承认作为现有技术存在。

技术实现思路

1、本发明的目的在于,提供一种在晶体管的前面形成插塞后,从基板的后面蚀刻通孔至插塞的表面被暴露,从而用插塞将源极电极与形成在通孔的金属层电连接的方法及通过其制造的晶体管。

2、本发明的课题不被以上提及到的课题所限定,可以从以下的记载中明确地理解未提及的又其它课题。

3、根据本发明实施例的一种晶体管的制造方法,其中,包括:配置在上方形成有外延层的基板的步骤;以使外延层的一部分区域暴露的方式形成绝缘层的步骤;在外延层形成贯通从绝缘层暴露的一部分区域的插塞的步骤;在插塞及暴露的外延层上部形成导电层的步骤;在基板以使插塞的下表面暴露的方式形成通孔的步骤以及形成覆盖基板的下部的金属层的步骤。

4、根据实施例,其特征在于,形成插塞的步骤是通过蚀刻外延层来形成沟槽构造,并在沟槽构造形成插塞。

5、根据实施例,其特征在于,沟槽构造形成为穿过外延层而贯通至基板的一部分。

6、根据实施例,其特征在于,所述晶体管的制造方法在形成插塞的步骤之后还包括加工基板的下表面以使基板的厚度减小的步骤。

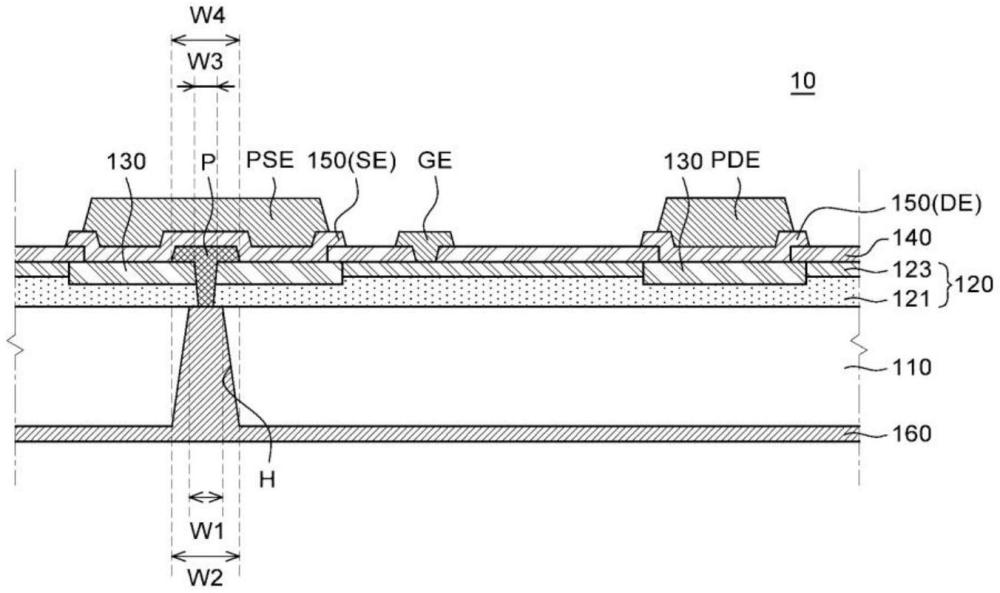

7、根据实施例,其特征在于,插塞及通孔在侧面方向上通孔的宽度比插塞的宽度大。

8、根据实施例,其特征在于,通孔的与插塞下表面抵接的上宽度小于或等于不抵接的下宽度。

9、根据实施例,其特征在于,形成通孔的步骤是穿过基板来蚀刻外延层的一部分而形成通孔,从而使插塞的下区域暴露。

10、根据实施例,其特征在于,所述晶体管的制造方法在配置基板的步骤之后还包括向外延层的至少一部分注入n型掺杂剂来形成离子注入层的步骤。

11、根据实施例,其特征在于,外延层包括依次配置于基板上方的缓冲层及阻挡层。

12、根据实施例,其特征在于,阻挡层由氮化镓(gan)层、alxgayn(x+y=1)层、alxinyn(x=y=1)层及alxinygazn(x+y+z=1)层中的两个以上的多层形成。

13、根据实施例,其特征在于,形成金属层的步骤填充通孔内部。

14、根据本发明实施例的晶体管,其中,包括:基板,在上方形成有外延层;绝缘层,配置于外延层上方,并暴露外延层的一部分区域;插塞,贯通从绝缘层暴露的外延层的一部分区域;导电层,配置于插塞及暴露的外延层上部,并与插塞接触;以及金属层,配置于基板的下方,并与从基板暴露的插塞接触,并且通过插塞与导电层电连接。

15、根据实施例,基板包括形成在配置有插塞的位置的通孔。

16、根据实施例,其特征在于,通孔的与插塞下表面抵接的上宽度比不抵接的下宽度小或者相同。

17、根据实施例,其特征在于,外延层包括依次配置于基板上方的缓冲层和阻挡层。

18、根据实施例,其特征在于,阻挡层由氮化镓(gan)层、alxgayn(x+y=1)层、alxinyn(x=y=1)层及alxinygazn(x+y+z=1)层中的两个以上的多层形成。

19、根据实施例,其特征在于,插塞穿过所述外延层并贯通至所述基板,金属层围绕从所述基板暴露的所述插塞的下区域。

20、根据实施例,还包括配置于位于导电层的下方的外延层的上方的离子注入层。

21、根据实施例,其特征在于,离子注入层的末端与绝缘层的未暴露的区域重叠。

22、根据实施例,其特征在于,金属层形成为填充通孔内部。

23、根据实施例,其特征在于,插塞形成为t字形状。

24、根据实施例,其特征在于,插塞的至少一部分由彼此不同的金属以多层形成。

25、根据实施例,其特征在于,插塞与通孔抵接的下宽度形成为比与插塞抵接的通孔的上宽度小,与导电层重叠的上宽度形成为比通孔的上宽度小。

26、根据实施例,其特征在于,插塞与金属层在所述活塞的下表面接触或者在下区域中接触。

27、根据实施例,晶体管包括源极电极、漏极电极及栅极电极。

28、根据实施例,其特征在于,插塞及通孔形成在源极电极的下方。

29、可以是,本发明在晶体管的前面形成插塞后,从基板的后面蚀刻通孔至插塞的表面被暴露,从而节约蚀刻时间,简化蚀刻过程。

30、另外,可以是,本发明的缓冲层起到和蚀刻停止层相同的作用,因此省略单独的蚀刻停止层。

31、另外,可以是,本发明不贯通缓冲层,具有比以往相对小的宽度,因此源极电极的最小尺寸比以往相对小,从而显著缩小晶体管的尺寸并使其小型化。

32、另外,可以是,本发明通过厚的缓冲层而停止蚀刻,因此可以解决由于通孔的过少或过度的蚀刻而产生不良品的问题。

33、另外,可以是,本发明的缓冲层没有被通孔贯通并将其保留了下来,因此与以往技术相比,机械稳定性优异,并可以降低由于根据晶体管的温度变化引起的机械问题而引起的故障的发生。

34、另外,可以是,本发明用金属填充通孔内部,从而可以提高热传导率,改善散热特性。

35、本发明的各种有益的优点和效果不被上述内容所限定,并在说明本发明的具体实施例的过程中可以更容易地理解。

技术特征:

1.一种晶体管的制造方法,包括:

2.根据权利要求1所述的晶体管的制造方法,其特征在于,

3.根据权利要求2所述的晶体管的制造方法,其特征在于,所述沟槽构造形成为穿过所述外延层而贯通至所述基板的一部分。

4.根据权利要求1所述的晶体管的制造方法,其特征在于,

5.根据权利要求1所述的晶体管的制造方法,其特征在于,

6.根据权利要求1所述的晶体管的制造方法,其特征在于,

7.根据权利要求1所述的晶体管的制造方法,其特征在于,

8.根据权利要求1所述的晶体管的制造方法,其特征在于,

9.根据权利要求1所述的晶体管的制造方法,其特征在于,

10.根据权利要求1所述的晶体管的制造方法,其特征在于,

11.一种晶体管,包括:

12.根据权利要求11所述的晶体管,其特征在于,

13.根据权利要求11所述的晶体管,其特征在于,

14.根据权利要求12所述的晶体管,其特征在于,

15.根据权利要求11所述的晶体管,其特征在于,

16.根据权利要求15所述的晶体管,其特征在于,

17.根据权利要求11所述的晶体管,其特征在于,

18.根据权利要求11所述的晶体管,其特征在于,

19.根据权利要求11所述的晶体管,其特征在于,

20.根据权利要求11所述的晶体管,其特征在于,

21.根据权利要求11所述的晶体管,其特征在于,

22.根据权利要求11所述的晶体管,其特征在于,

技术总结

本发明涉及一种晶体管,包括:配置在上方形成有外延层的基板的步骤;以使所述外延层的一部分区域暴露的方式形成绝缘层的步骤;在所述外延层形成贯通从所述绝缘层暴露的一部分区域的插塞的步骤;在所述插塞及所述暴露的外延层上部形成导电层的步骤;在所述基板以使所述插塞的下表面暴露的方式形成通孔的步骤;以及形成覆盖所述基板的下部的金属层的步骤。

技术研发人员:李相玟

受保护的技术使用者:瓦威士有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!