在硅衬底中具有后侧沟道和分离沟道的硅基氮化镓半导体构件以及用于其制造的方法与流程

背景技术:

1、基于氮化镓(gan)的晶体管提供如下可能性:与基于硅或碳化硅的同类的构件相比,可以实现在同时更高的击穿电压的情况下具有更低的导通电阻的构件。

2、氮化镓晶体管主要通过所谓的高电子迁移率晶体管(hemts)是已知的,在所述高电子迁移率晶体管中电流通过构成晶体管通道的二维电子气横向地在衬底上侧发生。这样的横向的构件可以通过在硅晶片上的功能性的氮化镓层的异质外延制造。然而,对于在低的单位面积的导通电阻的情况下的高击穿电压而言,垂直的构件在结构尺寸和在构件内的电场分布方面都是有利的,在所述构件中电流从衬底前侧流向衬底后侧。这种构件是不可直接借助硅(si)上的异质外延的氮化镓层实现的(darstellbar),因为为了匹配氮化镓和硅之间的晶格失配(gitterfehlpass)以及为了减小衬底曲率需要绝缘的中间层(所谓的缓冲器)。

3、缓冲器自身如此机械地张开,使得所述缓冲器在室温情况下恰好补偿氮化镓层的张力。然而,因为缓冲器是绝缘体,所以通过缓冲器从衬底前侧至衬底后侧的电流被阻止。

4、原生氮化镓衬底也是已知的,在所述氮化镓衬底上,构件的需要的附加的外延的氮化镓层可以生长,而不需要绝缘的缓冲器。然而,这种氮化镓衬底小(典型地50mm直径)且贵。

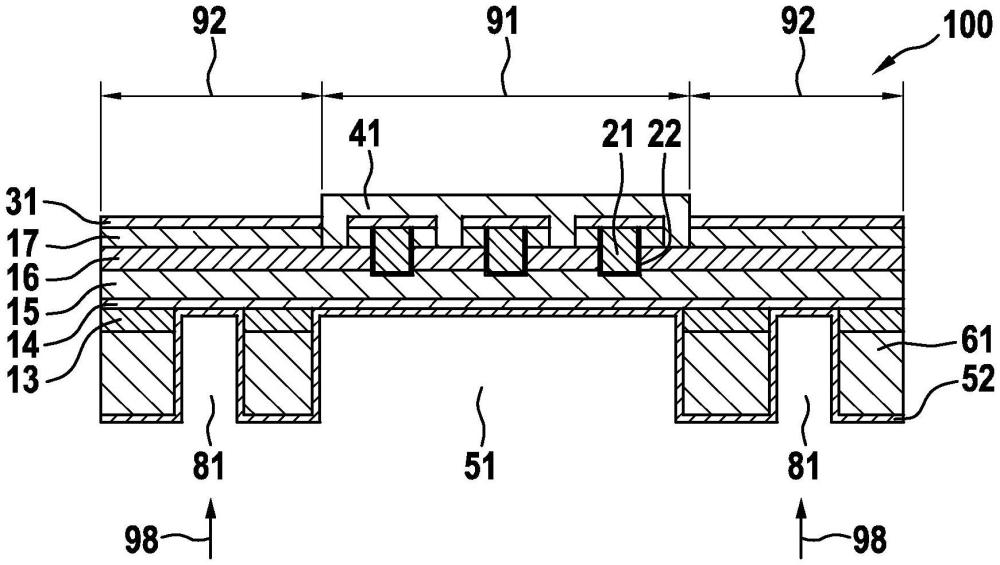

5、为了降低单位面积的晶体管价格,可以有利的是,在大的硅衬底上使用可供使用的异质外延的氮化镓层。对此,垂直的构件(沟槽mosfet、pn二极管)是已知的,在所述构件中硅衬底以及构件下的绝缘缓冲器被选择性地去除,后侧沟道(后侧沟槽)由此构造,以便可以直接地接触构件的漂移区(driftzone)的后侧。图1示出这样的具有绝缘缓冲器和后侧沟槽(在这里根据沟槽mosfets)的构件1的原理结构。以下,后侧沟槽也可以称为后侧腔(rückseitenkaverne)或后侧孔径(rückseitenapertur)。

6、如在图1中示出的那样,在硅衬底61上或一般地在载体衬底上以下iii-v氮化物半导体层(gan,缓冲器例外)外延地生长:绝缘缓冲器层13、具有n传导性的高掺杂的接触半导体层14、具有n传导性的低掺杂的漂移层15、具有p传导性的主体(body)层16和具有n传导性的高掺杂的源极接触层17。

7、源极接触层17以及主体层16由沟道(trench,沟槽)穿透,所述沟道的侧壁和底部通过栅极电介质22与栅极电极21分开。源极接触层17和主体层16通过源极电极4接触,所述源极电极41通过绝缘层31与栅极电极21分开。在后侧,硅衬底61和缓冲器13通过后侧沟槽51去除,所述沟道51在具有n传导性的高掺杂的接触半导体层14中终止。该接触半导体层通过后侧的漏极电极52接触(ankontaktiert)。在运行中,通过在栅极电极21上施加栅极电压构成主体层16中的传导性的通道,通过所述通道实现从源极电极41至漏极电极52的电流。

8、在图1中为了简化示出具有三个单元(即三个重复出现的结构)的晶体管。在实际的晶体管中,典型地存在多个这样的单元(zelle),并且因此高效地并联连接。典型的有源面处于几平方毫米的范围内,剩余的gan层有几微米的厚度。漏极电极52可以由多个金属层组成。

9、图2a和图2b以示意性的横截面视图示出相关技术中通常的、用于将具有多个晶体管芯片的晶片分离成各个芯片的方法。图2a示出分离之前的晶体管芯片,图2b示出分离之后的晶体管芯片。晶体管芯片可以在分离之后从载体71上被取下,以便借助常用的构建技术和连接技术的方法被再加工。为此,在有源晶体管区域(例如,具有源极电极41和/或后侧沟槽51的区域)外的区域内前侧地安装有标记,即所谓的锯切槽72。如在图2a中示出的那样,这些标记可以是蚀刻,在所述蚀刻中绝缘层31的部分被去除。作为替代,还设置附加的层作为标记,例如以不与源极电极41电连接的金属化的方式。

10、锯切槽72的标记用作用于随后的锯切工艺或分离工艺的记号。对此,晶片61被施加在所谓的锯切膜71(英语dice tape或bluetape,切带或蓝带)上,所述锯切膜71在框架中张开。随后借助金刚石涂层的锯切片沿着锯切槽72分离晶片61,使得较宽的锯切道产生,并且随后将分离的芯片留在锯切膜71上,然后可以将所述芯片从锯切膜71上取下。在这样的锯切工艺中,也可以将相同的锯切道多次锯切直至不同的深度,或者也可以对于各种不同的深度使用各种不同的据切条。作为替代,芯片的分离传统地通过激光进行,其方法是,借助激光进行分开或者通过所谓的隐形切割工艺,在所述隐形切割工艺中借助激光产生一种目标断裂点,在所述断裂点上在随后的锯切膜71的横向膨胀时将芯片分成两半(entzweibrechen)。

11、锯切工艺或激光工艺是串行工艺,因为轨道必须依次地被切割/被写。然而,对于较大的晶片直径而言,工艺时间增加并且因此成本也会增加。

技术实现思路

1、本发明的优点

2、与此相对,具有根据权利要求1所述的特征的根据本发明的膜片半导体构件具有如下优点:降低膜片半导体构件的分离时的成本。直观地,用于分离膜片半导体构件要锯切的厚度通过外部区域内的第二后侧空腔被减少。因此,可以实现横向更窄的锯切道,由此可以损失更少的用于锯切的晶片面积,并且可以节省成本。

3、另外,膜片半导体构件实现了免锯切分离工艺。因此,膜片半导体构件的分离以安全、可靠和更快的方式被执行。例如,免锯切工艺可以基于通过横向的膨胀或对目标分开点的压力加载的断裂。

4、另外,借助膜片半导体构件可以减少或避免所谓的后侧崩裂(backside-chipping)。后侧崩裂是在传统的锯切工艺中出现的在晶片后侧上的锯切沟道的折断。

5、在从属权利要求中和说明书中,描述膜片半导体构件的方面的扩展方案和有利的构型。

技术特征:

1.一种膜片半导体构件(100),所述膜片半导体构件(100)具有外部区域(92)和膜区域(91),

2.根据权利要求1所述的膜片半导体构件(100),所述膜片半导体构件(100)还具有回填材料(53),所述回填材料(53)布置在所述第一后侧腔(51)中,其中,所述回填材料(53)是电传导性和热传导性的,其中,所述第二后侧腔(81)没有回填材料(53)。

3.根据权利要求1或2所述的膜片半导体构件(100),所述膜片半导体构件(100)还具有漏极电极(52),所述漏极电极(52)布置在所述第一后侧腔(51)和所述第二后侧腔(81)中。

4.根据权利要求1或2所述的膜片半导体构件(100),所述膜片半导体构件(100)还具有漏极电极(52),所述漏极电极(52)布置在所述第一后侧腔(51)中,其中,所述第二后侧腔(81)没有漏极电极(52)。

5.根据权利要求1至4中任一项所述的膜片半导体构件(100),其中,所述目标分开点(98)设置为没有金属。

6.根据权利要求1至5中任一项所述的膜片半导体构件(100),其中,所述目标分开点(98)还具有在所述第二后侧腔(81)上或其上方的一个或多个层(13、14、15、16、17、31),其中,所述一个层(13、14、15、16、17、31)或所述多个层(13、14、15、16、17、31)分别具有光学上透明或半透明的材料,或者由光学上透明或半透明的材料构成。

7.根据权利要求1至6中任一项所述的膜片半导体构件(100),其中,所述第二后侧腔(81)具有沟道或盲孔的形式,所述沟道或盲孔具有在所述衬底(61)中的侧壁,其中,所述侧壁具有波纹结构,优选具有周期性波纹图案。

8.根据权利要求1至7中任一项所述的膜片半导体构件(100),其中,所述第二后侧腔(81)没有锯切痕迹。

9.一种膜片半导体构件结构,所述膜片半导体构件结构具有:

10.一种用于制造具有外部区域(92)和膜区域(91)的膜片半导体构件(100)的方法,所述方法具有:

11.根据权利要求8的方法,

12.根据权利要求8所述的方法,

13.根据权利要求8所述的方法,

技术总结

本发明提供一种膜片半导体构件(100),所述膜片半导体构件(100)具有外部区域(92)和膜区域(91),其中,有源层(14‑17)在膜区域内使膜成形。衬底(61)的至少一部分布置在所述外部区域(92)内。所述衬底(61)如此结构化,使得在所述衬底(61)的所述膜区域(91)内设置后侧腔(51),所述后侧腔(51)暴露在膜片的后侧。所述后侧腔(51)没有衬底(61)。至少一个有源区域布置在所述膜区域(91)内,并且有源区域具有至少一个PN结。用于分离膜半导体构件的所述目标分开点(98)具有在所述衬底的外部区域(92)内的第二后侧腔。

技术研发人员:S·雷根斯布格尔,C·胡贝尔

受保护的技术使用者:罗伯特·博世有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!