堆叠集成电路的制作方法

本申请涉及堆叠集成电路。

背景技术:

1、最近,为了提高集成度而通过对接合在一起的多个芯片进行堆叠而形成堆叠集成电路。堆叠集成电路中所包括的多个芯片可以通过相应的通孔相互传输数据以及包括命令和地址的控制信号。

技术实现思路

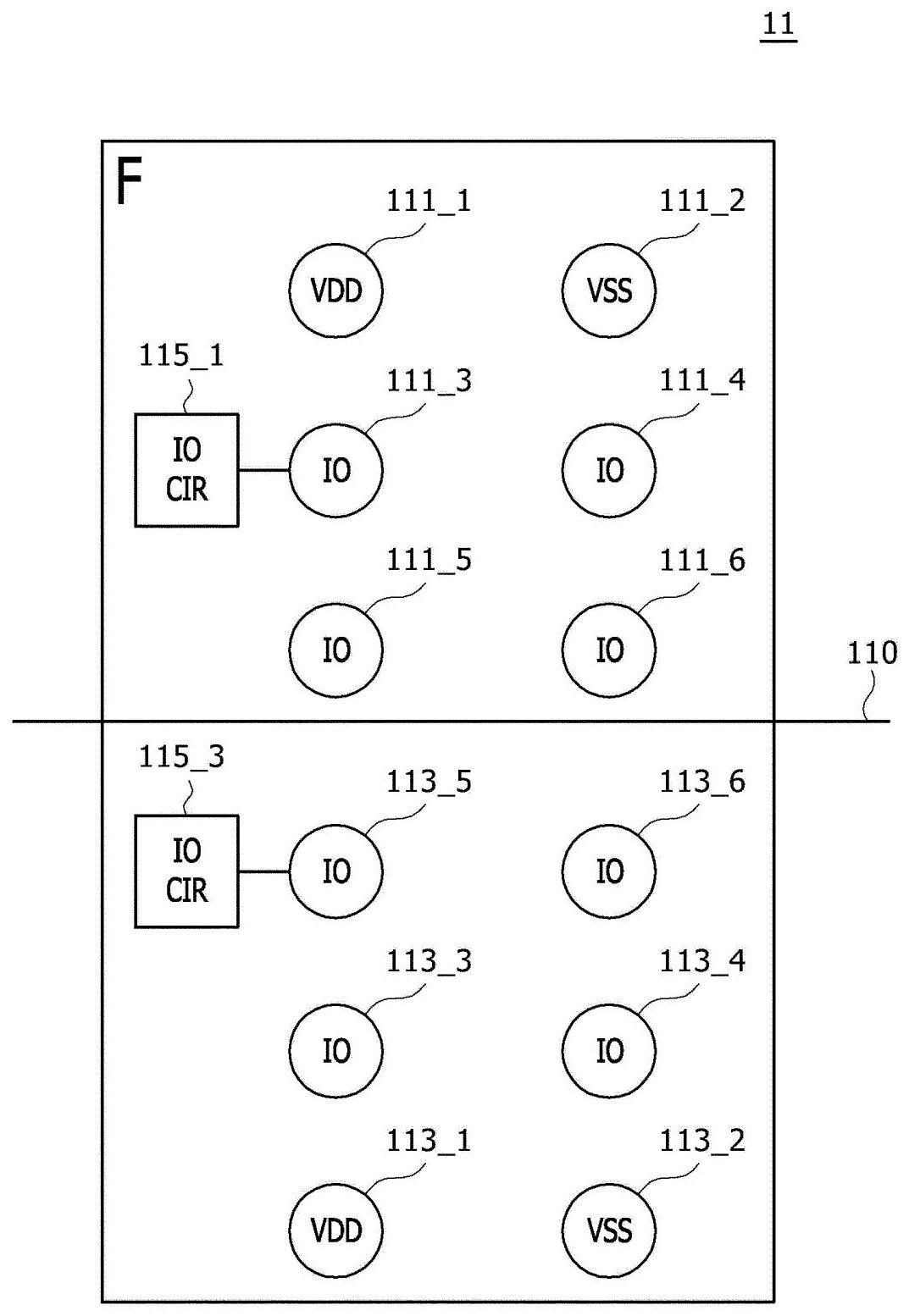

1、为此,本公开提供了一种堆叠集成电路,包括:第一芯片,其包括被设置为关于第一旋转轴线彼此对称的第一通孔集合和第二通孔集合以及包括被设置为关于所述第一旋转轴线彼此不对称的第一输入及输出(io)电路和第二io电路;以及第二芯片,其包括被设置为关于第二旋转轴线彼此对称的第三通孔集合和第四通孔集合以及包括被设置为关于所述第二旋转轴线彼此不对称的第三io电路和第四io电路。所述第二芯片绕着所述第二旋转轴线旋转并且堆叠在所述第一芯片上。

2、此外,本公开提供了一种堆叠集成电路,包括:第一芯片,其包括被连接至第一前焊盘的第一通孔和被连接至第二前焊盘的第二通孔并且包括被连接至所述第一前焊盘的第一输入及输出(io)电路;以及第二芯片,其包括被连接至第三前焊盘的第三通孔和被连接至第四前焊盘的第四通孔并且包括被连接至所述第四前焊盘的第二io电路,所述第一芯片和所述第二芯片通过将所述第一前焊盘与所述第三前焊盘接合以及将所述第二前焊盘与所述第四前焊盘接合而被接合在一起。

3、此外,本公开提供了一种堆叠集成电路,包括:第一芯片,其包括被设置为关于第一旋转轴线彼此对称的第一通孔和第二通孔并且包括被连接至与所述第一通孔连接的第一前焊盘的第一输入及输出(io)电路;以及第二芯片,其包括被设置为关于第二旋转轴线彼此对称的第三通孔和第四通孔并且包括被连接至与所述第三通孔连接的第二前焊盘的第二io电路。所述第二芯片绕着所述第二旋转轴线旋转并且堆叠在所述第一芯片上。

4、此外,本公开提供了一种堆叠集成电路,包括:第一芯片,其包括被连接至第一前焊盘的第一通孔、被连接至第二前焊盘的第二通孔和被连接至所述第一前焊盘的第一输入及输出(io)电路;以及第二芯片,其包括被连接至第三前焊盘的第三通孔、被连接至第四前焊盘的第四通孔和被连接至所述第四前焊盘的第二io电路。所述第一通孔和所述第二通孔被设置为基于旋转轴线彼此对称,所述第三通孔和所述第四通孔被设置为基于所述旋转轴线彼此对称,所述第一前焊盘与所述第三前焊盘接合在一起,以及所述第二前焊盘与所述第四前焊盘接合在一起。

5、此外,本公开提供了一种堆叠集成电路,包括:第一接合芯片,其通过对包括第一输入及输出(io)电路的第一芯片和包括第二io电路的第二芯片进行堆叠而形成;虚设芯片,其堆叠在所述第一接合芯片上;以及第二接合芯片,其堆叠在所述虚设芯片上并且通过对包括第三io电路的第三芯片和包括第四io电路的第四芯片进行堆叠而形成。所述虚设芯片包括虚设通孔集合、第一虚设焊盘集合和第二虚设焊盘集合,对所述虚设通孔集合、所述第一虚设焊盘集合和所述第二虚设焊盘集合中的每一个进行连接,以使得所述第一io电路、所述第二io电路、所述第三io电路和所述第四io电路中的每一个被分配至单独的通道。

6、此外,本公开提供了一种堆叠集成电路,包括:第一芯片,其包括第一前焊盘集合、第一通孔集合、第一后焊盘集合和第一输入及输出(io)电路;第二芯片,其堆叠在所述第一芯片上并且包括第二io电路;第三芯片,其堆叠在所述第二芯片上并且包括第三io电路;以及第四芯片,其堆叠在所述第三芯片上并且包括第四io电路。所述第二芯片包括第二前焊盘集合、第二通孔集合和第二后焊盘集合,对所述第二前焊盘集合、所述第二通孔集合和所述第二后焊盘集合中的每一个进行连接,以使得所述第一io电路、所述第二io电路、所述第三io电路和所述第四io电路中的每一个被分配至单独的通道。

7、此外,本公开提供了一种堆叠集成电路,包括:芯片标志模块,其被配置为基于源标志产生包括与芯片是下芯片还是上芯片有关的信息的芯片标志;以及输出控制模块,其被配置为基于所述芯片标志在不同的路径中产生芯片id,并且被配置为基于所述芯片id、选择id和读取控制信号产生输出控制信号以控制芯片数据的输出。

8、此外,本公开提供了一种堆叠集成电路,包括:第一芯片,其包括第一前焊盘集合和第一后焊盘集合,并且还包括第一芯片id产生电路,所述第一芯片id产生电路被配置为基于第一芯片标志在第一路径中产生第一芯片id;以及第二芯片,其包括第二前焊盘集合和第二后焊盘集合,并且还包括第二芯片id产生电路,所述第二芯片id产生电路被配置为基于第二芯片标志在第二路径中产生第二芯片id,所述第二芯片堆叠在所述第一芯片上并且通过将所述第一前焊盘集合与所述第二前焊盘集合接合而与第一芯片接合在一起。

技术特征:

1.一种堆叠集成电路,包括:

2.根据权利要求1所述的堆叠集成电路,其中,通过所述第一通孔集合、所述第二通孔集合、所述第三通孔集合和所述第四通孔集合的每个通孔来输入或输出数据或控制信号,供应电源电压或供应接地电压。

3.根据权利要求1所述的堆叠集成电路,其中:

4.根据权利要求3所述的堆叠集成电路,其中:

5.根据权利要求4所述的堆叠集成电路,其中:

6.根据权利要求5所述的堆叠集成电路,其中:

7.根据权利要求6所述的堆叠集成电路,其中:

8.一种堆叠集成电路,包括:

9.根据权利要求8所述的堆叠集成电路,其中:

10.根据权利要求8所述的堆叠集成电路,其中:

11.根据权利要求10所述的堆叠集成电路,其中:

12.根据权利要求11所述的堆叠集成电路,其中:

13.根据权利要求11所述的堆叠集成电路,其中:

14.根据权利要求8所述的堆叠集成电路,还包括:

15.根据权利要求14所述的堆叠集成电路,其中:

16.一种堆叠集成电路,包括:

17.根据权利要求16所述的堆叠集成电路,其中,通过所述第一通孔、所述第二通孔、所述第三通孔和所述第四通孔中的每个通孔输入和输出数据或控制信号。

18.根据权利要求16所述的堆叠集成电路,其中:

19.一种堆叠集成电路,包括:

20.根据权利要求19所述的堆叠集成电路,其中:

21.根据权利要求19所述的堆叠集成电路,还包括:

22.根据权利要求21所述的堆叠集成电路,其中:

23.一种堆叠集成电路,包括:

24.根据权利要求23所述的堆叠集成电路,其中,所述虚设通孔集合中的分别被连接至所述第一虚设焊盘集合的虚设焊盘的虚设通孔的配置与所述虚设通孔集合中分别被连接至所述第二虚设焊盘集合的虚设焊盘的虚设通孔的配置不同。

25.根据权利要求23所述的堆叠集成电路,其中:

26.根据权利要求23所述的堆叠集成电路,其中:

27.根据权利要求26所述的堆叠集成电路,其中:

28.根据权利要求26所述的堆叠集成电路,其中:

29.根据权利要求28所述的堆叠集成电路,其中:

30.根据权利要求29所述的堆叠集成电路,其中:

31.根据权利要求30所述的堆叠集成电路,其中:

32.根据权利要求30所述的堆叠集成电路,其中:

33.一种堆叠集成电路,包括:

34.根据权利要求33所述的堆叠集成电路,其中,所述第二通孔集合中的分别被连接至所述第二前焊盘集合的前焊盘的通孔的配置与所述第二通孔集合中的分别被连接至所述第二后焊盘集合的后焊盘的通孔的配置不同。

35.根据权利要求33所述的堆叠集成电路,其中:

36.根据权利要求33所述的堆叠集成电路,其中:

37.根据权利要求36所述的堆叠集成电路,其中:

38.根据权利要求37所述的堆叠集成电路,其中:

39.一种堆叠集成电路,包括:

40.根据权利要求39所述的堆叠集成电路,其中:

41.根据权利要求40所述的堆叠集成电路,其中:

42.根据权利要求39所述的堆叠集成电路,其中:

43.根据权利要求42所述的堆叠集成电路,其中,所述第一输出控制模块包括第一芯片id产生电路,所述第一芯片id产生电路基于第一芯片标志在第一路径中产生第一芯片id。

44.根据权利要求43所述的堆叠集成电路,其中,所述第一芯片id产生电路包括:

45.根据权利要求43所述的堆叠集成电路,其中,所述第一输出控制模块还包括第一输出控制信号产生电路,所述第一输出控制信号产生电路基于所述第一芯片id、所述选择id和所述读取控制信号产生第一输出控制信号以控制第一内部数据的输出。

46.根据权利要求45所述的堆叠集成电路,其中,所述第一输出控制信号产生电路在读取操作已经执行并且所述读取控制信号已经被激活的状态下产生所述第一输出控制信号,所述第一输出控制信号在所述第一芯片id与所述选择id彼此相同时被激活。

47.根据权利要求42所述的堆叠集成电路,其中,所述第二输出控制模块包括第二芯片id产生电路,所述第二芯片id产生电路基于第二芯片标志在第二路径中产生第二芯片id。

48.根据权利要求47所述的堆叠集成电路,其中,所述第二芯片id产生电路包括:

49.根据权利要求47所述的堆叠集成电路,其中,所述第二输出控制模块还包括第二输出控制信号产生电路,所述第二输出控制信号产生电路基于所述第二芯片id、选择id和读取控制信号产生第二输出控制信号以控制第二内部数据的输出。

50.根据权利要求49所述的堆叠集成电路,其中,所述第二输出控制信号产生电路在读取操作已经执行并且所述读取控制信号已经被激活的状态下产生所述第二输出控制信号,所述第二输出控制信号在所述第二芯片id与所述选择id彼此相同时被激活。

51.一种堆叠集成电路,包括:

52.根据权利要求51所述的堆叠集成电路,其中,所述第一芯片还包括第一芯片标志模块,所述第一芯片标志模块从源标志的反相信号产生所述第一芯片标志。

53.根据权利要求51所述的堆叠集成电路,其中,所述第二芯片还包括第二芯片标志模块,所述第二芯片标志模块从源标志产生所述第二芯片标志。

54.根据权利要求51所述的堆叠集成电路,其中,所述第一芯片id产生电路包括:

55.根据权利要求51所述的堆叠集成电路,其中,所述第一芯片还包括第一输出控制信号产生电路,所述第一输出控制信号产生电路基于所述第一芯片id、选择id和读取控制信号产生第一输出控制信号以控制第一内部数据的输出。

56.根据权利要求55所述的堆叠集成电路,其中,所述第一输出控制信号产生电路在读取操作已经执行并且所述读取控制信号已经被激活的状态下产生所述第一输出控制信号,所述第一输出控制信号在所述第一芯片id与所述选择id彼此相同时被激活。

57.根据权利要求51所述的堆叠集成电路,其中,所述第二芯片id产生电路包括:

58.根据权利要求51所述的堆叠集成电路,其中,所述第二芯片还包括第二输出控制信号产生电路,所述第二输出控制信号产生电路基于所述第二芯片id、选择id和读取控制信号产生第二输出控制信号以控制第二内部数据的输出。

59.根据权利要求58所述的堆叠集成电路,其中,所述第二输出控制信号产生电路在读取操作已经执行并且所述读取控制信号已经被激活的状态下产生所述第二输出控制信号,所述第二输出控制信号在所述第二芯片id与所述选择id彼此相同时被激活。

技术总结

本公开涉及一种堆叠集成电路。堆叠集成电路包括:第一芯片,其包括被设置为关于第一旋转轴线彼此对称的第一通孔集合和第二通孔集合并且包括被设置为关于第一旋转轴线彼此不对称的第一输入及输出(IO)电路和第二IO电路;以及第二芯片,其包括被设置为关于第二旋转轴线彼此对称的第三通孔集合和第四通孔集合并且包括被设置为关于第二旋转轴线彼此不对称的第三IO电路和第四IO电路,第二芯片绕着第二旋转轴线旋转并且堆叠在第一芯片上。

技术研发人员:李东郁,朴明宰,李昶权

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!