半导体结构及其制备方法与流程

本申请涉及集成电路,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、发光芯片是一种常用的发光器件。由于发光芯片可高效地将电能转化为光能,在现代社会具有广泛的用途,如照明、平板显示、医疗器件等领域。

2、随着生活水平的提高与科技的进步,对发光芯片以及使用发光芯片制备而成的显示面板的发光率、透光率、亮度等性能提出更高的要求。

技术实现思路

1、基于此,有必要针对发光芯片的发光率低的问题提供一种半导体结构及其制备方法。

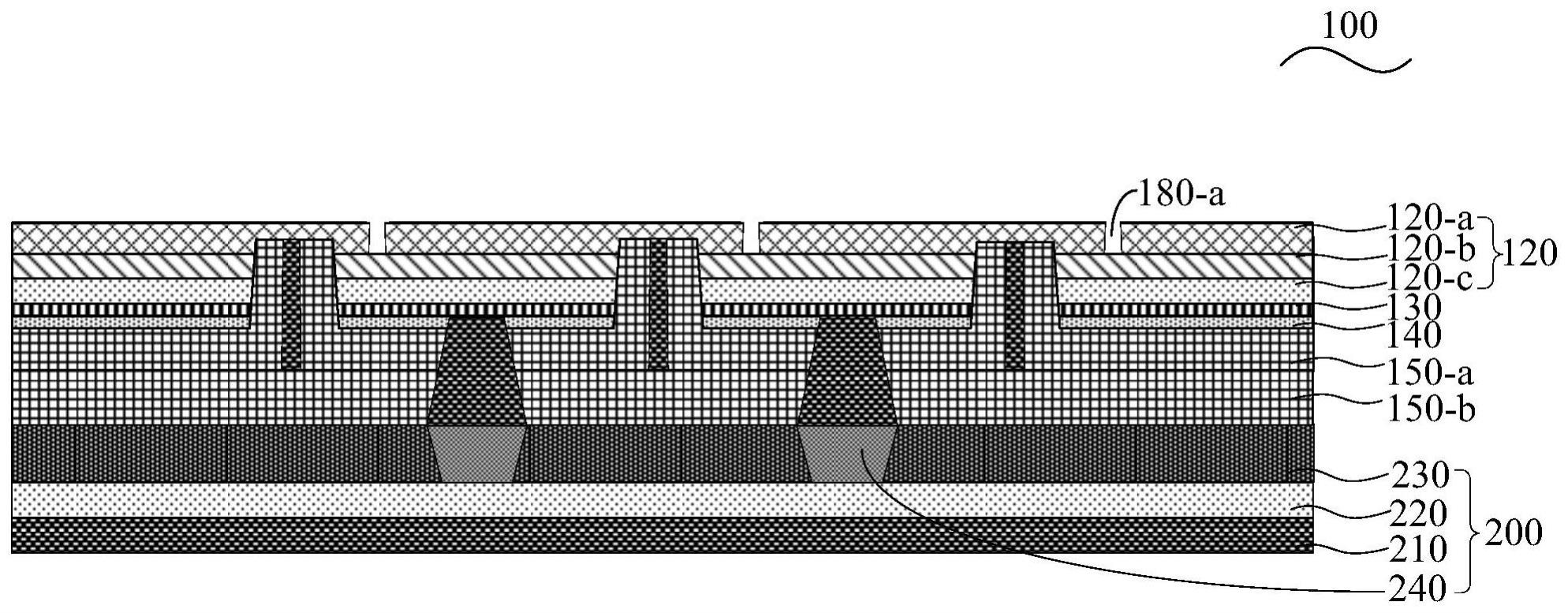

2、为了实现上述目的,一方面,本发明提供了一种半导体结构,包括:

3、外延层,包括n型半导体层、发光层、p型半导体层,且所述外延层具有台面结构,所述台面结构暴露所述n型半导体层;

4、第一介质层,覆盖所述外延层;

5、第一电极,位于所述第一介质层中,自所述第一介质层远离所述n型半导体层的表面延伸至所述n型半导体层;

6、第二介质层,覆盖所述第一介质层以及所述第一电极上;

7、第二电极,由所述第二介质层远离所述第一介质层的表面延伸至所述p型半导体层;

8、驱动基板,与所述第二介质层以及所述第二电极键合;

9、分隔通孔,至少贯穿所述n型半导体层,用于分隔所述外延层而形成多个发光芯片。

10、在其中一个实施例中,所述半导体结构包括:

11、反射层,填充于所述分隔通孔内。

12、在其中一个实施例中,所述半导体结构包括:

13、连通电极,位于相邻所述第一电极之间,且所述连通电极的深度小于所述第一电极的深度。

14、在其中一个实施例中,所述连通电极的底部高于所述p型半导体层。

15、在其中一个实施例中,所述半导体结构包括:

16、电流扩散层,位于所述p型半导体层上;

17、刻蚀阻挡层,位于所述电流扩散层上。

18、本发明还提供了一种半导体结构的制备方法,包括:

19、提供芯片衬底;

20、于所述芯片衬底上形成外延层;其中,所述外延层包括n型半导体层、发光层、p型半导体层;所述外延层具有台面结构,所述台面结构暴露所述n型半导体层;

21、形成覆盖所述外延层的第一介质层,所述第一介质层内具有延伸至所述n型半导体层的第一沟槽,并填充所述第一沟槽,形成第一电极;

22、于所述第一介质层远离所述芯片衬底的表面形成第二介质层,且相邻所述第一电极之间的所述第二介质层内具有延伸至所述p型半导体层的第二沟槽,并填充所述第二沟槽,形成第二电极;

23、提供驱动基板,并将所述第二介质层以及所述第二电极键合至所述驱动基板;

24、去除所述芯片衬底,并至少刻蚀所述n型半导体层,形成分隔通孔,所述分隔通孔用于分隔所述外延层而形成多个发光芯片。

25、在其中一个实施例中,去除所述芯片衬底,并刻蚀相邻所述第一电极之间的所述n型半导体层,形成分隔通孔与间隔设置的发光芯片,包括:

26、于所述分隔通孔内填充反射层。

27、在其中一个实施例中,刻蚀形成所述第一介质层内的第一沟槽的同时,还刻蚀形成位于相邻所述第一沟槽之间的所述第一介质层内的连通沟槽,所述连通沟槽的深度小于所述第一沟槽的深度;

28、填充所述第一沟槽,形成第一电极的同时,还填充所述连通沟槽,形成连通电极。

29、在其中一个实施例中,所述连通沟槽的底部高于所述p型半导体层。

30、在其中一个实施例中,于所述芯片衬底上形成外延层,包括:

31、于所述芯片衬底上依次形成n型半导体材料层、发光材料层、p型半导体材料层;

32、于所述p型半导体材料层上形成电流扩散材料层;

33、于所述电流扩散材料层上形成刻蚀阻挡材料层;

34、依次刻蚀所述刻蚀阻挡材料层、电流扩散材料层、p型半导体材料层、发光材料层以及n型半导体材料层,形成所述外延层。。

35、本发明的半导体构及其制备方法具有如下有益效果:

36、本发明的半导体结构以及制备方法,通过在第一介质层中设置第一电极,在第二介质层中设置第二电极,达到相邻发光芯片共用阳极,单独阴极的效果。此外,通过贯穿n型半导体层的分隔通孔,分隔外延层而形成多个发光芯片,增加了发光芯片的发光面积,进而增加了发光芯片发光率。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括:

3.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括:

4.根据权利要求3所述的半导体结构,其特征在于,所述连通电极的底部高于所述p型半导体层。

5.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括:

6.一种半导体结构的制备方法,其特征在于,包括:

7.根据权利要求6所述的半导体结构的制备方法,其特征在于,去除所述芯片衬底,并刻蚀相邻所述第一电极之间的所述n型半导体层,形成分隔通孔与间隔设置的发光芯片,包括:

8.根据权利要求6所述的半导体结构的制备方法,其特征在于,刻蚀形成所述第一介质层内的第一沟槽的同时,还刻蚀形成位于相邻所述第一沟槽之间的所述第一介质层内的连通沟槽,所述连通沟槽的深度小于所述第一沟槽的深度;

9.根据权利要求8所述的半导体结构的制备方法,其特征在于,所述连通沟槽的底部高于所述p型半导体层。

10.根据权利要求6所述的半导体结构的制备方法,其特征在于,于所述芯片衬底上形成外延层,包括:

技术总结

本发明涉及一种半导体结构及其制备方法,半导体结构包括:外延层,包括N型半导体层、发光层、P型半导体层,且所述外延层具有台面结构,所述台面结构暴露所述N型半导体层;第一介质层,覆盖所述外延层;第一电极,位于所述第一介质层中,自所述第一介质层远离所述N型半导体层的表面延伸至所述N型半导体层;第二介质层,覆盖所述第一介质层以及所述第一电极上;第二电极,由所述第二介质层远离所述第一介质层的表面延伸至所述P型半导体层;驱动基板,与所述第二介质层以及所述第二电极键合;分隔通孔,至少贯穿所述N型半导体层,用于分隔所述外延层而形成多个发光芯片。

技术研发人员:籍亚男,赵影

受保护的技术使用者:苏州市奥视微科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!