集成芯片及其形成方法与流程

本发明的实施例涉及集成芯片及其形成方法。

背景技术:

1、集成电路(integrated circuit,ic)形成在包含数百万或数十亿个晶体管元件的半导体裸片上。晶体管元件被配置为用作开关和/或产生功率增益以启用逻辑功能。ic还包括用于控制增益、时间常数和其他ic特性的无源元件。一种无源元件是金属-绝缘体-金属(mim)电容器。

技术实现思路

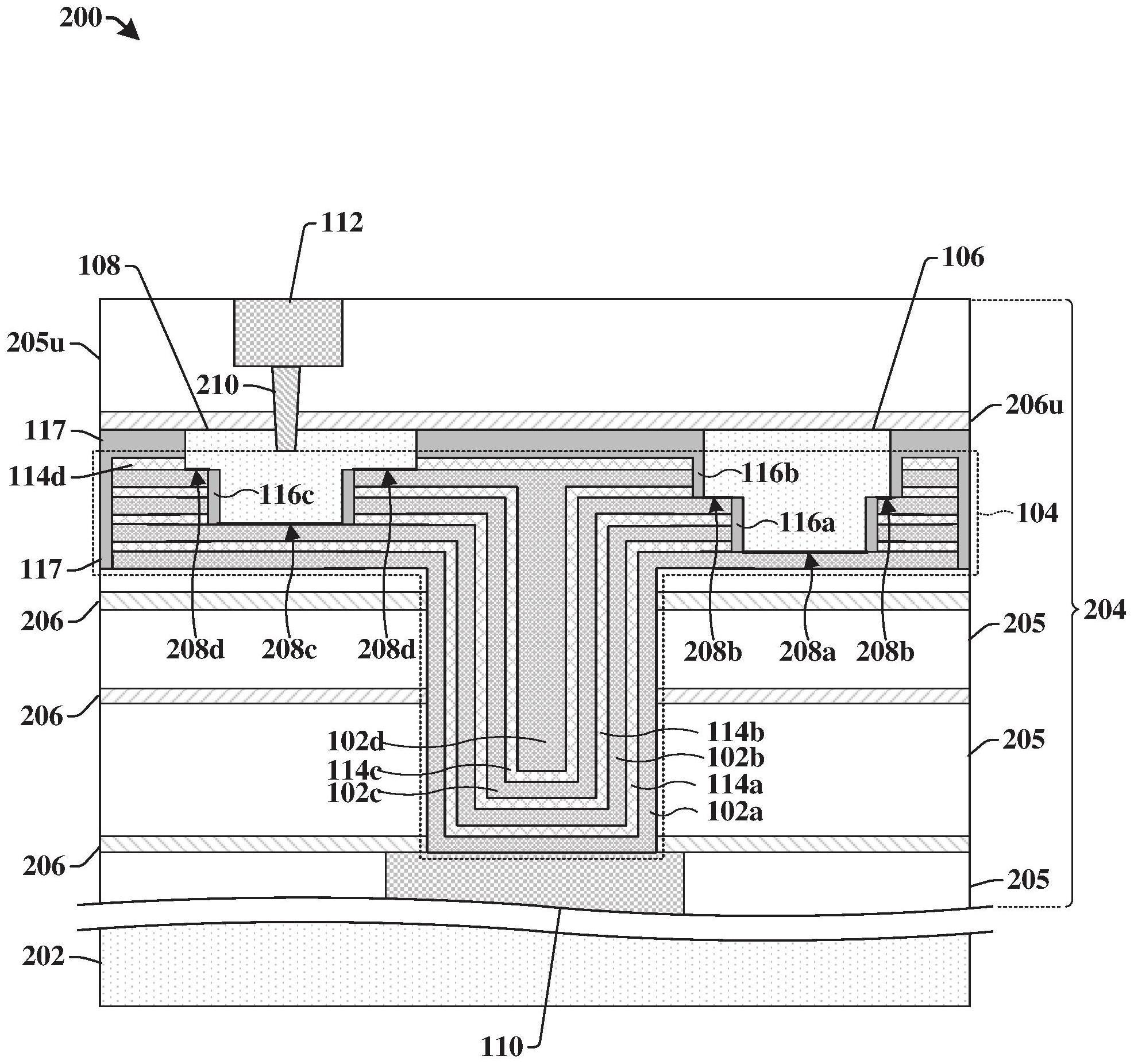

1、本发明实施例提供一种集成芯片,其包括金属-绝缘体-金属组件,且包括:多个导电板设置在衬底之上,并由多个电容器绝缘结构彼此隔开;第一导电插塞结构具有接触所述多个导电板中的第一导电板和第三导电板的多个下部表面;第一多个绝缘段沿着所述第一导电插塞结构的多个侧壁布置并且横向地将所述第一导电插塞结构的所述多个侧壁与所述多个导电板中的第二导电板和第四导电板隔开;第二导电插塞结构具有接触所述多个导电板中的所述第二导电板和所述第四导电板的多个下部表面;以及第二多个绝缘段沿所述第二导电插塞结构的多个侧壁布置,并将所述第二导电插塞结构的所述多个侧壁与所述第三导电板横向隔开。

2、本发明实施例提供一种集成芯片,其包括金属-绝缘体-金属组件,且包括:多个导电板彼此间隔;多个电容器绝缘结构,设置在所述多个导电板中的相邻导电板之间并且电隔离所述相邻导电板;第一导电插塞结构电耦合到所述多个导电板中的第一导电板和第三导电板,其中耦合到所述第一导电板的所述第一导电插塞结构的第一表面被耦合到所述第三导电板的所述第一导电插塞结构的第二表面横向包围;以及第二导电插塞结构电耦合到所述多个导电板中的第二导电板和第四导电板,其中耦合到所述第二导电板的所述第二导电插塞结构的第一表面被耦合到所述第四导电板的所述第二导电插塞结构的第二表面横向包围。

3、本发明实施例提供一种形成集成芯片的方法,包括:在第一电极之上形成多个导电板和多个电容器绝缘结构;蚀刻所述多个导电板和所述多个电容器绝缘结构中的一个或多个以在所述多个导电板和所述多个电容器绝缘结构中开出第一阶梯状插塞孔和第二阶梯状插塞孔;在所述多个导电板中的由所述第一阶梯状插塞孔和所述第二阶梯状插塞孔暴露出的多个内侧壁之上形成多个绝缘段;横跨所述第一阶梯状插塞孔和所述第二阶梯状插塞孔形成导电层;以及去除部分所述导电层的一部分以在所述第一二阶梯状插塞孔和所述第二阶梯状插塞孔内形成第一导电插塞结构和第二导电插塞结构。

技术特征:

1.一种集成芯片,包括金属-绝缘体-金属元件,包括:

2.根据权利要求1所述的集成芯片,其中所述第一多个绝缘段包括设置在所述第一导电插塞结构的相对侧上的多个第一绝缘段和多个第二绝缘段,并且所述第二多个绝缘段包括设置在所述第二导电插塞结构的相对侧上的多个第三绝缘段。

3.根据权利要求1所述的集成芯片,其中所述第一导电插塞结构在第一表面处电耦合到所述第一导电板并且在所述第一导电插塞结构的相对侧上的第二表面处电耦合到所述第三导电板,并且所述第二导电插塞结构在第三表面处电耦合到所述第二导电板并且在所述第二导电插塞结构的相对侧上的第四表面处电耦合到所述第四导电板。

4.根据权利要求1所述的集成芯片,其中所述多个导电板的最上面的导电板具有从一个角度看的“t”形,并且所述多个导电板中的其他导电板都衬在所述最上面的导电板的多个下部表面上。

5.根据权利要求1所述的集成芯片,其中,所述第一导电插塞结构具有在所述第一多个绝缘段及所述第二多个绝缘段的最上面的表面正上方延伸的最上面的下部表面。

6.根据权利要求1所述的集成芯片,其中,所述第二导电插塞结构包括沿具有多个上部表面的所述第一多个绝缘段向上延伸的导电膜,并且内连线耦合到所述导电膜的最下面的上部表面。

7.一种集成芯片,包括金属-绝缘体-金属元件,包括:

8.根据权利要求7所述的集成芯片,还包括多个绝缘段,将所述第一导电插塞结构与所述第二导电板和所述第四导电板以及所述第二导电插塞结构与所述第一导电板和所述第三导电板隔开并电绝缘。

9.根据权利要求7所述的集成芯片,其中所述第一导电插塞结构接触所述第一导电板和所述第三导电板的多个上部表面,并且其中所述第二导电插塞结构接触所述第二导电板和第四导电板的多个上部表面。

10.根据权利要求7所述的集成芯片,其中所述第一导电插塞结构的最上面的下部表面位于所述多个导电板的最上面的导电板正上方并与所述多个导电板的所述最上面的导电板隔开。

11.根据权利要求7所述的集成芯片,其中所述第二导电插塞结构的最底部表面位于所述第一导电板正上方并与所述第一导电板隔开,并且其中所述第二导电插塞结构的所述最底部表面位于所述第二导电板正上方并与所述第二导电板接触。

12.根据权利要求7所述的集成芯片,其中所述第一导电板完全低于所述第二导电插塞结构;以及

13.根据权利要求12所述的集成芯片,其中所述第二导电板、所述第三导电板和所述第四导电板直接在所述第一导电板的多个内侧壁之间。

14.根据权利要求7所述的集成芯片,其中所述多个电容器绝缘结构的厚度小于所述多个导电板的厚度的一半。

15.一种形成集成芯片的方法,包括:

16.根据权利要求15所述的形成集成芯片的方法,其中所述多个导电板和所述多个电容器绝缘结构形成“t”形,所述“t”形的底部耦合到所述第一电极。

17.根据权利要求15所述的形成集成芯片的方法,其中所述第一阶梯状插塞孔包括第一内侧壁和第二内侧壁,并且其中所述第二阶梯状插塞孔包括第三内侧壁,其中所述第一内侧壁和所述第二内侧壁是嵌套的。

18.根据权利要求15所述的形成集成芯片的方法,其中在所述多个内侧壁之上形成所述多个绝缘段还包括:

19.根据权利要求15所述的形成集成芯片的方法,还包括:

20.根据权利要求15所述的形成集成芯片的方法,还包括:

技术总结

在一些实施例中,本申请提供集成芯片(IC)。IC包括设置在衬底之上的金属‑绝缘体‑金属(MIM)元件。MIM元件包括彼此间隔开的多个导电板。MIM元件还包括电耦合到多个导电板中的第一导电板和第三导电板的第一导电插塞结构。第一多个绝缘段将第二导电板和第四导电板与第一导电插塞结构电隔离。MIM元件还包括电耦合到多个导电板中的第二导电板和第四导电板的第二导电插塞结构。第二多个绝缘段将第一导电板和第三导电板与第二导电插塞结构电隔离。

技术研发人员:周禄盛,曾宣翰,陈春元,曾晓晖,王俊智

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!