一种兼容增强型GaN基n沟道/p沟道器件集成结构的制作方法

本发明属于半导体器件,具体涉及一种兼容增强型gan基n沟道/p沟道器件集成结构。

背景技术:

1、近年来,随着增强型gan高电子迁移率晶体管(hemt)器件性能及可靠性的提升,gan hemt器件在高速数字电路中的应用研究也越来越广泛。目前,业界主要采用直接耦合场效应管逻辑(dcfl)或电阻晶体管逻辑(rtl)来实现gan数字电路的研制。然而,基于dcfl或rtl架构的gan数字电路芯片存在诸多不足。一是耗尽型gan器件或电阻在零压偏置条件下已处于导通状态,存在额外的静态功耗;二是电路的工作电压摆幅较小,需进行复杂的栅极驱动等电路的设计与配置,引入多余的寄生电感,影响系统工作频率特性的提升。因此,为充分发挥gan在数字电路中的优势,亟需开发兼容增强型gan基n沟道/p沟道器件的gancmos单片集成技术。

2、事实上,基于p-gan/algan/gan等材料结构,已有增强型n沟道/p沟道gan器件单片制备的相关报道。然而,单片集成工艺中增强型p沟道gan器件的制备需通过对p-gan层进行数十nm量级的精准刻蚀以实现,其中p-gan层的刻蚀深度不足将导致p沟道gan器件无法实现增强型,相反p-gan层刻蚀过深将导致增强型p沟道gan器件的输出电流特性大幅降低,严重影响gan cmos单片集成的电路匹配设计。在兼顾器件电学输出特性的同时,如何从结构上实质性提升增强型gan基n沟道/p沟道器件单片集成工艺的可控性与稳定性,简化工艺制程,是gan cmos技术真正迈向商业化应用的关键。

技术实现思路

1、解决的技术问题:针对上述技术问题,本发明提供了一种兼容增强型gan基n沟道/p沟道器件集成结构,其工艺制程可控性与均匀性高、器件电学输出特性稳定。

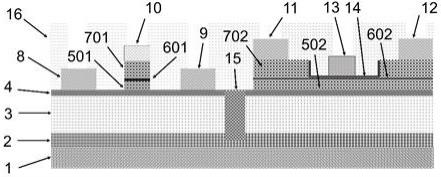

2、技术方案:一种兼容增强型gan基n沟道/p沟道器件集成结构,包括衬底、缓冲层、沟道层、势垒层、隔离区、n沟道区、p沟道区和钝化介质层,所述衬底、缓冲层、沟道层和势垒层自下而上依次设置,所述隔离区自势垒层的上表面延伸至缓冲层内部,所述n沟道区和p沟道区分别设于隔离区两侧;所述n沟道区包括设于势垒层的上方的第一源极、第一漏极和第一p-gan层,所述第一p-gan层自下而上依次包括第一下部p-gan层、第一插入层和第一上部p-gan层,且第一上部p-gan层的上方设有第一栅极,所述第一源极和第一漏极分别设于第一p-gan层的两侧;所述p沟道区包括第二源极、第二漏极、第二栅极和第二p-gan层,所述第二p-gan层设于势垒层的上方,自下而上依次包括第二下部p-gan层、第二插入层和第二上部p-gan层,且第二上部p-gan层的中部设有未覆盖第二插入层的中空区,所述第二栅极设于中空区上,且与第二插入层之间设有栅介质层,所述第二源极和第二漏极分别设于第二栅极两侧的第二上部p-gan层的上方;所述钝化介质层覆盖n沟道区、p沟道区和隔离区,且在第一源极、第一漏极、第一栅极、第二源极、第二漏极和第二栅极的对应位置开设有与外界进行电接触的窗口。

3、优选的,所述第一插入层、第二插入层均为含有al元素的iii-v族化合物半导体。

4、进一步的,所述第一插入层、第二插入层为aln、algan、inaln、inalgan中的一种或多种。

5、优选的,所述第一插入层、第二插入层的厚度均为1~10nm。

6、优选的,所述第一下部p-gan层和第二下部p-gan层的厚度均为20~50nm,mg掺杂浓度为1017~1019cm-3。

7、优选的,所述第一上部p-gan层和第二上部p-gan层的厚度均为50~100nm,mg掺杂浓度为1019~1021cm-3。

8、优选的,所述衬底为蓝宝石、sic、si、金刚石或gan中的一种。

9、优选的,所述缓冲层为gan、aln、algan中的一种或多种组成的单层或多层结构。

10、优选的,所述沟道层与所述势垒层的组合结构为gan/aln、gan/algan、algan/aln结构中的一种。

11、优选的,所述栅介质层为sio2、si3n4、al2o3、aln、hfo2中的一种或几种,厚度为5~20nm。

12、有益效果:本发明中含al组分插入层的引入,可以提升上部p-gan层与插入层之间的刻蚀选择比,有效解决增强型p沟道器件纳米量级深度的栅极刻蚀工艺稳定性与一致性差的问题,提升gan cmos单片集成工艺的可控性与均匀性;

13、刻蚀损伤问题是制约gan器件性能提升的关键因素,含al组分插入层的引入可以有效阻挡刻蚀工艺对下部p-gan层的损伤,降低下部p-gan层的表面粗糙度,提升单片集成的p沟道gan器件的电学输出特性;

14、本发明提出的结构与现有基于p-gan帽层栅技术的增强型n沟道gan器件工艺高度兼容,易于实现多功能gan cmos单片逻辑电路的制备。

技术特征:

1.一种兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,包括衬底(1)、缓冲层(2)、沟道层(3)、势垒层(4)、隔离区(15)、n沟道区、p沟道区和钝化介质层(16),所述衬底(1)、缓冲层(2)、沟道层(3)和势垒层(4)自下而上依次设置,所述隔离区(15)自势垒层(4)的上表面延伸至缓冲层(2)内部,所述n沟道区和p沟道区分别设于隔离区(15)两侧;所述n沟道区包括设于势垒层(4)的上方的第一源极(8)、第一漏极(9)和第一p-gan层,所述第一p-gan层自下而上依次包括第一下部p-gan层(501)、第一插入层(601)和第一上部p-gan层(701),且第一上部p-gan层(701)的上方设有第一栅极(10),所述第一源极(8)和第一漏极(9)分别设于第一p-gan层的两侧;所述p沟道区包括第二源极(11)、第二漏极(12)、第二栅极(13)和第二p-gan层,所述第二p-gan层设于势垒层(4)的上方,自下而上依次包括第二下部p-gan层(502)、第二插入层(602)和第二上部p-gan层(702),且第二上部p-gan层(702)的中部设有未覆盖第二插入层(602)的中空区,所述第二栅极(13)设于中空区上,且与第二插入层(602)之间设有栅介质层(14),所述第二源极(11)和第二漏极(12)分别设于第二栅极(13)两侧的第二上部p-gan层(702)的上方;所述钝化介质层(16)覆盖n沟道区、p沟道区和隔离区(15),且在第一源极(8)、第一漏极(9)、第一栅极(10)、第二源极(11)、第二漏极(12)和第二栅极(13)的对应位置开设有与外界进行电接触的窗口。

2.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述第一插入层(601)、第二插入层(602)均为含有al元素的iii-v族化合物半导体。

3.根据权利要求1或2所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述第一插入层(601)、第二插入层(602)为aln、algan、inaln、inalgan中的一种或多种。

4.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述第一插入层(601)、第二插入层(602)的厚度均为1~10nm。

5.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述第一下部p-gan层(501)和第二下部p-gan层(502)的厚度均为20~50nm,mg掺杂浓度为1017~1019 cm-3。

6.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述第一上部p-gan层(701)和第二上部p-gan层(702)的厚度均为50~100nm,mg掺杂浓度为1019~1021 cm-3。

7.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述衬底(1)为蓝宝石、sic、si、金刚石或gan中的一种。

8.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述缓冲层(2)为gan、aln、algan中的一种或多种组成的单层或多层结构。

9.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述沟道层(3)与所述势垒层(4)的组合结构为gan/aln、gan/algan、algan/aln结构中的一种。

10.根据权利要求1所述的兼容增强型gan基n沟道/p沟道器件集成结构,其特征在于,所述栅介质层(14)为sio2、si3n4、al2o3、aln、hfo2中的一种或几种,厚度为5~20nm。

技术总结

本发明公开了一种兼容增强型GaN基n沟道/p沟道器件集成结构,其隔离区自势垒层的上表面延伸至缓冲层内部,n沟道区和p沟道区分别设于隔离区两侧;n沟道区的第一p‑GaN层自下而上依次包括第一下部p‑GaN层、第一插入层和第一上部p‑GaN层;p沟道区的第二p‑GaN层自下而上依次包括第二下部p‑GaN层、第二插入层和第二上部p‑GaN层,且第二上部p‑GaN层的中部设有未覆盖第二插入层的中空区,所述第二栅极设于中空区上,且与第二插入层之间设有栅介质层。本发明工艺制程可控性与均匀性高、器件电学输出特性稳定、与现有增强型n沟道GaN器件工艺兼容度高。

技术研发人员:王登贵,周建军,胡壮壮,张凯,孔月婵,陈堂胜

受保护的技术使用者:中国电子科技集团公司第五十五研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!