3D存储器及其制造方法、电子设备与流程

本申请涉及但不限于半导体技术,尤指一种3d存储器及其制造方法、电子设备。

背景技术:

1、近些年,3d结构的存储器受到越来越多的关注,在提高存储器的密度具有一定优势。当前,以具有可沉积在任意材料表面特性和高开关比特性的金属氧化物,比如铟镓锌氧化物(indium gallium zinc oxide,igzo)作为沟道的半导体存储器件受到业界关注。在存储器领域,为了提高存储单元的密度,可以将该金属氧化物半导体晶体管用于存储单元的3d堆叠结构。

2、目前越来越多地关注3d器件的设计结构在产业上制作的便利性以及存储密度上的优势等。

技术实现思路

1、以下是对本文详细描述的主题的概述。本概述并非是为了限制本申请的保护范围。

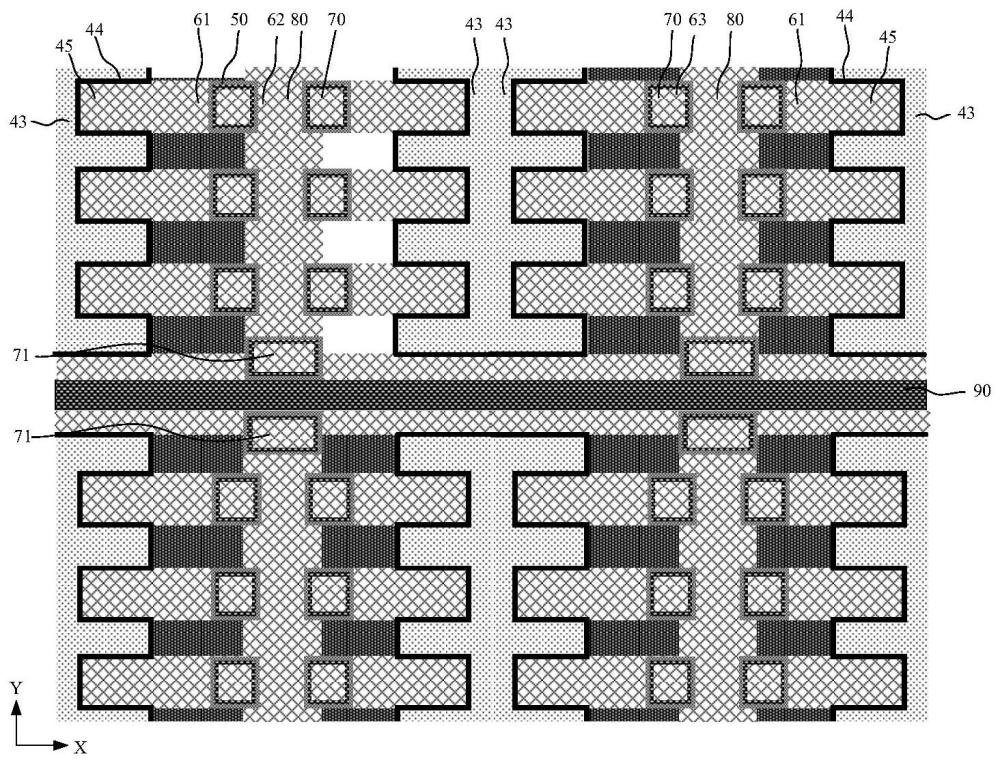

2、在一个方面,本申请的示例性实施方式提供了一种3d存储器,包括多层沿垂直于衬底的方向堆叠的存储区和多条字线,其中所述字线沿着垂直于所述衬底的方向延伸且贯穿不同层的所述存储区,每一层存储区包括:

3、第一公共位线,其沿着垂直于所述字线的第一方向延伸;

4、至少两个存储单元阵列,其设置在所述第一公共位线的两侧,每个存储单元阵列包括:

5、多条沿着第二方向延伸的第二公共位线,所述第二方向与所述第一方向垂直且与所述字线垂直;

6、至少两列存储单元,每列存储单元沿着所述第二方向延伸且连接到一条所述第二公共位线;每列存储单元包括多个存储单元,每个存储单元包括晶体管,所述晶体管包括第一电极和第二电极,所述第一电极和所述第二电极之间的沟道为水平沟道,每个所述晶体管的所述第二电极在所述第一方向上与所述第二公共位线电连接;

7、多个选通晶体管,与各存储单元阵列的各第二公共位线一一对应,每个选通晶体管设置在所述第一公共位线与一条对应的第二公共位线之间并与所述第一公共位线和所述第二公共位线连接。

8、在示例性的实施方式中,所述晶体管还包括沿垂直于所述衬底的方向延伸的栅电极、环绕所述栅电极的侧壁的半导体层以及设置在所述栅电极与所述半导体层之间的栅极绝缘层;晶体管的所述栅电极为所述字线的一部分。

9、在示例性的实施方式中,每个存储单元还包括电容,所述电容包括第一极板和第二极板,每个存储单元的所述电容的所述第一极板与所述晶体管的所述第一电极电连接;每个电容的所述第二极板沿着所述第二方向相连接。

10、在示例性的实施方式中,所述第一极板与所述第一电极为一体式结构。

11、在示例性的实施方式中,多层存储区的多条所述第一公共位线在垂直于所述衬底的方向上呈台阶状分布。

12、在另一方面,本申请的示例性实施方式提供了一种3d存储器的制造方法,所述3d存储器包括多层沿垂直于衬底的方向堆叠的存储区和字线,所述3d存储器的制造方法包括:

13、提供衬底,在所述衬底上依次交替沉积绝缘薄膜和导电薄膜形成叠层结构;

14、对所述叠层结构构图形成包括沿着垂直于所述字线的第一方向延伸的第一子叠层结构、沿着与所述第一方向垂直且与所述字线垂直的第二方向延伸的第二子叠层结构的叠层结构以及与第一子叠层结构平行且被第二子叠层结构隔开的第一子部和第二子部;

15、所述第一子叠层结构形成第一公共位线;

16、所述第二子叠层结构形成第二公共位线;

17、形成在垂直于所述衬底的方向上贯穿所述叠层结构的第一通孔、第二通孔以及第三通孔;

18、在所述第一通孔和所述第二通孔的侧壁依次沉积半导体薄膜和栅绝缘薄膜形成多层所述晶体管的环形的半导体层和栅极绝缘层,在所述半导体层沿所述第一方向的两侧形成第一电极和第二电极,同一个晶体管中所述第一电极和所述第二电极之间的沟道为水平沟道;

19、在所述第一通孔和所述第二通孔内沉积栅电极薄膜形成多层所述晶体管的栅电极,不同层的所述晶体管的所述栅电极为所述字线的一部分;

20、在所述第三通孔的侧壁依次沉积半导体薄膜、栅绝缘薄膜以及栅电极薄膜形成选通晶体管,所述选通晶体管与所述第一公共位线和所述第二公共位线电连接。

21、在示例性的实施方式中,所述第一通孔在所述衬底上的正投影与所述第一子部在所述衬底上的正投影和第二公共位线在所述衬底上的正投影至少部分交叠;所述第二通孔在所述衬底上的正投影与所述第二子部在所述衬底上的正投影和第二公共位线在所述衬底上的正投影至少部分交叠以及所述第三通孔在所述衬底上的正投影与所述第一公共位线在所述衬底上的正投影和第二公共位线在所述衬底上的正投影至少部分交叠。

22、在示例性的实施方式中,所述第一子叠层结构形成第一公共位线还包括将多条所述第一公共位线设置成不同的长度,使得多层存储区的多条所述第一公共位线在垂直于所述衬底的方向上呈台阶状分布。

23、在示例性的实施方式中,在所述第一子部靠近所述第一电极的一侧形成电容的第一极板;在所述第一子部远离所述第一电极的一侧形成电容的第二极板;在所述第二子部靠近所述第一电极的一侧形成电容的第一极板;在所述第二子部远离所述第一电极的一侧形成电容的第二极板。

24、在又一方面,本申请的示例性实施方式提供了一种电子设备,包括上述任一项所述的3d存储器。

25、在示例性的实施方式中,上述电子设备包括存储装置、智能电话、计算机、平板电脑、人工智能设备、可穿戴设备或移动电源。

26、本申请通过在同层设置一条第一公共位线和多条第二公共位线,每一条第二公共位线通过各自对应的选通晶体管连接到同层的第一公共位线。读写操作时,打开一条位线,可以同时打开对应的选通晶体管并关闭其他的选通晶体管;同时通过与每个选通晶体管相连来开启第一公共位线,从而减小寄生电容,提高了读取速度。

27、本申请的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本申请而了解。本申请的其他优点可通过在说明书以及附图中所描述的方案来实现和获得。

技术特征:

1.一种3d存储器,其特征在于,包括多层沿垂直于衬底的方向堆叠的存储区和多条字线,其中所述字线沿着垂直于所述衬底的方向延伸且贯穿不同层的所述存储区,每一层存储区包括:

2.根据权利要求1所述的3d存储器,其特征在于,所述晶体管还包括沿垂直于所述衬底的方向延伸的栅电极、环绕所述栅电极的侧壁的半导体层以及设置在所述栅电极与所述半导体层之间的栅极绝缘层;所述晶体管的所述栅电极为所述字线的一部分。

3.根据权利要求1所述的3d存储器,其特征在于,每个存储单元还包括电容,所述电容包括第一极板和第二极板,每个存储单元的所述电容的所述第一极板与所述晶体管的所述第一电极电连接;每个电容的所述第二极板沿着所述第二方向相连接。

4.根据权利要求3所述的3d存储器,其特征在于,所述第一极板与所述第一电极为一体式结构。

5.根据权利要求1所述的3d存储器,其特征在于,多层存储区的多条所述第一公共位线在垂直于所述衬底的方向上呈台阶状分布。

6.一种3d存储器的制造方法,其特征在于,所述3d存储器包括:多层沿垂直于衬底的方向堆叠的存储区和字线,所述3d存储器的制造方法包括:

7.根据权利要求6所述的制造方法,其特征在于,形成在垂直于所述衬底的方向上贯穿所述叠层结构的第一通孔、第二通孔以及第三通孔的步骤包括形成第一通孔,使所述第一通孔在所述衬底上的正投影与所述第一子部在所述衬底上的正投影和第二公共位线在所述衬底上的正投影至少部分交叠;形成第二通孔,使所述第二通孔在所述衬底上的正投影与所述第二子部在所述衬底上的正投影和第二公共位线在所述衬底上的正投影至少部分交叠以及形成第三通孔,所述第三通孔在所述衬底上的正投影与所述第一公共位线在所述衬底上的正投影和第二公共位线在所述衬底上的正投影至少部分交叠。

8.根据权利要求6所述的制造方法,其特征在于,所述第一子叠层结构形成第一公共位线还包括将多条所述第一公共位线设置成不同的长度,使得多层存储区的多条所述第一公共位线在垂直于所述衬底的方向上呈台阶状分布。

9.一种电子设备,其特征在于,包括根据权利要求1-5中任一项所述的3d存储器。

10.根据权利要求9所述的电子设备,其特征在于,所述电子设备包括存储装置、智能电话、计算机、平板电脑、人工智能设备、可穿戴设备或移动电源。

技术总结

本申请提供了一种3D存储器及其制造方法,电子设备。该3D存储器包括多层沿垂直于衬底的方向堆叠的存储区和字线;每一层存储区包括沿第一方向延伸的第一公共位线,至少两列存储单元以及设置在第一公共位线与每个存储单元阵列中的沿第二方向延伸的各条第二公共位线之间的多个选通晶体管,每个选通晶体管与第一公共位线和第二公共位线连接。本申请通过在位于同一层的每相邻两个存储单元阵列之间设置一条第一公共位线且每个存储单元阵列中沿与第一公共位线垂直的方向设置多条第二公共位线,使得相邻两列存储单元之间的第二公共位线通过对应的选通晶体管连接到同层的第一公共位线,从而减小线与线之间的寄生电容,提高了读取速度,提升了存储单元密度。

技术研发人员:宋艳鹏,戴瑾,王祥升,王海玲,王桂磊,赵超

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!