半导体器件及其形成方法与流程

本申请的实施例涉及半导体器件及其形成方法。

背景技术:

1、自集成电路(ic)的发展以来,由于各种电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度不断改进,半导体工业经历了持续的快速增长。在大多数情况下,集成密度的这些改进来自于最小部件尺寸的反复减小,这允许将更多组件集成到给定区域中。随着对小型化、更高速度、更大带宽以及更低功耗和延迟的需求的增长,对封装半导体管芯的更小和更具创造性的技术的需求也增长。

2、堆叠的半导体器件已经作为进一步减小半导体器件的物理尺寸的有效技术出现。在堆叠的半导体器件中,在不同的半导体晶圆上制造有源电路,诸如逻辑电路和存储器电路。两个或多个半导体晶圆可以通过合适的接合技术接合在一起,以进一步减小半导体器件的形状因数。

技术实现思路

1、根据本申请的一个实施例,提供了一种半导体器件,包括:介电层,位于半导体衬底的有源表面上方;导电通孔,位于介电层中,导电通孔包括具有非均匀晶粒取向的第一铜层;以及接合焊盘,位于导电通孔上方和介电层中,接合焊盘包括具有均匀晶粒取向的第二铜层,接合焊盘的顶面与介电层的顶面共面。

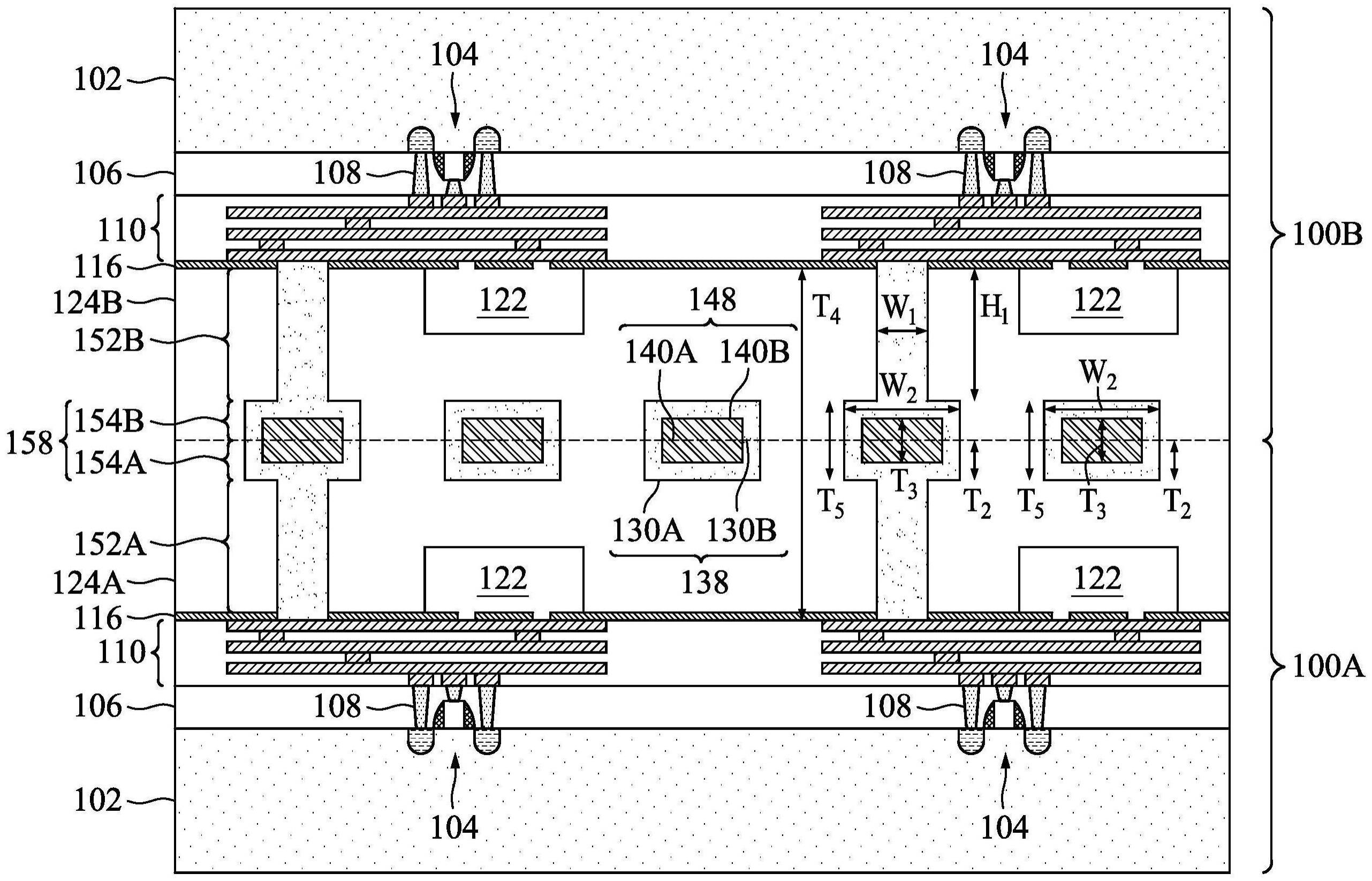

2、根据本申请的另一个实施例,提供了一种半导体器件,包括:第一集成电路管芯。第一集成电路管芯包括:第一介电层;和第一接合焊盘,位于第一介电层中,第一接合焊盘包括第一导电层和位于第一导电层上的第二导电层,第一导电层包括第一晶粒,第二导电层包括第二晶粒,大部分第一晶粒不具有相同的晶格方向,大部分第二晶粒具有相同的晶格方向。半导体器件还包括第二集成电路管芯,第二集成电路管芯包括:第二介电层,利用电介质至电介质接合直接接合至第一介电层;和第二接合焊盘,位于第二介电层中,第二接合焊盘利用金属至金属接合直接接合至第一接合焊盘。

3、根据本申请的又一个实施例,提供了一种形成半导体器件的方法,包括:在介电层中图案化互连开口,介电层设置在半导体衬底的有源表面上方,互连开口具有通孔开口和位于通孔开口上方的沟槽;在互连开口中镀第一铜层,第一铜层填充通孔开口并且衬里沟槽,第一铜层具有非均匀晶粒取向;在第一铜层上镀第二铜层,第二铜层填充沟槽的剩余部分,第二铜层具有均匀晶粒取向;以及平坦化第二铜层、第一铜层和介电层,直到第二铜层的顶面与第一铜层的顶面和介电层的顶面共面。

4、本申请的实施例涉及管芯接合焊盘及其形成方法。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,所述第二铜层包括多个铜纳米柱,所述铜纳米柱的每个包括多个铜纳米板,所述铜纳米板在远离所述第一铜层延伸的垂直方向上堆叠。

3.根据权利要求2所述的半导体器件,其中,所述铜纳米柱通过垂直边界彼此分离。

4.根据权利要求2所述的半导体器件,其中,所述铜纳米板通过水平边界彼此分离。

5.根据权利要求2所述的半导体器件,其中,所述第一铜层包括第一晶粒,所述第一晶粒具有分布在整个所述第一铜层中的不规则图案,并且所述铜纳米板中的每个铜纳米板包括第二晶粒,所述第二晶粒具有分布在整个所述铜纳米板中的不规则图案。

6.根据权利要求1所述的半导体器件,其中,所述接合焊盘还包括所述第一铜层,其中,所述第二铜层设置在所述第一铜层上方。

7.一种半导体器件,包括:

8.根据权利要求7所述的半导体器件,其中,所述大部分所述第二晶粒是<111>取向的。

9.根据权利要求7所述的半导体器件,其中,所述第二接合焊盘包括第三导电层和位于所述第三导电层上的第四导电层,所述第三导电层接合至所述第一导电层,所述第四导电层接合至所述第二导电层。

10.一种形成半导体器件的方法,包括:

技术总结

在实施例中,一种器件包括:介电层,位于半导体衬底的有源表面上方;导电通孔,位于介电层中,该导电通孔包括具有非均匀晶粒取向的第一铜层;以及接合焊盘,位于导电通孔上方和介电层中,接合焊盘包括具有均匀晶粒取向的第二铜层,接合焊盘的顶面与介电层的顶面共面。根据本申请的实施例,还提供了半导体器件及其形成方法。

技术研发人员:吕文雄,郑明达,林佳莉,黄育智,陈承先

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!