一种双层侧墙结构的超结器件的制备方法及超结器件与流程

本发明涉及半导体,尤其涉及一种双层侧墙结构的超结器件的制备方法及超结器件。

背景技术:

1、功率mosfet器件作为半导体分立器件的主要开关功率器件之一,被大量的应用于模块电源中,随着技术发展对于器件耐压的提高、损耗的降低、模块电源的功率密度的提高等方面的要求愈加严格,但若一味的减少mosfet器件的损耗,容易产生严重的电磁干扰(electromagnetic interference,emi)现象。功率mosfet器件的emi问题主要是在开关过程中电流变化率di/dt、电压变化率dv/dt较大而引起的,超结mossfet器件(下文中简称为超结器件)作为新一代的功率mos,相比传统的垂直双扩散金属-氧化物半导体场效应晶体管(vdmos)器件,其具有更高的功率密度,更快的反应速度,相对应地,超结器件的emi问题也更加突出,因此对产品的应用拓扑电路设计有了更高的要求,如何在保证电源效率的同时,降低应用端的设计难度,增强超结器件自身的抗emi能力是必要的且必须引起重视的问题。

技术实现思路

1、为了解决以上技术问题,本发明提供了一种双层侧墙结构的超结器件的制备方法及超结器件。

2、本发明所解决的技术问题可以采用以下技术方案实现:

3、一种双层侧墙结构的超结器件的制备方法,包括:

4、步骤s1,提供一超结器件,所述超结器件具有一栅极多晶硅层;

5、步骤s2,于所述栅极多晶硅层的侧面形成一具有氧化层和多晶硅层的双层侧墙结构。

6、优选地,所述步骤s1具体包括:

7、步骤s11,于一衬底上形成一外延层,并于所述外延层内部形成p型柱区,所述柱区与所述外延层形成n型和p型相互交替的超结结构;

8、步骤s12,于所述柱区的上方分别形成一体区,并通过一场氧化层刻蚀形成所述超结器件的有源区;

9、步骤s13,于上述表面形成一栅氧化层和具有第一预设厚度的多晶硅层,并通过光刻工艺刻蚀形成所述栅极多晶硅层,得到所述超结器件的栅极。

10、优选地,所述步骤s11中,所述柱区采用深沟槽技术形成;或者所述柱区采用多次外延技术形成。

11、优选地,所述步骤s2具体包括:

12、步骤s21,于所述超结器件的表面形成一具有第二预设厚度的氧化层,并于所述氧化层上形成一具有一第三预设厚度的多晶硅层;·

13、步骤s22,利用侧墙工艺和无阻挡层式刻蚀工艺将表面的所述多晶硅层和所述氧化层被蚀刻掉,保留所述栅极多晶硅层侧面的所述氧化层和所述多晶硅层,形成所述双层侧墙结构。

14、优选地,所述步骤s21中,所述氧化层的厚度小于所述超结器件的栅氧化层的厚度。

15、优选地,所述步骤s22中,保留的所述氧化层的宽度与所述第二预设厚度相等;和/或

16、保留的所述多晶硅层的宽度与所述第三预设厚度相等。

17、优选地,所述步骤s2之后,还包括:

18、步骤s3,于所述体区中进行蚀刻和注入退火,形成所述源区;

19、步骤s4,于所述所述双层侧墙结构的上方淀积形成一隔离层,并进行接触孔的刻蚀、金属层的淀积;

20、步骤s5,于所述金属层的表面分别形成一钝化层,并于器件背面形成一背面金属层。

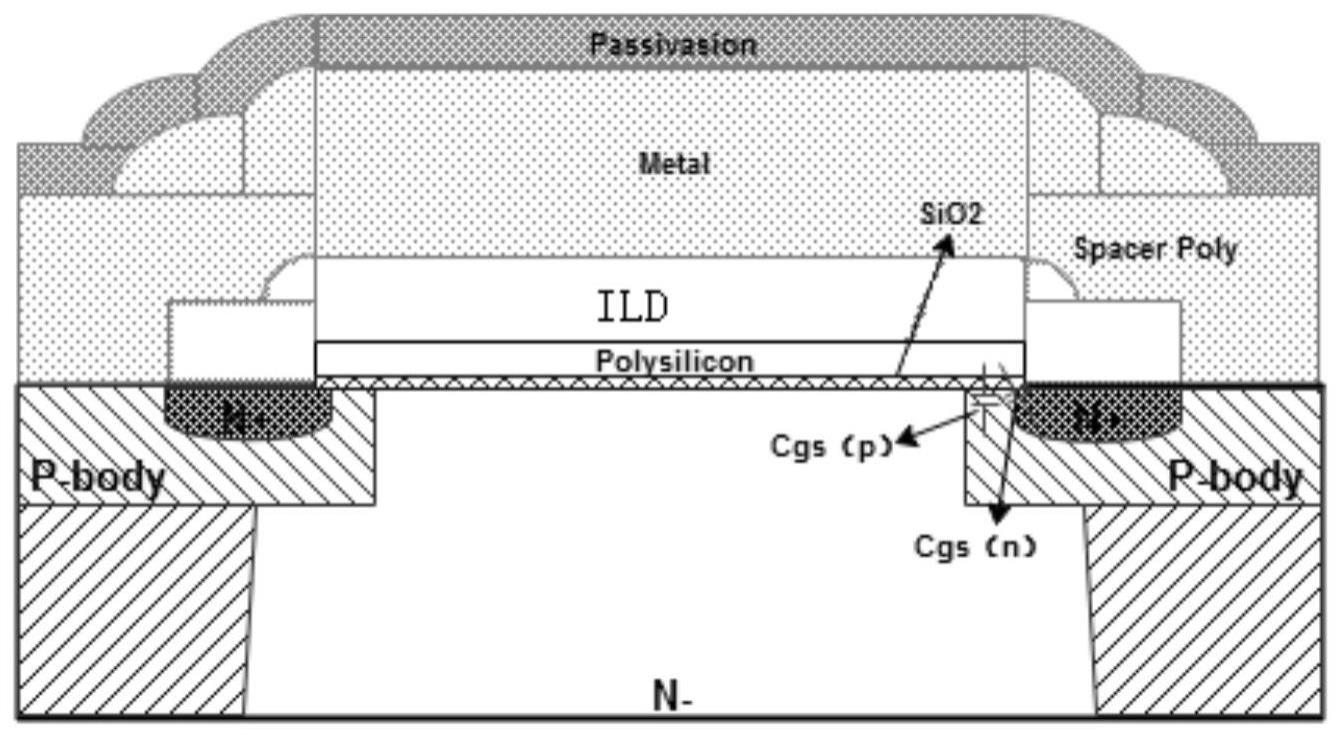

21、本发明提供一种双层侧墙结构的超结器件,采用如上述的双层侧墙结构的超结器件的制备方法制备得到,所述器件包括:

22、一超结器件,所述超结器件具有一栅极多晶硅层;

23、一双层侧墙结构,包括一具有第二预设厚度的氧化层和具有一第三预设厚度的多晶硅层,形成于所述栅极多晶硅层的侧面。

24、优选地,所述超结器件包括:

25、外延层,形成于一衬底上;

26、柱区,形成于所述外延层内,所述柱区与所述外延层形成n型和p型相互交替的超结结构;

27、体区,分别形成于所述柱区的上方;

28、栅极多晶硅层,包括栅氧化层和具有第一预设厚度的多晶硅层,所述栅极多晶硅层覆盖所述外延层表面除所述体区的区域,并部分覆盖所述体区上表面。

29、优选地,所述氧化层的宽度与所述第二预设厚度相等;和/或

30、所述多晶硅层的宽度与所述第三预设厚度相等。

31、本发明技术方案的优点或有益效果在于:

32、本发明在超结器件的栅极多晶硅层侧壁形成了一个包含有氧化层和多晶硅层的双层侧墙结构,栅极多晶硅层通过侧壁的氧化层与侧壁的多晶硅层新形成一个寄生电容csr,该寄生电容csr与原栅源电容并联,从而增大了输入电容,减小了栅极电压的振荡,有效改善了产品的抗电磁干扰能力。

技术特征:

1.一种双层侧墙结构的超结器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的双层侧墙结构的超结器件的制备方法,其特征在于,所述步骤s1具体包括:

3.根据权利要求2所述的双层侧墙结构的超结器件的制备方法,其特征在于,所述步骤s11中,所述柱区采用深沟槽技术形成;或者所述柱区采用多次外延技术形成。

4.根据权利要求1所述的双层侧墙结构的超结器件的制备方法,其特征在于,所述步骤s2具体包括:

5.根据权利要求4所述的双层侧墙结构的超结器件的制备方法,其特征在于,所述步骤s21中,所述氧化层的厚度小于所述超结器件的栅氧化层的厚度。

6.根据权利要求4所述的双层侧墙结构的超结器件的制备方法,其特征在于,所述步骤s22中,保留的所述氧化层的宽度与所述第二预设厚度相等;和/或

7.根据权利要求1所述的双层侧墙结构的超结器件的制备方法,其特征在于,所述步骤s2之后,还包括:

8.一种双层侧墙结构的超结器件,其特征在于,采用如权利要求1-7任意一项所述的双层侧墙结构的超结器件的制备方法制备得到,所述器件包括:

9.根据权利要求8所述的双层侧墙结构的超结器件,其特征在于,所述超结器件包括:

10.根据权利要求8所述的双层侧墙结构的超结器件,其特征在于,所述氧化层的宽度与所述第二预设厚度相等;和/或

技术总结

本发明提供一种双层侧墙结构的超结器件的制备方法及超结器件,属于半导体技术领域,包括:步骤S1,提供一超结器件,超结器件具有一栅极多晶硅层;步骤S2,于栅极多晶硅层的侧面形成一具有氧化层和多晶硅层的双层侧墙结构。有益效果:本发明在超结器件的栅极多晶硅层侧壁形成了一个包含有氧化层和多晶硅层的双层侧墙结构,栅极多晶硅层通过侧壁的氧化层与侧壁的多晶硅层新形成一个寄生电容Csr,该寄生电容Csr与原栅源电容并联,从而增大了输入电容,减小了栅极电压的振荡,有效改善了产品的抗电磁干扰能力。

技术研发人员:任杰,马治军,苏海伟

受保护的技术使用者:上海维安半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!