静电放电半导体器件及其制造方法、集成电路与流程

本发明涉及半导体,具体地,涉及一种静电放电半导体器件及其制造方法、集成电路。

背景技术:

1、esd(electro-static discharge,静电放电)是一种客观存在的自然现象,伴随着产品的整个周期。esd不易被人体感知,却会对集成电路产品造成严重威胁。据美国国家半导体公司(national-semiconductor)数据统计表明,现今集成电路失效产品中的38%是由esd/eos(electrical-over-stress静电过应力)所引起的。在芯片的制造、封装、测试到应用阶段,其外部环境和内部结构都会积累一定的电荷,会随时受到静电的威胁。因此,在芯片设计中需要在各个引脚放置esd防护器件。对于高压cmos或高压bcd工艺,其广泛的用于制造电源管理、高压驱动以及汽车电子等领域的集成电路产品中。这些产品的高压引脚经常会使用ldmos(laterally-diffused metal-oxide semiconductor,横向扩散金属氧化物半导体)或scr(silicon controlled rectifier,可控硅)结构作为esd防护器件。而这类集成电路产品往往工作在大电流、大电压、强电磁干扰环境下,esd防护器件会出现低鲁棒性、误触发等问题。

2、图1示出现有技术的ldmos半导体结构的截面示意图。如图1所示,以pldmos为例,其包括p型衬底101、位于衬底101上部的n型阱区103和p型掺杂漂移区102以及位于漂移区102上部的p型阱区104,在n型阱区103中形成有第一p+注入区131和第一n+注入区132,在p型阱区104中形成有第二p+注入区133,在衬底101表面形成有场氧化层111和场氧化层112,在场氧化层112上方还形成有栅氧化层121和多晶硅层122。为得到高维持电压的esd特性,将该pldmos的源、体、栅极短接作为阳极,漏端作为阴极,当esd脉冲来临时,n型阱区103和漂移区102发生雪崩击穿,寄生pnp泄放电流,但由于pnp作为esd防护器件其鲁棒性较低,若想达到较高的hbm(human body model)等级则需要较大的器件面积,目前的ldmos器件的静电防护能力较差。

技术实现思路

1、鉴于上述问题,本发明的目的在于提供一种静电放电半导体器件及其制造方法、集成电路,以解决现有技术中的问题。

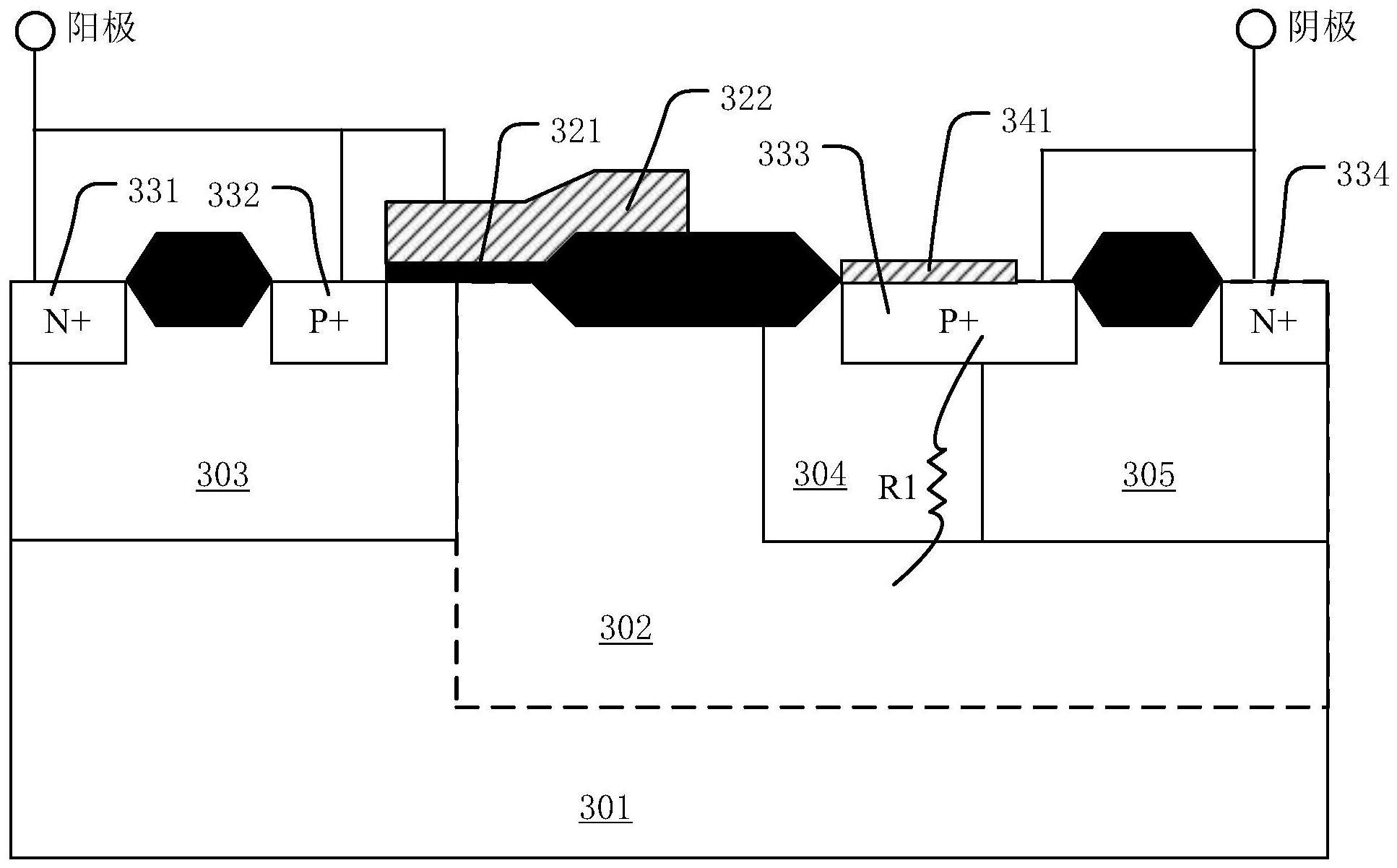

2、根据本发明的第一方面,提供一种静电放电半导体器件,包括:

3、衬底;

4、横向分布在所述衬底上部的第一n型阱区和漂移区;

5、分布在所述漂移区上部的远离所述第一n型阱区一侧的相接触的p型阱区和第二n型阱区;

6、第一n+注入区和第一p+注入区,位于所述第一n型阱区中远离所述漂移区的一侧;

7、第二p+注入区和第二n+注入区,分别位于所述p型阱区和所述第二n型阱区中;

8、多个场氧化层,位于所述衬底表面,将所述第一n+注入区、所述第一p+注入区、所述第二p+注入区和所述第二n+注入区依次隔开;

9、栅氧化层和多晶硅层,依次堆叠在所述第一n型阱区和所述漂移区之间的衬底表面上,

10、其中,所述第二p+注入区横跨所述p型阱区和所述第二n型阱区。

11、可选地,所述p型阱区和所述第二n型阱区横向相邻分布在所述漂移区内。

12、可选地,所述第二n型阱区位于所述p型阱区中远离所述第一n型阱区的一侧上部。

13、可选地,所述第一n+注入区、所述第一p+注入区和所述多晶硅层均与所述半导体器件的阳极相连接,所述第二p+注入区和所述第二n+注入区均与所述半导体器件的阴极相连接。

14、可选地,所述半导体器件在工作时,由第一p+注入区、第一n型阱区和漂移区组成的三极管结构导通以形成从阳极到阴极之间的第一电流泄放通路。

15、可选地,所述半导体器件在工作时,由第一p+注入区、第一n型阱区、漂移区、p型阱区和第二n型阱区组成的可控硅结构导通以形成从阳极到阴极之间的第二电流泄放通路。

16、可选地,所述半导体器件在接收到静电脉冲时,所述第一电流泄放通路先于所述第二电流泄放通路开启。

17、可选地,所述静电放电半导体器件还包括:硅化物阻挡层,位于所述第二p+注入区上方远离所述第二n+注入区的一侧。

18、根据本发明的第二方面,提供一种静电放电半导体器件的制造方法,包括:

19、形成衬底和位于所述衬底上部的漂移区;

20、在所述衬底表面形成多个场氧化层;

21、形成位于所述衬底上部的依次隔开的第一n型阱区、p型阱区和第二n型阱区,所述p型阱区和所述第二n型阱区位于所述漂移区内;

22、形成位于所述第一n型阱区和所述漂移区之间的衬底表面上的堆叠的栅氧化层和多晶硅层;

23、形成位于所述第一n型阱区中的第一n+注入区和第一p+注入区;以及

24、分别形成位于所述p型阱区和所述第二n型阱区中的第二p+注入区和第二n+注入区,

25、其中,所述第二p+注入区横跨所述p型阱区和所述第二n型阱区。

26、可选地,所述静电放电半导体器件的制造方法还包括:

27、在所述第二p+注入区上方远离所述第二n+注入区的一侧形成多晶硅阻挡层;以及

28、形成所述半导体器件的阳极和阴极,其中,所述阳极与所述第一n+注入区、所述第一p+注入区和所述多晶硅层相连接;所述阴极与所述第二n+注入区和所述第二p+注入区相连接。

29、根据本发明的第三方面,提供一种集成电路,包括:上述静电放电半导体器件。

30、本发明提供的静电放电半导体器件及其制造方法、集成电路,在pldmos半导体结构的基础上进行改进,在漏端增加了一个与p型阱区相接触的n型阱区和位于n型阱区中的n型注入区(n+注入区),再使漏端的p型阱区内的p+注入区同时横跨n型阱区,得到可控硅结构的半导体器件,而漏端的一系列结构改进使得在静电脉冲来临时,靠近源端的寄生pnp三极管先形成电流泄放通路,而后随电流增大,靠近漏端的寄生npn三极管也导通形成可控硅电流泄放通路,从而可以提供极高的静电保护能力,鲁棒性较高,也能提升半导体器件单位面积的电流泄放效率,同时工艺实现较为简单,易于操作;而且寄生pnp先开启可防止管脚因电压过冲或毛刺尖峰造成scr器件误触发引起的闩锁效应。

31、优选地,为加快scr结构的电流泄放,在漏端的p+注入区上方还形成有硅化物阻挡层sab(salicide block),以增加寄生三极管的寄生电阻,从而较小的电流就可以触发scr较快开启,提高静电防护能力。

技术特征:

1.一种静电放电半导体器件,包括:

2.根据权利要求1所述的静电放电半导体器件,其中,所述p型阱区和所述第二n型阱区横向相邻分布在所述漂移区内。

3.根据权利要求1所述的静电放电半导体器件,其中,所述第二n型阱区位于所述p型阱区中远离所述第一n型阱区的一侧上部。

4.根据权利要求1所述的静电放电半导体器件,其中,所述第一n+注入区、所述第一p+注入区和所述多晶硅层均与所述半导体器件的阳极相连接,所述第二p+注入区和所述第二n+注入区均与所述半导体器件的阴极相连接。

5.根据权利要求4所述的静电放电半导体器件,其中,所述半导体器件在工作时,由第一p+注入区、第一n型阱区和漂移区组成的三极管结构导通以形成从阳极到阴极之间的第一电流泄放通路。

6.根据权利要求5所述的静电放电半导体器件,其中,所述半导体器件在工作时,由第一p+注入区、第一n型阱区、漂移区、p型阱区和第二n型阱区组成的可控硅结构导通以形成从阳极到阴极之间的第二电流泄放通路。

7.根据权利要求6所述的静电放电半导体器件,其中,所述半导体器件在接收到静电脉冲时,所述第一电流泄放通路先于所述第二电流泄放通路开启。

8.根据权利要求1所述的静电放电半导体器件,还包括:硅化物阻挡层,位于所述第二p+注入区上方远离所述第二n+注入区的一侧。

9.一种静电放电半导体器件的制造方法,包括:

10.根据权利要求9所述的静电放电半导体器件的制造方法,还包括:

11.一种集成电路,包括:根据权利要求1-9任一项所述的静电放电半导体器件。

技术总结

公开了一种静电放电半导体器件及其制造方法、集成电路,静电放电半导体器件包括:衬底;横向分布在衬底上部的第一N型阱区和漂移区;分布在漂移区上部的远离第一N型阱区一侧的相接触的P型阱区和第二N型阱区;第一N+注入区和第一P+注入区,位于第一N型阱区中远离漂移区的一侧;第二P+注入区和第二N+注入区,分别位于P型阱区和第二N型阱区中;多个场氧化层,位于衬底表面,将第一N+注入区、第一P+注入区、第二P+注入区和第二N+注入区依次隔开;栅氧化层和多晶硅层,依次堆叠在衬底表面上,第二P+注入区横跨P型阱区和第二N型阱区。在静电脉冲下寄生三极管先开启,然后形成可控硅放电路径,器件的静电防护能力强,鲁棒性高。

技术研发人员:胡涛

受保护的技术使用者:杰华特微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!