多域电路中的跨域静电放电保护的制作方法

本文中所描述的主题的实施例涉及保护电子电路免于由静电放电引起的损坏的电路元件。

背景技术:

1、包括晶体管和其它电子装置的集成电路常常易受由静电放电(esd)事件引起的物理损坏。esd事件可能来源于外部来源,例如由带静电的人和机器的处置。esd事件还可由集成电路内的电荷累积产生,由带电装置模型(“cdm型”esd事件)解释。一些集成电路包括多个参考电压节点,所述多个参考电压节点彼此分离以提供多个参考域(“接地域”)。此类集成电路可包括属于不同接地域的互连电路块。此类电路块可具有对来源于属于其它接地域的电路块的cdm型esd事件的不同阻抗。

2、具有多个接地域的ic常常具有耦合到内部信号线的保护电路,所述内部信号线将一个接地域中的装置连接到另一接地域中的装置。“cdm箝位器”为被设计成耗散可能由内部信号线处的电荷累积产生的cdm型esd驱动电流的子电路。cdm箝位器常常包括串联连接在装置的输出节点(所述装置可能成为esd事件的来源)与另一装置的输入节点之间的电阻器。此类电阻器又耦合到例如晶体管或二极管等被配置成安全地耗散由cdm型esd事件驱动的电流的装置。

技术实现思路

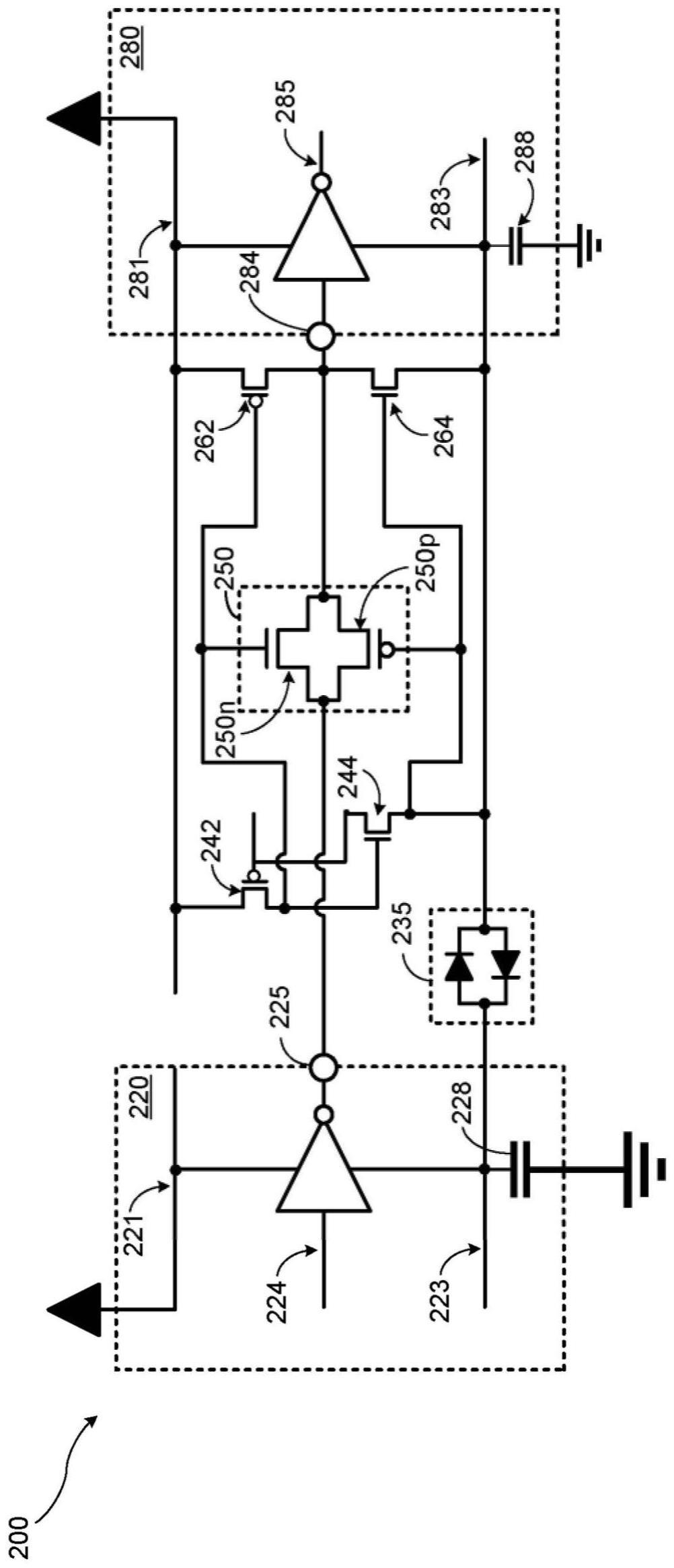

1、在示例实施例中,提供一种半导体装置。所述半导体装置包括半导体基板、形成于所述半导体基板内的第一电路块以及形成于所述半导体基板内的第二电路块。所述第一电路块具有输出节点并且包括第一电子装置,所述第一电子装置耦合到形成于所述半导体基板内的第一供电电压节点和形成于所述半导体基板内的第一参考电压节点。所述第二电路块具有耦合到所述第一电路块的所述输出节点的输入节点,并且包括第二电子装置,所述第二电子装置耦合到形成于所述半导体基板内的第二供电电压节点和形成于所述半导体基板内的与所述第一参考电压节点分离的第二参考电压节点。

2、所述装置还包括形成于所述半导体基板内的晶体管传输门,所述晶体管传输门具有第一电流端和第二电流端。所述传输门耦合在所述第一电路块的所述输出节点与所述第二电路块的所述输入节点之间。所述传输门的所述第一电流端耦合到所述第一电路块的所述输出节点,并且所述传输门的所述第二电流端耦合到所述第二电路块的所述输入节点。

3、所述传输门被配置成在所述第一电流端与所述第二电流端之间提供电阻性路径,使得当足以引起静电放电(esd)事件的电荷量累积在所述第一电路块的所述输出节点处时,所述第二电路块的所述输入节点与所述第二电路块的所述第二参考电压节点之间的电位差不超过第一预定阈值电压。

4、在另一示例实施例中,提供一种制造半导体装置的方法。所述方法包括在半导体基板内形成晶体管传输门。所述传输门具有第一电流端和第二电流端。所述方法另外包括:将所述传输门的所述第一电流端电耦合到形成于所述半导体基板内的第一电路块的输出节点;将所述传输门的所述第二电流端电耦合到形成于所述半导体基板内的第二电路块的所述输入节点。

5、所述第一电路块包括第一电子装置,所述第一电子装置耦合到形成于所述半导体基板内的第一供电电压节点和形成于所述半导体基板内的第一参考电压节点。所述第二电路块的所述输入节点经由所述传输门耦合到所述第一电路块的所述输出节点。

6、所述第二电路块包括第二电子装置,所述第二电子装置耦合到形成于所述半导体基板内的第二供电电压节点和形成于所述半导体基板内的与所述第一参考电压节点分离的第二参考电压节点。

7、所述传输门被配置成在所述第一电流端与所述第二电流端之间提供电阻性路径,使得当足以引起静电放电(esd)事件的电荷量累积在所述第一电路块的所述输出节点处时,所述第二电路块的所述输入节点与所述第二电路块的所述第二参考电压节点之间的电位差不超过第一预定阈值电压。

技术特征:

1.一种半导体装置,其特征在于,包括:

2.根据权利要求1所述的半导体装置,其特征在于,另外包括形成于所述半导体基板内并且耦合到所述第二电路块的所述输入节点的箝位装置;

3.根据权利要求2所述的半导体装置,其特征在于,

4.根据权利要求2所述的半导体装置,其特征在于,

5.根据权利要求2所述的半导体装置,其特征在于,

6.一种制造半导体装置的方法,其特征在于,所述方法包括:

7.根据权利要求6所述的方法,其特征在于,

8.根据权利要求7所述的方法,其特征在于,另外包括:

9.根据权利要求7所述的方法,其特征在于,

10.根据权利要求7所述的方法,其特征在于,

技术总结

静电放电保护电路系统包括耦合在潜在静电放电驱动电流(“ESD电流”)源之间的晶体管传输门,且电路块的输入节点被配置成在所述传输门的第一电流端与第二电流端之间提供足够电阻性电流路径,使得当足以引起ESD事件的电荷量累积在所述潜在ESD电流源处时,跨越所述传输门产生充足电压降,使得耦合到所述电路块的所述输入节点的装置被保护免于经历横越所述装置的超过预定阈值电压的电压降。

技术研发人员:吉耶兹·简·德拉德,米哈伊尔·尤里耶维奇·谢苗诺夫,尤里·弗拉基米罗维奇·阿雷莫夫,叶连娜·瓦伦丁诺夫娜·索莫娃

受保护的技术使用者:恩智浦有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!