半导体结构及其形成方法与流程

本公开是关于半导体装置,特别是关于半导体装置的互连结构。

背景技术:

1、一些电子装置,例如处理器、存储器装置或其他类型的电子装置,包括将前端制程(front end of line,feol)区域中的晶体管电性连接到后段制程(back end of line,beol)区域的中端制程(middle end of line,meol)区域。后段制程区域或端制程区域可以包括介电层和形成在介电层中的导孔插塞。导孔插塞可以包括一种或多种用于电性连接的金属。

技术实现思路

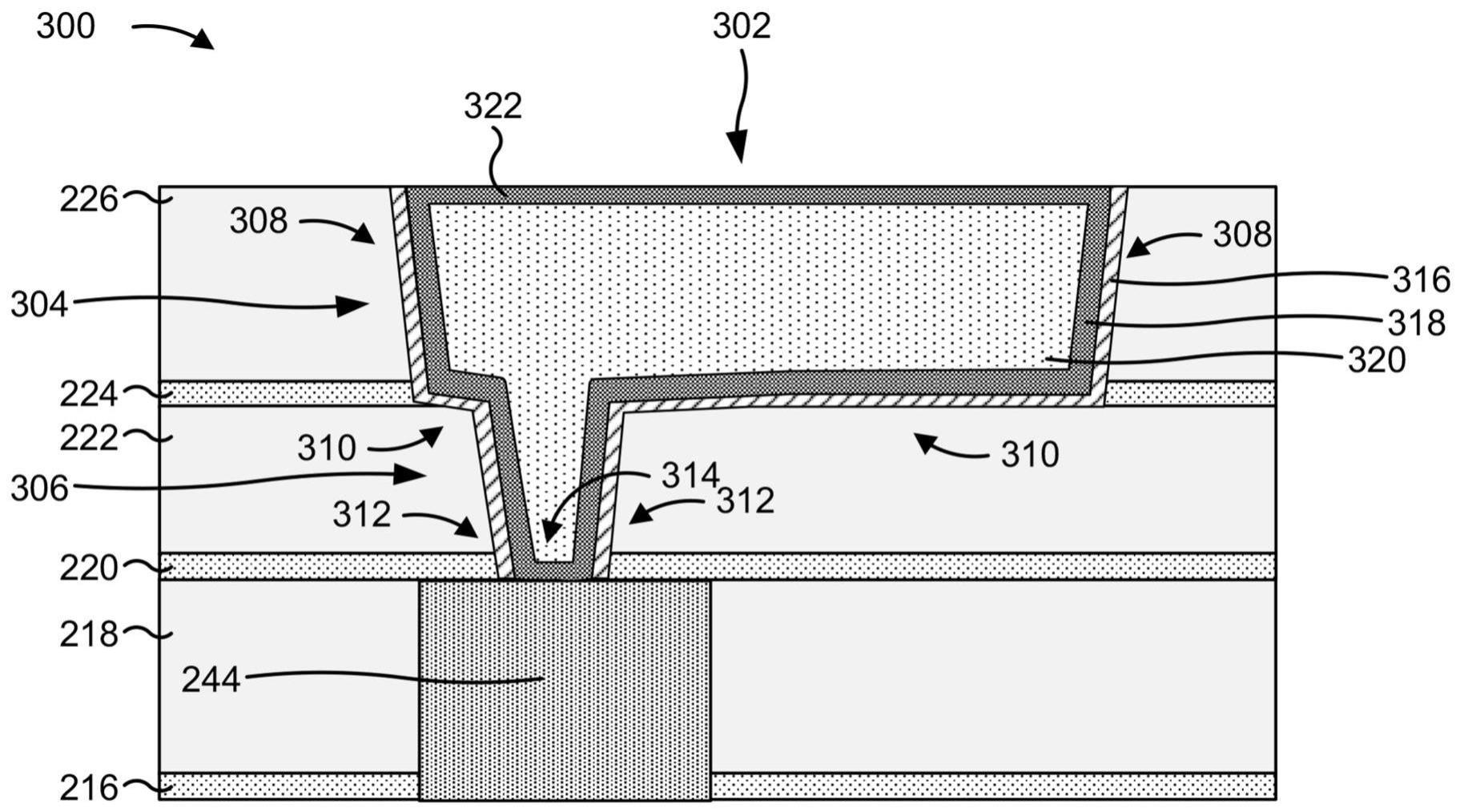

1、本案提供了一种半导体结构,包括:第一介电层;第一导电结构,位于第一介电层中;一或多层第二介电层,位于第一介电层上方以及第一导电结构上方;第二导电结构,位于一或多层第二介电层中以及第一导电结构之上;一或多层金属衬层,位于第二导电结构与一或多层第二介电层之间;以及氮化物阻障层,位于一或多层金属衬层与一或多层第二介电层之间,其中一或多层金属衬层中的至少一层金属衬层直接与第一导电结构的顶表面电性耦合,且第二导电结构通过至少一层金属衬层与第一导电结构的顶表面电性耦合,或其中第二导电结构直接与第一导电结构的顶表面电性耦合。

2、本案还提供了一种半导体结构的形成方法,包括:形成开口,开口穿过一或多层第一介电层且在第一导电结构之上,其中第一导电结构被包含在第二介电层中;在开口中的一或多层第一介电层的侧壁上形成阻障层,其中开口中的第一导电结构之上的石墨烯层减少阻障层在第一导电结构上形成的可能性;在开口中的阻障层之上形成一或多层金属衬层;以及在第一导电结构之上的开口中以及一或多层金属衬层上方形成第二导电结构。

3、本案更提供了一种半导体结构的形成方法,包括:形成开口,开口穿过一或多层第一介电层并至第一导电结构,且第一导电结构被包含在第二介电层中;对位于开口的底部的第一导电结构的顶表面执行表面处理操作;在开口的侧壁上形成石墨烯阻障层,其中表面处理操作减少石墨烯层在第一导电结构的顶表面上形成的可能性;以及在第一导电结构之上的开口中以及石墨烯层之上形成第二导电结构。

技术特征:

1.一种半导体结构,包括:

2.如权利要求1所述的半导体结构,其中该一或多层金属衬层包括:一钴(co)金属衬层,或一钌(ru)金属衬层中的至少一者。

3.如权利要求1所述的半导体结构,更包括:

4.如权利要求1所述的半导体结构,其中该至少一层金属衬层直接与该第一导电结构的该顶表面电性耦合,且该第二导电结构通过该至少一层金属衬层与该第一导电结构的该顶表面电性耦合;

5.如权利要求1所述的半导体结构,其中该至少一层金属衬层直接与该第一导电结构的该顶表面电性耦合,且该第二导电结构通过该至少一层金属衬层与该第一导电结构的该顶表面电性耦合;

6.一种半导体结构的形成方法,包括:

7.如权利要求6所述的半导体结构的形成方法,更包括:

8.如权利要求6所述的半导体结构的形成方法,更包括:

9.如权利要求6所述的半导体结构的形成方法,更包括:

10.一种半导体结构的形成方法,包括:

技术总结

半导体结构及其形成方法。半导体结构包括:第一介电层;第一导电结构,位于第一介电层中;一或多层第二介电层,位于第一介电层上方及第一导电结构上方;第二导电结构,位于第二介电层中及第一导电结构之上;一或多层金属衬层,位于第二导电结构与第二介电层之间;氮化物阻障层,位于金属衬层与第二介电层之间,金属衬层中的至少一层金属衬层直接与第一导电结构的顶表面电性耦合,第二导电结构通过至少一层金属衬层与第一导电结构的顶表面电性耦合,或第二导电结构直接与第一导电结构的该顶表面电性耦合。本文的各种后段制程膜层形成技术能够降低接触电阻、降低表面粗糙度及/或提高诸如互连及/或金属化层等后段制程膜层的半导体装置性能。

技术研发人员:金书正,纪志坚,彭馨莹,黄昭郡,李亚莲,陈冠嘉,郭家邦,刘耀闵

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!