半导体器件及其制备方法与流程

本发明涉及半导体,特别是涉及一种半导体器件及其制备方法。

背景技术:

1、随着半导体加工技术的不断发展,半导体器件由于其更小的体积、更高的性能、更高的转换效率在电子、通讯等领域得到越来越多的应用。

2、现有常规纵向双扩散金属氧化物半导体(vertical double-diffused metaloxide semiconductor,简称vdmos)器件仅在单元阵列区存在寄生二极管,故vdmos器件中二极管的面积相对较小,导致vdmos器件的抗浪涌电流能力较弱,进而导致器件的可靠性较低。

3、因此,如何提升vdmos器件的抗浪涌电流能力是亟需解决的问题。

技术实现思路

1、基于此,有必要提供一种半导体器件及其制备方法,以有效提升vdmos器件的抗浪涌电流能力。

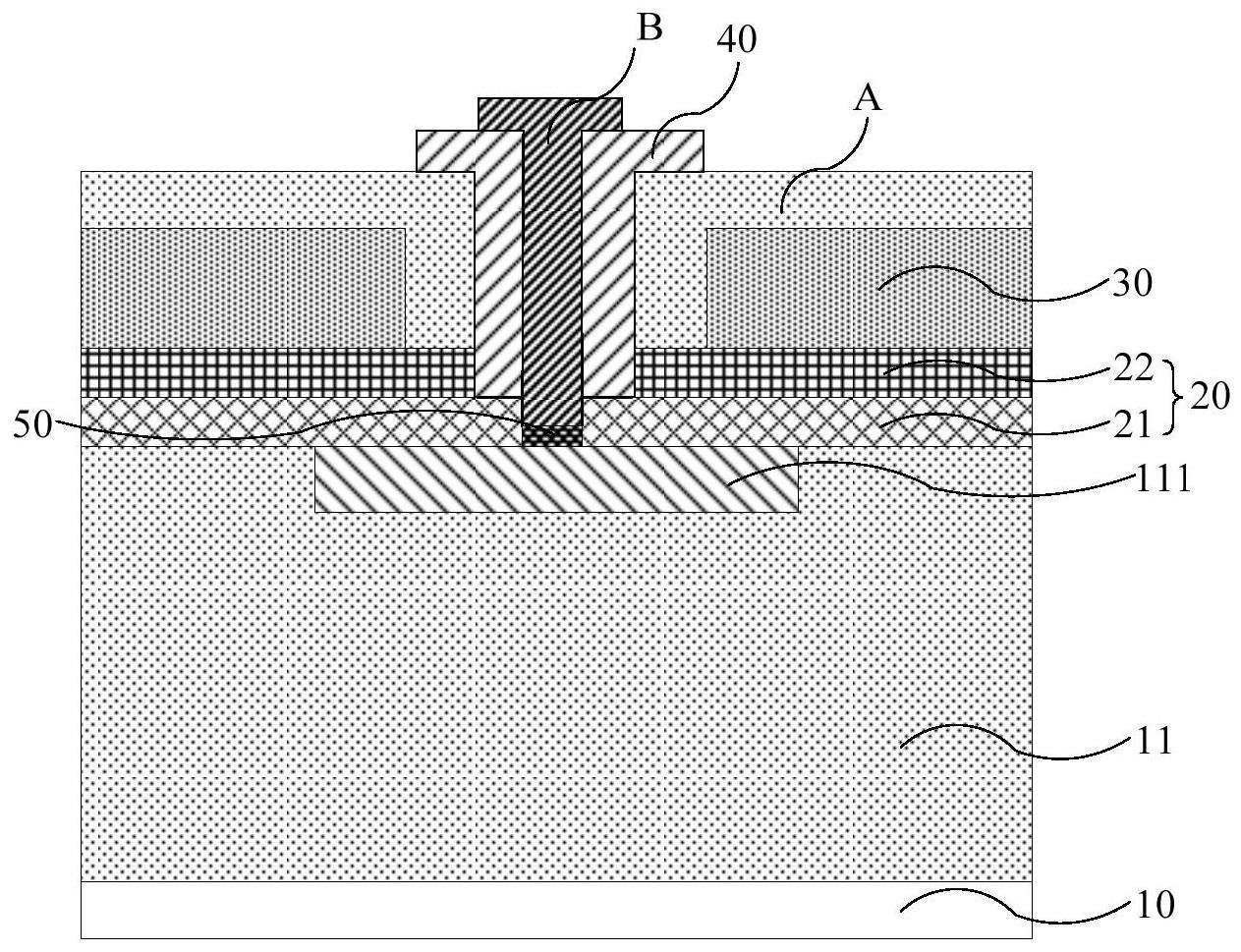

2、本申请实施例提供了一种半导体器件,包括:衬底、第一导电类型的外延层、第二导电类型的埋层、栅极结构、覆盖介质层、栅极引出电极、引出孔、源极引出电极以及隔离绝缘层。其中,第一导电类型的外延层位于衬底的表面。第二导电类型的埋层位于第一导电类型的外延层内。栅极结构位于第一导电类型的外延层远离衬底的表面。覆盖介质层覆盖栅极结构;覆盖介质层内具有开口,开口暴露出栅极结构。栅极引出电极,至少位于开口内,与栅极结构相接触;引出孔,位于开口内,沿厚度方向贯穿栅极引出电极、栅极结构,以暴露出第二导电类型的埋层;源极引出电极,位于引出孔内,与第二导电类型的埋层电连接。隔离绝缘层位于源极引出电极与栅极引出电极和栅极结构之间。

3、本申请实施例中,半导体器件采用如上结构。上述半导体器件中的引出孔贯穿栅极引出电极和栅极结构,使得源极引出电极利用引出孔与第二导电类型的埋层电连接。如此,本申请在没有增大半导体器件面积且不占用半导体器件有效面积的前提下,通过引出孔将源极引出电极与第二导电类型的埋层电连接,使得二极管集成于半导体器件必有的外延层内,从而增加了半导体器件中二极管的面积,进而提高了半导体器件的抗浪涌电流能力。因此,上述半导体器件具有较好的抗浪涌电流能力以及可靠性。

4、可选地,半导体器件还包括:金属接触层,位于引出孔的底部,且位于源极引出电极与第二导电类型的埋层之间,并与第二导电类型的埋层相接触。

5、本申请实施例中,源极引出电极与第二导电类型的埋层之间的金属接触层,有利于源极引出电极与第二导电类型的埋层形成良好的欧姆接触,进而提高二极管的电学性能。

6、可选地,开口和引出孔在第一导电类型的外延层远离衬底的表面的正投影均位于第二导电类型的埋层内。

7、可选地,栅极结构包括:栅介质层,位于第一导电类型的外延层远离衬底的表面;栅极,位于栅介质层远离第一导电类型的外延层的表面。

8、可选地,第一导电类型为n型且第二导电类型为p型;或第一导电类型为p型且第二导电类型为n型。

9、基于同样的发明构思,本申请还提供了一种半导体器件制备方法,其特征在于,包括以下步骤:提供衬底;于衬底的表面形成第一导电类型的外延层;于第一导电类型的外延层内形成第二导电类型的埋层;于第一导电类型的外延层远离衬底的表面形成栅极结构;形成覆盖介质层,覆盖介质层覆盖栅极结构;覆盖介质层内具有开口,开口暴露出栅极结构;于开口内形成栅极引出电极,栅极引出电极与栅极结构相接触;于栅极引出电极内和栅极结构内形成引出孔,引出孔暴露出第二导电类型的埋层;于引出孔的侧壁形成隔离绝缘层;于引出孔内形成源极引出电极,源极引出电极与第二导电类型的埋层电连接。

10、本申请实施例中,半导体器件采用如上方法制备。首先,于栅极引出电极内和栅极结构内形成引出孔,暴露出第二导电类型的埋层。其次,在引出孔内形成源极引出电极,以将源极引出电极与第二导电类型的埋层电连接。如此,本申请在没有增大半导体器件面积且不占用半导体器件有效面积的前提下,通过引出孔将源极引出电极与第二导电类型的埋层电连接,使得二极管集成于半导体器件必有的外延层内,从而增加了半导体器件中二极管的面积,进而提高了半导体器件的抗浪涌电流能力。因此,上述半导体器件的制备方法提高了半导体器件的抗浪涌电流能力,进而提高了半导体器件的可靠性,且没有增加额外的制备成本。

11、可选地,于第一导电类型的外延层远离衬底的表面形成栅极结构,包括:于第一导电类型的外延层远离衬底的表面形成栅介质材料层;于栅介质材料层远离第一导电类型的外延层的表面形成栅极导电层;刻蚀栅极导电层以形成栅极,并刻蚀栅介质材料层以形成栅介质层,栅介质层和栅极共同构成栅极结构。

12、可选地,形成覆盖介质层,包括:形成覆盖介质材料层,覆盖介质材料层覆盖栅极结构;刻蚀覆盖介质材料层,以形成具有开口的覆盖介质层。

13、可选地,于引出孔内形成源极引出电极之前,还包括:于引出孔的底部形成金属接触层,金属接触层与第二导电类型的埋层相接触;源极引出电极与金属接触层远离第二导电类型的埋层的表面相接触。

14、本申请实施例中,于源极引出电极与第二导电类型的埋层之间形成金属接触层,有利于源极引出电极与第二导电类型的埋层形成良好的欧姆接触,进而提高二极管的电学性能。

15、可选地,第一导电类型为n型且第二导电类型为p型;或第一导电类型为p型且第二导电类型为n型。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.如权利要求1所述的半导体器件,其特征在于,还包括:

3.如权利要求1所述的半导体器件,其特征在于,所述开口和所述引出孔在所述第一导电类型的外延层远离所述衬底的表面的正投影均位于所述第二导电类型的埋层内。

4.如权利要求1所述的半导体器件,其特征在于,所述栅极结构包括:

5.如权利要求1至4中任一项所述的半导体器件,其特征在于,所述第一导电类型为n型且所述第二导电类型为p型;或所述第一导电类型为p型且所述第二导电类型为n型。

6.一种半导体器件制备方法,其特征在于,包括以下步骤:

7.如权利要求6所述的半导体器件制备方法,其特征在于,所述于所述第一导电类型的外延层远离所述衬底的表面形成栅极结构,包括:

8.如权利要求6所述的半导体器件制备方法,其特征在于,所述形成覆盖介质层,包括:

9.如权利要求6所述的半导体器件制备方法,其特征在于,所述于所述引出孔内形成源极引出电极之前,还包括:

10.如权利要求6至9中任一项所述的半导体器件制备方法,其特征在于,所述第一导电类型为n型且所述第二导电类型为p型;或所述第一导电类型为p型且所述第二导电类型为n型。

技术总结

本申请涉及一种半导体器件及其制备方法。所述半导体器件,包括:衬底、第一导电类型的外延层、第二导电类型的埋层、栅极结构、覆盖介质层、栅极引出电极、引出孔、源极引出电极以及隔离绝缘层。其中,覆盖介质层覆盖栅极结构;覆盖介质层内具有开口,开口暴露出栅极结构。栅极引出电极至少位于开口内,与栅极结构相接触。引出孔位于开口内,沿厚度方向贯穿栅极引出电极、栅极结构,以暴露出第二导电类型的埋层。源极引出电极,位于引出孔内,与第二导电类型的埋层电连接。隔离绝缘层位于源极引出电极与栅极引出电极和栅极结构之间。上述半导体器件具有较好的抗浪涌电流能力以及可靠性。

技术研发人员:魏峰,相奇

受保护的技术使用者:广东芯粤能半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!