半导体装置及其制造方法与流程

本公开涉及一种半导体装置,并且更具体地,涉及一种包括场效应晶体管(fet)的半导体装置及其制造方法。

背景技术:

1、随着集成电路装置的尺寸减小,基底上的fet的集成程度逐渐增加,因此,正在开发纳米片(ns)-fet,ns-fet包括堆叠在同一布图区域上的多个纳米片。随着半导体装置的集成程度增加及半导体装置的尺寸减小,制造ns-fet的工艺中的工艺缺陷正在增加。因此,需要一种能够使工艺缺陷最小化并改善ns-fet的性能和可以靠性的结构。

技术实现思路

1、被提供的是一种具有最小化的缺陷及改善的性能和可以靠性的半导体装置及其制造方法。

2、另外,由实施例实现的技术目标不限于上述技术目标,并且本领域普通技术人员可以从以下描述中清楚地理解其他技术目标。

3、附加的方面将在下面的描述中被部分地阐述,并且部分地,将从该描述中明显,或者可以通过实践所呈现的实施例来习得。

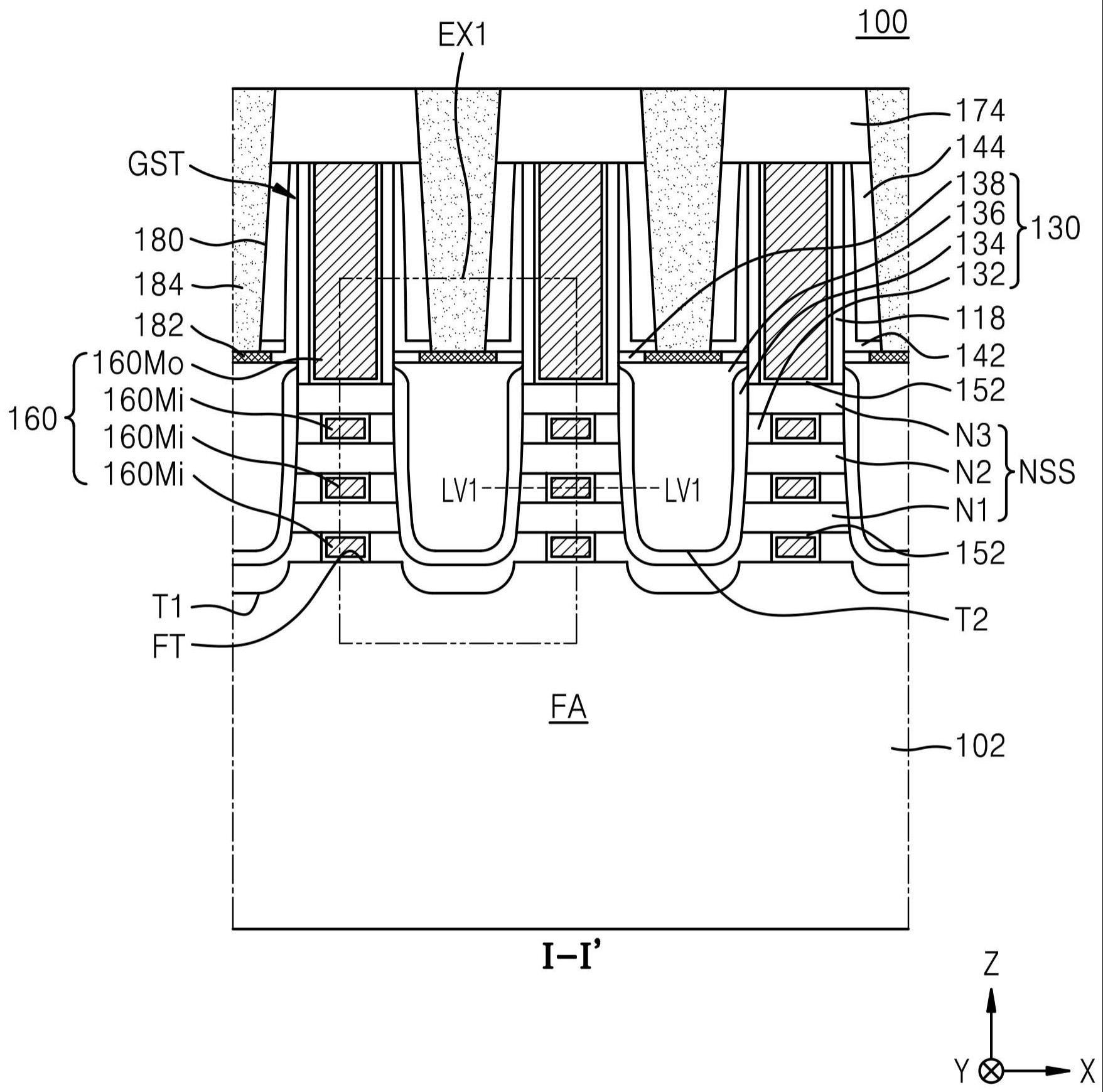

4、根据本公开的一个方面,一种半导体装置包括:鳍状有源区域,具有从基底突起并在第一方向上延伸的结构;器件隔离层,覆盖所述基底上的所述鳍状有源区域的两个侧壁;栅极结构,在所述鳍状有源区域和所述器件隔离层上在第二方向上延伸,其中,所述第二方向与所述第一方向相交;纳米片结构,包括多个纳米片,所述多个纳米片在竖直方向上从所述鳍状有源区域的顶表面彼此间隔开;以及源极/漏极区域,设置在所述鳍状有源区域上并与所述栅极结构相邻,其中,所述源极/漏极区域中的每个源极/漏极区域包括顺序地堆叠的缓冲层、内部杂质层和中心杂质层,其中,所述缓冲层填充两个竖直相邻的纳米片之间的第一凹进和所述鳍状有源区域的所述顶表面与纳米片之间的第二凹进,并且其中,所述多个纳米片接触所述内部杂质层的侧表面。

5、根据本公开的一个方面,一种半导体装置包括:鳍状有源区域,在第一方向上延伸;栅极结构,在垂直于所述第一方向的第二方向上跨所述鳍状有源区域而延伸;纳米片结构,包括多个纳米片,所述多个纳米片在竖直方向上从所述鳍状有源区域的顶表面彼此间隔开;以及源极/漏极区域,设置在所述栅极结构的两侧上的所述鳍状有源区域上,其中,所述源极/漏极区域包括顺序地堆叠的缓冲层、内部杂质层和中心杂质层,其中,所述缓冲层包括在所述第一方向上延伸并且在所述竖直方向上彼此间隔开的多个突起,其中,所述多个纳米片中的每个的端部部分夹在两个竖直相邻的突起之间或夹在所述栅极结构的间隔件与突起之间,并且其中,所述端部部分接触所述内部杂质层。

6、根据本公开的一个方面,一种半导体装置包括:鳍状有源区域,具有从基底突起并在第一方向上延伸的结构;器件隔离层,覆盖所述基底上的所述鳍状有源区域的两个侧壁;栅极结构,在所述鳍状有源区域和所述器件隔离层上在第二方向上延伸,其中,所述第二方向与所述第一方向相交;纳米片结构,包括多个纳米片,所述多个纳米片在竖直方向上从所述鳍状有源区域的顶表面彼此间隔开;以及源极/漏极区域,设置在所述鳍状有源区域上并且与所述栅极结构相邻,其中,所述源极/漏极区域包括顺序堆叠的缓冲层、内部杂质层和中心杂质层,其中,所述缓冲层包括在所述第一方向上延伸并且在所述竖直方向上彼此间隔开的多个第一突起,所述多个纳米片中的每个纳米片在栅极全包围(gaa)结构中被所述栅极结构的金属栅极包围,其中,所述每个纳米片的端部部分夹在两个竖直相邻的第一突起之间,或者夹在所述栅极结构的间隔件与第一突起之间,并且其中,所述端部部分接触所述内部杂质层。

7、根据本公开的一个方面,一种制造半导体装置的方法包括:通过在基底上交替地堆叠牺牲半导体层和纳米片半导体层来形成堆叠结构;通过蚀刻所述堆叠结构和所述基底的部分,形成在第一方向上延伸的鳍状有源区域和位于所述鳍状有源区域上的堆叠图案结构;形成覆盖所述鳍状有源区域的两个侧壁的器件隔离层;在所述堆叠图案结构和所述器件隔离层上形成在第二方向上延伸的虚设栅极结构,其中,所述第二方向与所述第一方向相交;通过使用所述虚设栅极结构作为蚀刻掩模蚀刻所述堆叠图案结构来暴露所述鳍状有源区域的顶表面,并且形成将所述堆叠图案结构划分成多个纳米片结构的沟槽;通过在所述沟槽中生长外延层来形成源极/漏极区域;去除所述虚设栅极结构的多晶硅和所述堆叠图案结构的牺牲半导体层;以及通过用金属填充被去除的部分来形成栅极结构,其中,所述多个纳米片结构中的每个纳米片结构包括多个纳米片,所述多个纳米片包括纳米片半导体层并且在竖直方向上从所述鳍状有源区域的顶表面彼此间隔开,其中,形成所述源极/漏极区域的步骤包括在所述沟槽中顺序地形成缓冲层、内部杂质层和中心杂质层,其中,所述缓冲层延伸到两个竖直相邻的纳米片之间的第一凹进中以及所述鳍状有源区域的所述顶表面与纳米片之间的第二凹进中,并且其中,所述多个纳米片接触所述内部杂质层。

8、根据本公开的一个方面,一种半导体装置包括:鳍状有源区域,从基底突起并且在第一水平方向上延伸;栅极结构,在所述鳍状有源区域上在第二水平方向上延伸,其中,所述第二水平方向与所述第一水平方向相交;第一纳米片,在竖直方向上与所述鳍状有源区域间隔开;第二纳米片,在所述竖直方向上与所述第一纳米片间隔开;以及源极/漏极区域,设置在所述鳍状有源区域上并与所述栅极结构相邻,并且包括缓冲层和内部杂质层,其中,所述缓冲层填充所述鳍状有源区域与所述第一纳米片之间的第一凹进以及所述第一纳米片与所述第二纳米片之间的第二凹进,并且其中,所述第一纳米片和所述第二纳米片接触所述内部杂质层的侧表面。

技术特征:

1.一种半导体装置,所述半导体装置包括:

2.根据权利要求1所述的半导体装置,其中,所述栅极结构的内金属栅极设置在所述两个竖直相邻的纳米片之间以及所述鳍状有源区域的所述顶表面与所述纳米片之间,

3.根据权利要求1所述的半导体装置,其中,所述内部杂质层包括围绕所述中心杂质层的底表面的底部部分和围绕所述中心杂质层的侧表面的侧部部分,并且

4.根据权利要求1所述的半导体装置,其中,所述缓冲层包括未掺杂的si或si1-xgex,其中x<0.1,

5.根据权利要求1所述的半导体装置,其中,所述缓冲层包括接触所述鳍状有源区域的所述顶表面的底部部分,

6.根据权利要求1所述的半导体装置,其中,所述源极/漏极区域还包括:外部杂质层,设置在所述缓冲层与所述内部杂质层之间并且围绕所述内部杂质层,并且

7.根据权利要求1所述的半导体装置,其中,所述栅极结构的内金属栅极设置在所述两个竖直相邻的纳米片之间以及所述鳍状有源区域的所述顶表面与所述纳米片之间,

8.根据权利要求1所述的半导体装置,其中,所述内部杂质层包括围绕所述中心杂质层的底表面的底部部分和围绕所述中心杂质层的侧表面的侧部部分,

9.根据权利要求1所述的半导体装置,其中,所述栅极结构的外金属栅极的最外表面与所述源极/漏极区域的最外表面之间在所述第一方向上的接近度小于或等于10纳米。

10.根据权利要求1所述的半导体装置,其中,在所述竖直方向上,所述中心杂质层的顶表面位于距所述纳米片结构的最上面的纳米片的顶表面-2nm至5nm范围内的位置处。

11.一种半导体装置,所述半导体装置包括:

12.根据权利要求11所述的半导体装置,其中,所述栅极结构的内金属栅极设置在两个竖直相邻的纳米片之间以及所述鳍状有源区域的所述顶表面与纳米片之间,

13.根据权利要求11所述的半导体装置,其中,所述源极/漏极区域还包括设置在所述缓冲层与所述内部杂质层之间并且围绕所述内部杂质层的外部杂质层。

14.根据权利要求13所述的半导体装置,其中,所述缓冲层包括未掺杂的si或si1-xgex(x<0.1),

15.一种制造半导体装置的方法,所述方法包括:

16.根据权利要求15所述的方法,其中,形成所述源极/漏极区域的步骤包括:

17.根据权利要求16所述的方法,所述方法还包括:

18.根据权利要求16所述的方法,其中,在形成所述第二外延层之前所述方法还包括:

19.一种半导体装置,所述半导体装置包括:

20.根据权利要求19所述的半导体装置,其中,所述栅极结构的第一内金属栅极设置在所述鳍状有源区域与所述第一纳米片之间,

技术总结

提供了半导体装置及其制造方法。该半导体装置包括:鳍状有源区域;器件隔离层,覆盖位于基底上的鳍状有源区域的两个侧壁;栅极结构;纳米片结构,包括多个纳米片;以及源极/漏极区域,设置在鳍状有源区域上并且与栅极结构相邻,其中,源极/漏极区域中的每个源极/漏极区域包括顺序堆叠的缓冲层、内部杂质层和中心杂质层,其中,缓冲层填充两个竖直相邻的纳米片之间的第一凹进和鳍状有源区域的顶表面与纳米片之间的第二凹进,并且其中,所述多个纳米片接触内部杂质层的侧表面。

技术研发人员:金奇奂,金镜浩,文康薰,李峭蒑,全龙昱

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!